# Please do not upload this copyright pdf document to any other website. Breach of copyright may result in a criminal conviction.

This Acrobat document was generated by me, Colin Hinson, from a document held by me. I requested permission to publish this from Texas Instruments (twice) but received no reply. It is presented here (for free) and this pdf version of the document is my copyright in much the same way as a photograph would be. If you believe the document to be under other copyright, please contact me.

The document should have been downloaded from my website <u>https://blunham.com/Radar</u>, or any mirror site named on that site. If you downloaded it from elsewhere, please let me know (particularly if you were charged for it). You can contact me via my Genuki email page: <u>https://www.genuki.org.uk/big/eng/YKS/various?recipient=colin</u>

You may not copy the file for onward transmission of the data nor attempt to make monetary gain by the use of these files. If you want someone else to have a copy of the file, point them at the website. (<u>https://blunham.com/Radar</u>). Please do not point them at the file itself as it may move or the site may be updated.

It should be noted that most of the pages are identifiable as having been processed by me.

I put a lot of time into producing these files which is why you are met with this page when you open the file.

In order to generate this file, I need to scan the pages, split the double pages and remove any edge marks such as punch holes, clean up the pages, set the relevant pages to be all the same size and alignment. I then run Omnipage (OCR) to generate the searchable text and then generate the pdf file.

Hopefully after all that, I end up with a presentable file. If you find missing pages, pages in the wrong order, anything else wrong with the file or simply want to make a comment, please drop me a line (see above).

It is my hope that you find the file of use to you personally – I know that I would have liked to have found some of these files years ago – they would have saved me a lot of time !

Colin Hinson

In the village of Blunham, Bedfordshire.

TI 99/4 HOME COMPUTER SERVICING MANUAL

> COMPILED AND EDITED BY JON STANFORD

FIRST REVISION, NOVEMBER, 1982

TI 99/4 HOME COMPUTER SERVICING MANUAL

> COMPILED AND EDITED BY JON STANFORD

FIRST REVISION, NOVEMBER, 1982

## TABLE OF CONTENTS

# PAGE #

| Introduction                                                                                                                                                                                                                                                                                                                                                                                | 01                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| System Block Diagram                                                                                                                                                                                                                                                                                                                                                                        | 02                                                  |

| Arch /tectural Features                                                                                                                                                                                                                                                                                                                                                                     | 03                                                  |

| TMS 9918 VDP.<br>TMC 0430 Graphics ROM<br>TIM 9919 Sound Generator                                                                                                                                                                                                                                                                                                                          | 04<br>05<br>06                                      |

| System Power Up                                                                                                                                                                                                                                                                                                                                                                             | 07                                                  |

| Debug Check List                                                                                                                                                                                                                                                                                                                                                                            | 08                                                  |

| Cassețte Interface                                                                                                                                                                                                                                                                                                                                                                          | 09                                                  |

| General Description                                                                                                                                                                                                                                                                                                                                                                         | 10                                                  |

| Oscillator Circuit<br>CPU<br>Memory Selection Logic<br>Memory Map<br>ROM and RAM Memory<br>16 To 8 Bit Interfacing Circuit<br>Graphic Read Only Memory (GROM)<br>TMS 9901 Programmable System Interface<br>Video Display Processor<br>Sound Generation Controller<br>Keyboard & Remote Handheld Control Unit Interfacing<br>Cassette Interfacing Circuitry<br>I/O Bus<br>Power Supply Board | 13<br>34<br>37<br>98<br>45<br>47<br>78<br>914<br>88 |

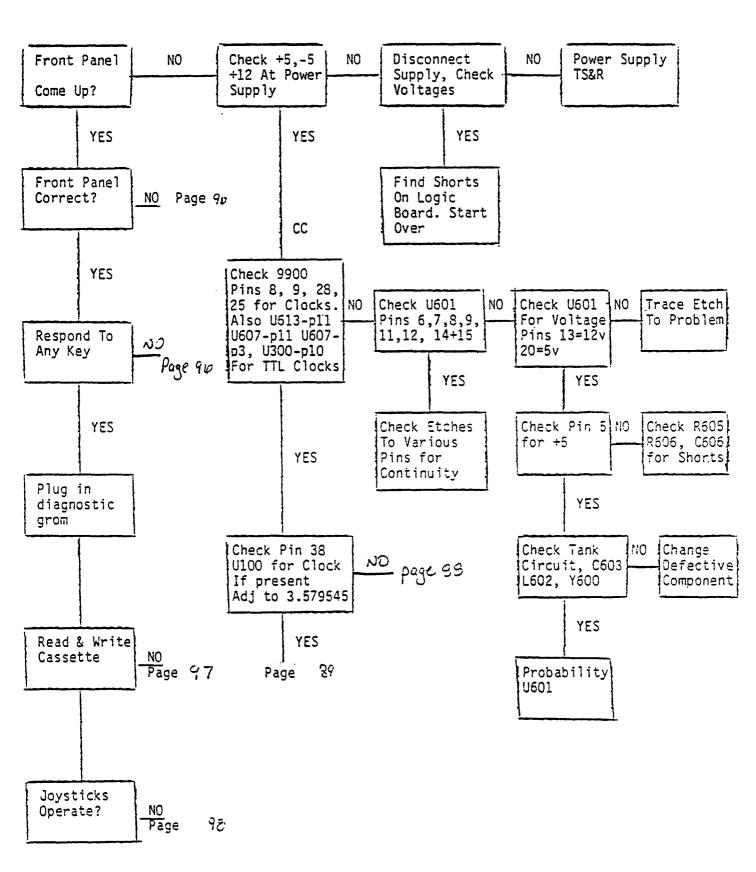

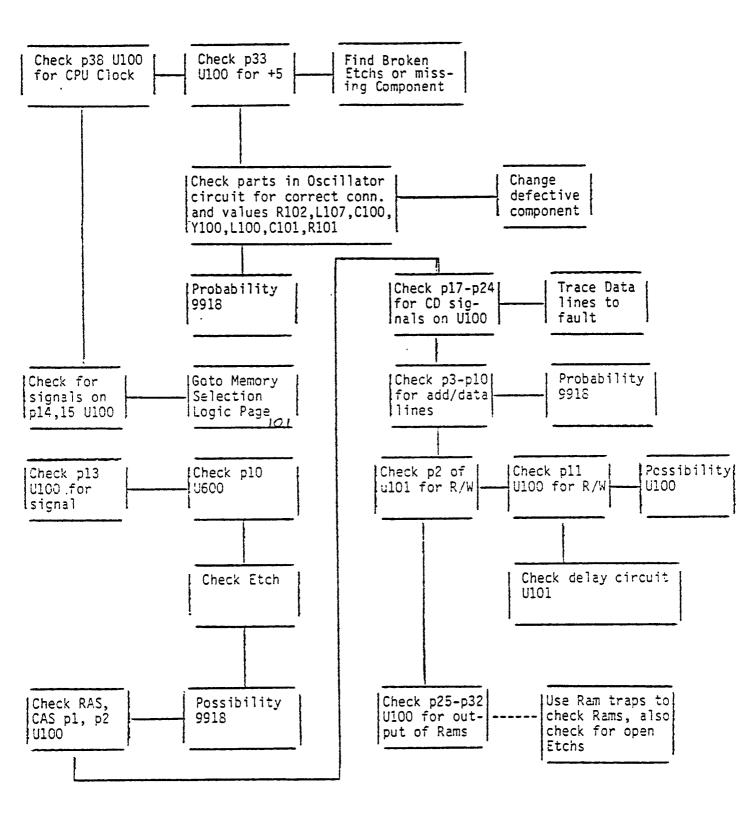

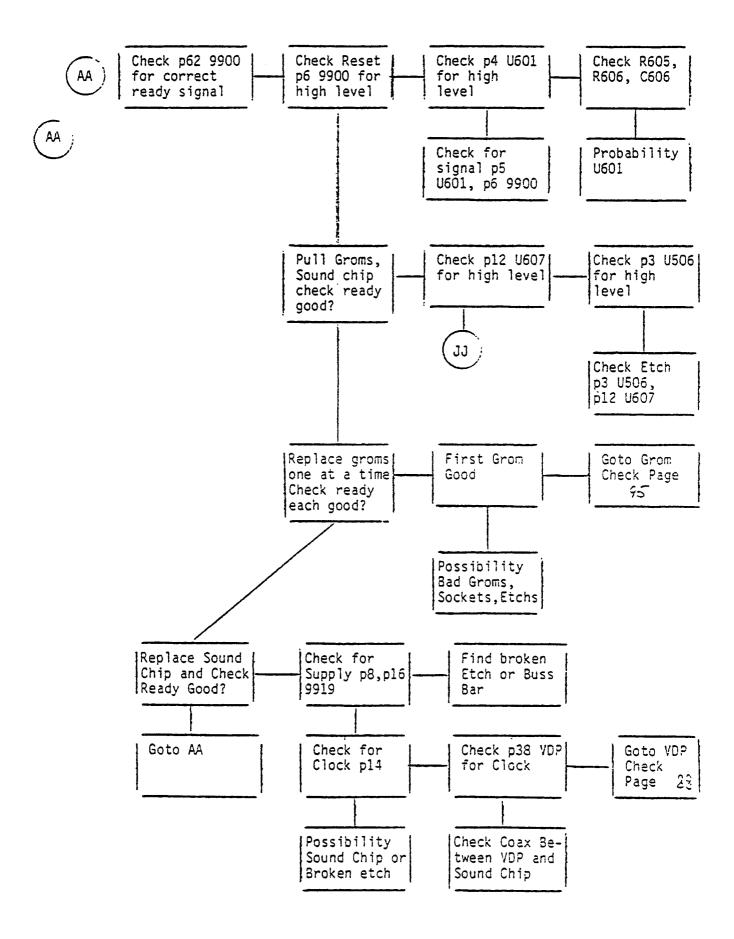

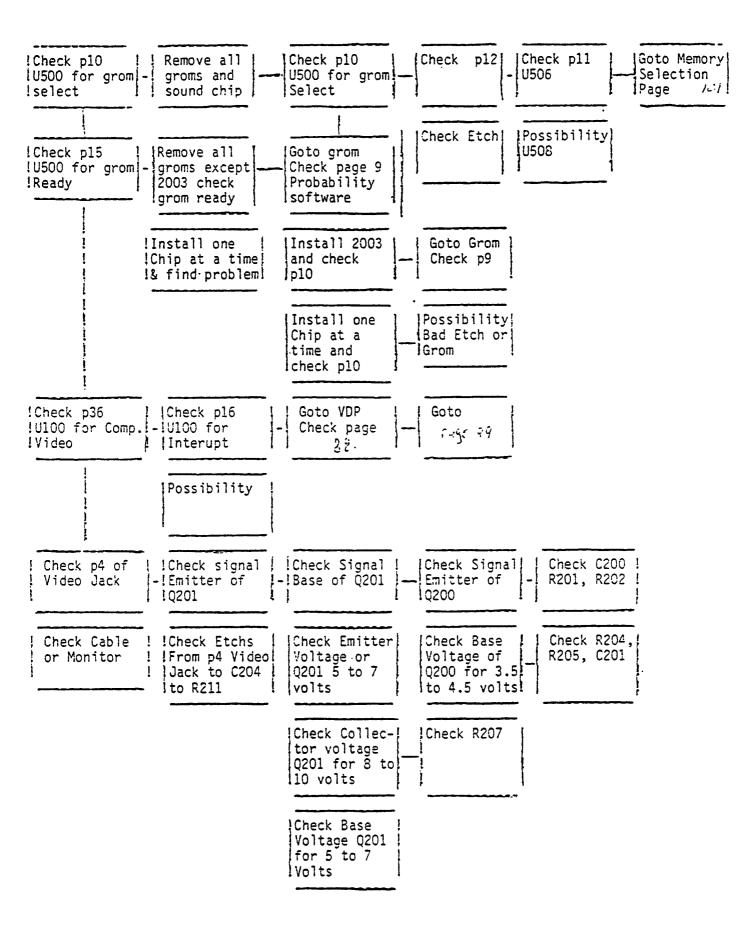

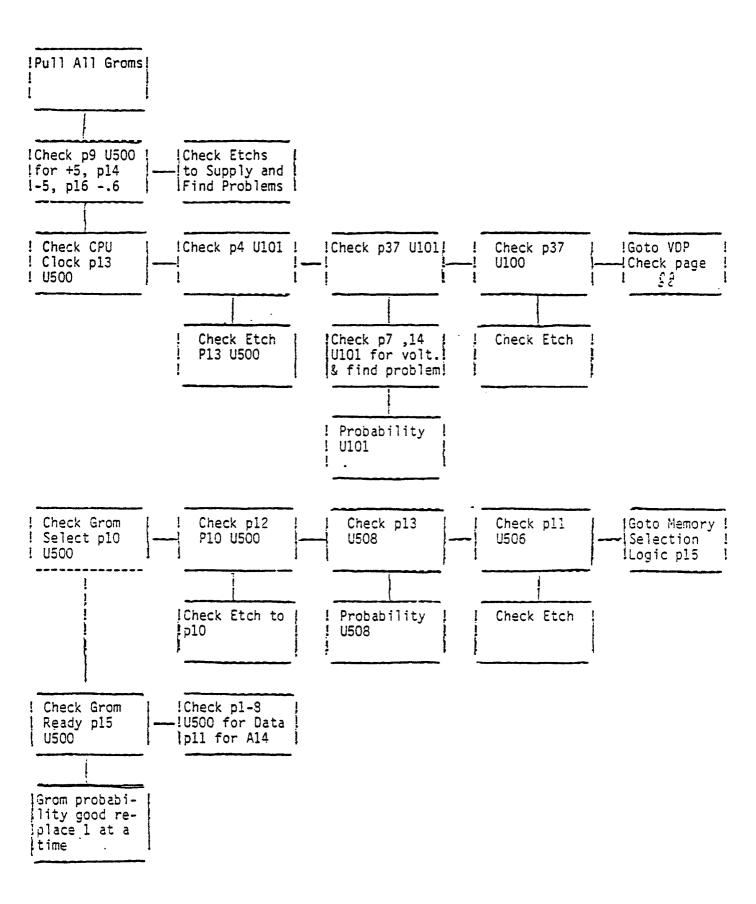

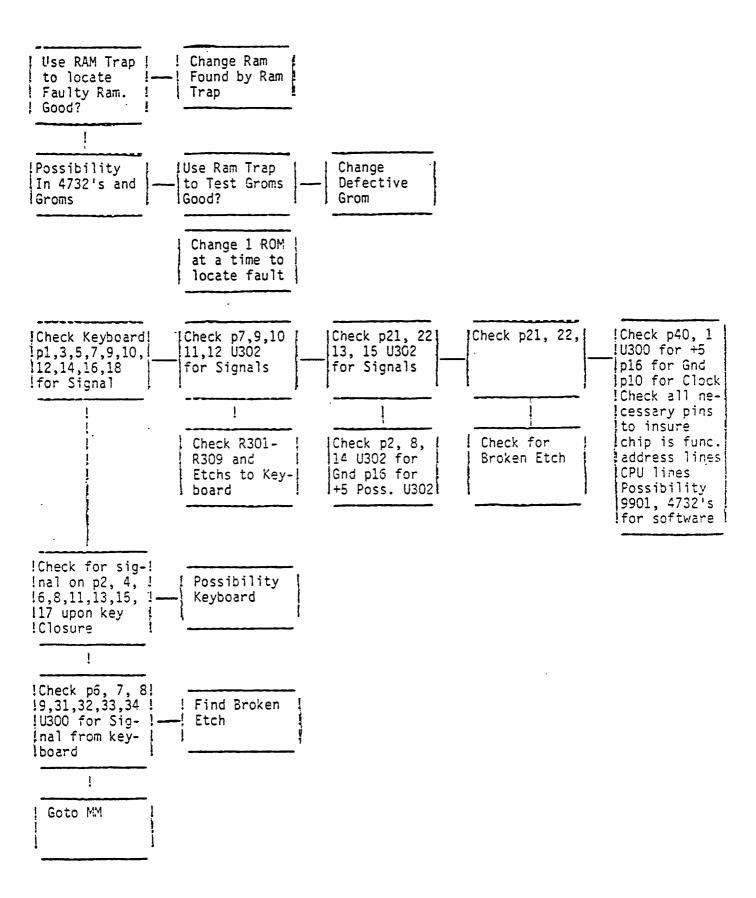

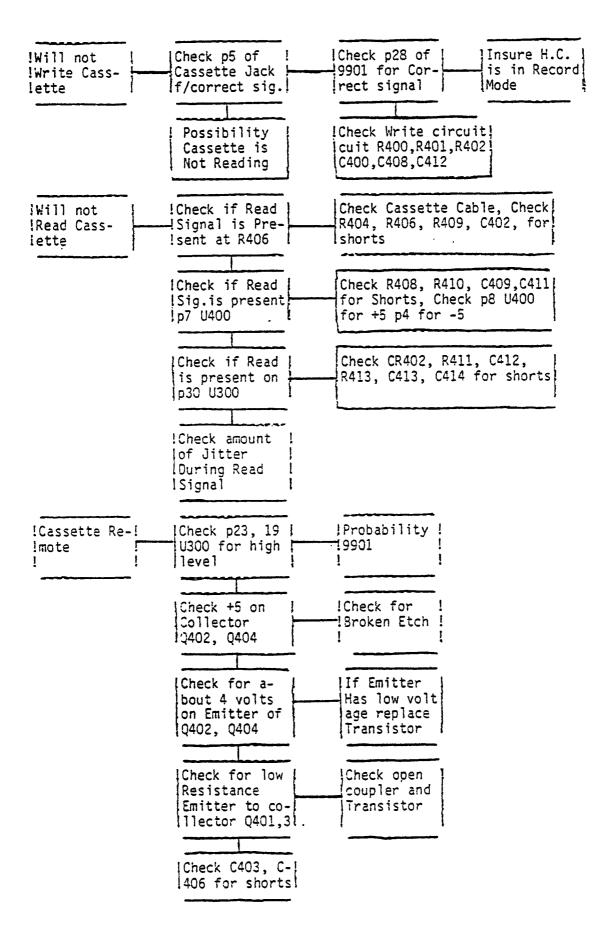

| Trouble Shooting Guide                                                                                                                                                                                                                                                                                                                                                                      | 86                                                  |

| I/O Port Connector                                                                                                                                                                                                                                                                                                                                                                          | 104                                                 |

| GROM Port Connector                                                                                                                                                                                                                                                                                                                                                                         | 105                                                 |

| Cassette I/O Port                                                                                                                                                                                                                                                                                                                                                                           | 10ộ                                                 |

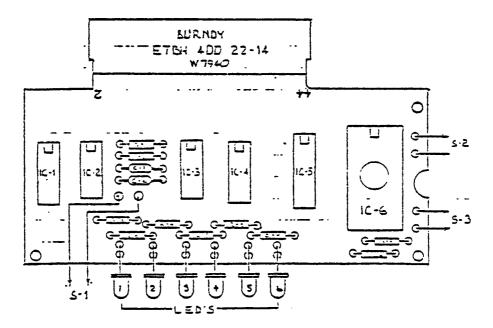

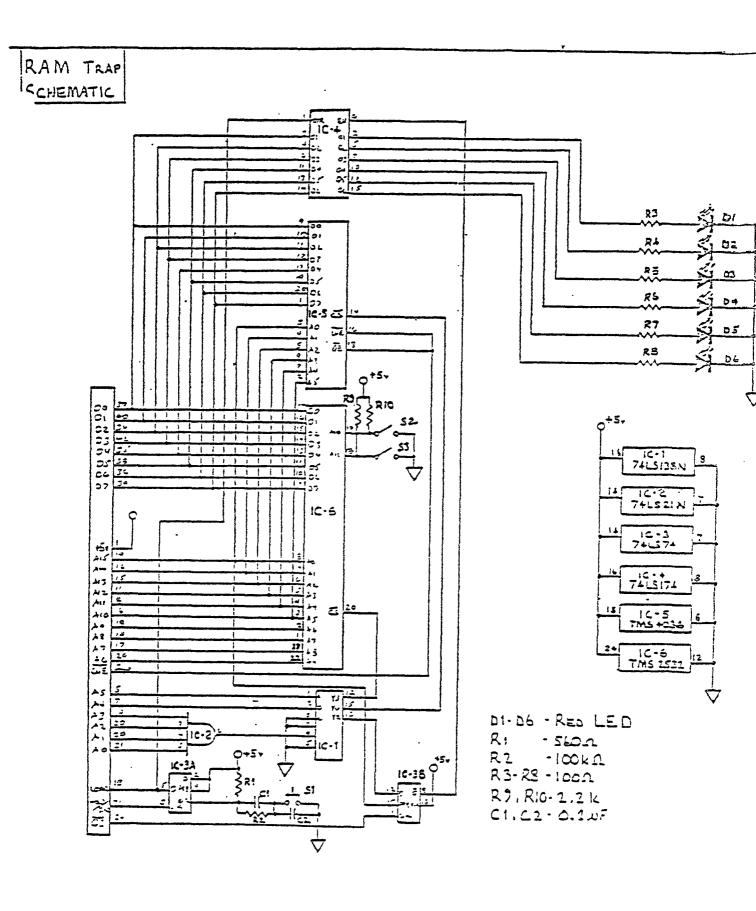

| RAM Trap                                                                                                                                                                                                                                                                                                                                                                                    | 107                                                 |

## LIST OF FIGURES

# Figure #

## DESCRIPTION

| 01<br>02 | System Block Diagram                                   |

|----------|--------------------------------------------------------|

| 03       | TMS 9900 Archetecture 20                               |

| 04       | TMS 9900 Pin Assignments And Functions 21              |

| 05       | Memory Read Cycle Timing 25                            |

| 06       | Memory Write Cycle Timing                              |

| 07       | Memory Read Cycle Timing With One Wait State 27        |

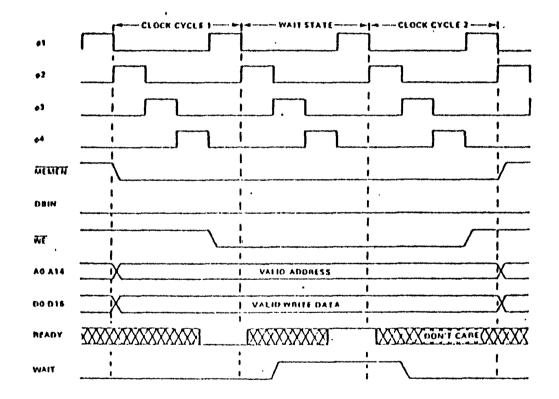

| 08       | Memory Write Cycle Timing With One Wait State 28       |

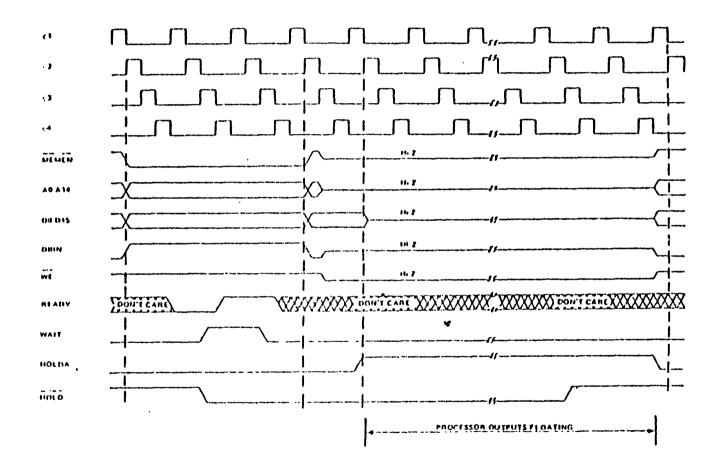

| 09       | Direct Memory Access Timing 29                         |

| 10<br>11 | CRU Interface Timing                                   |

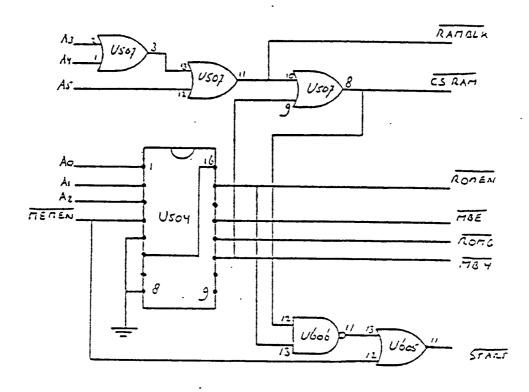

| 12       | Memory Selection Logic                                 |

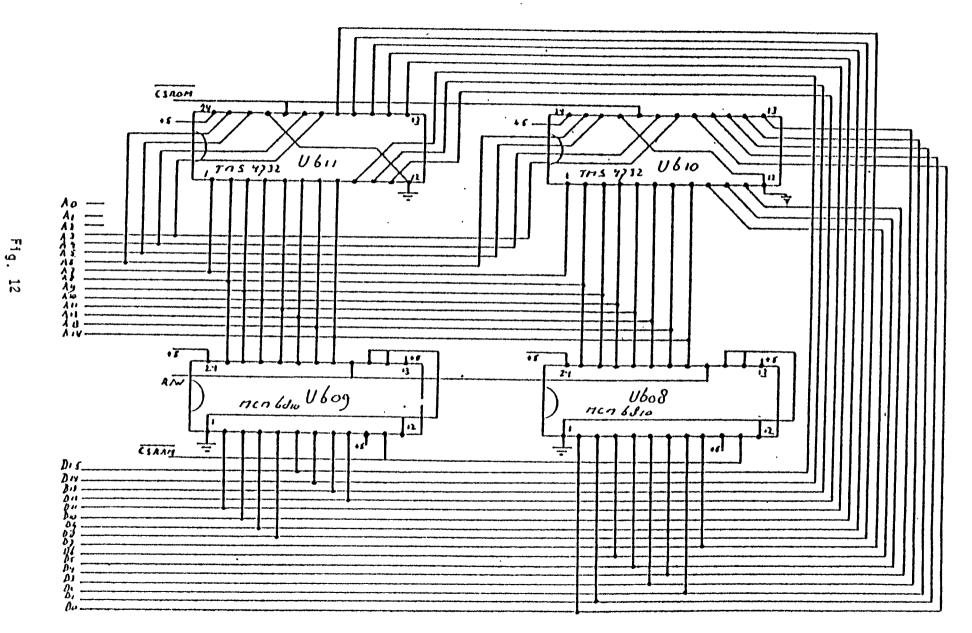

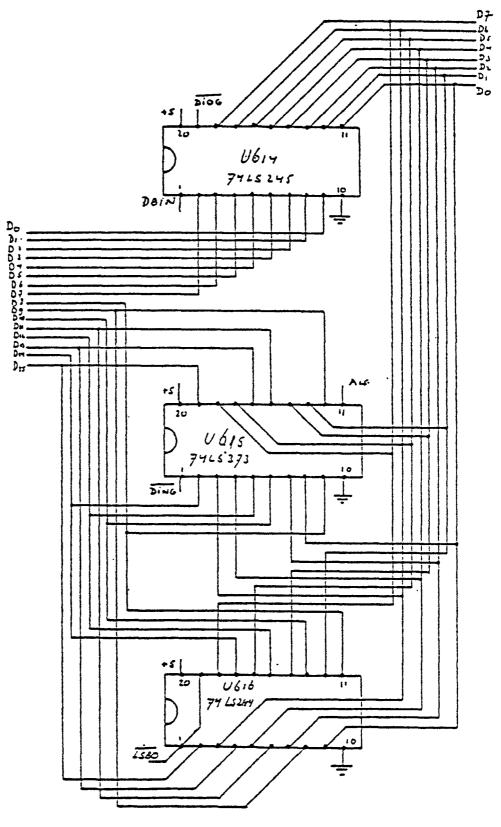

| 12       | ROM And RAM Memory3816 To 8 Bit Multiplexing Circuit41 |

| 13       |                                                        |

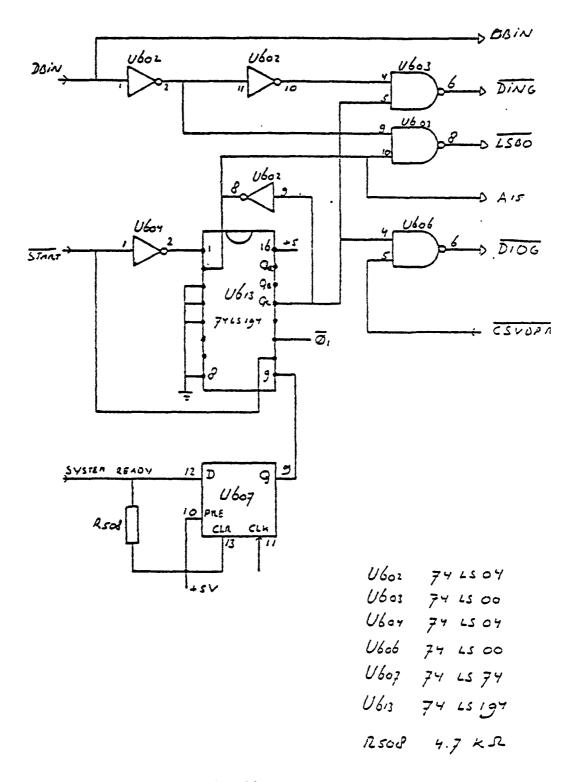

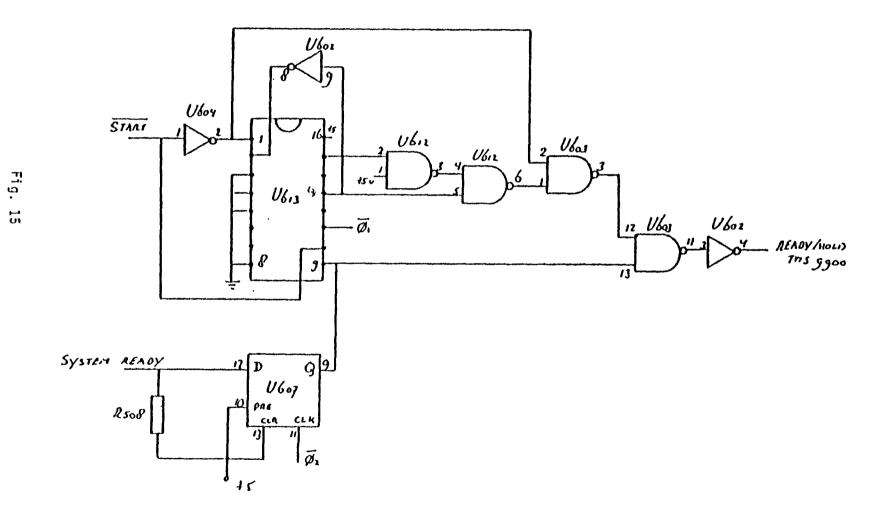

| 15       | Control Signal Generation                              |

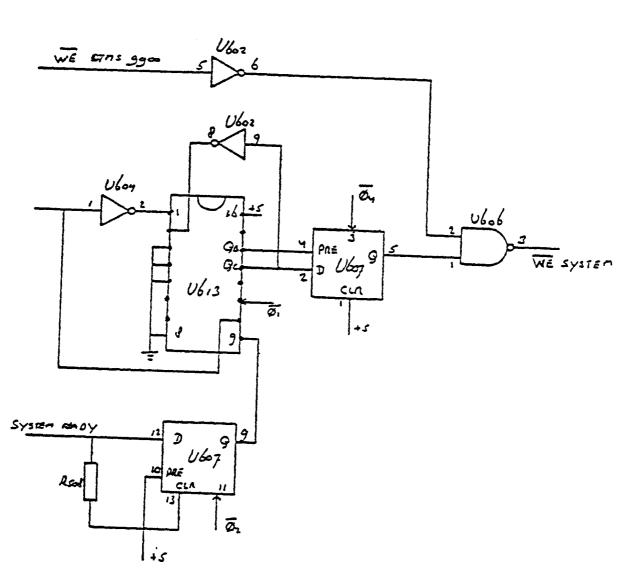

| 16       | WE Generation                                          |

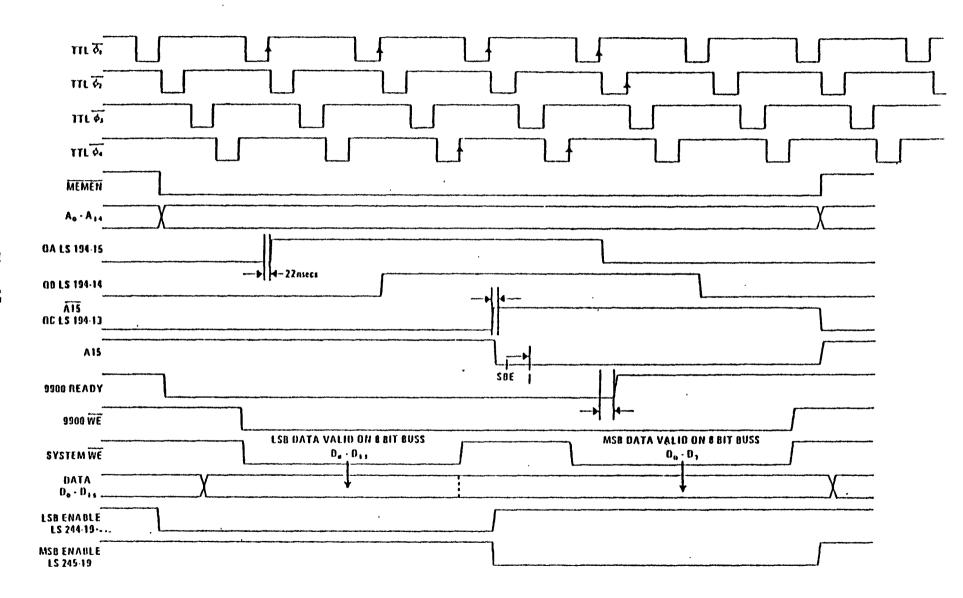

| 17       | External CPU Write Timing                              |

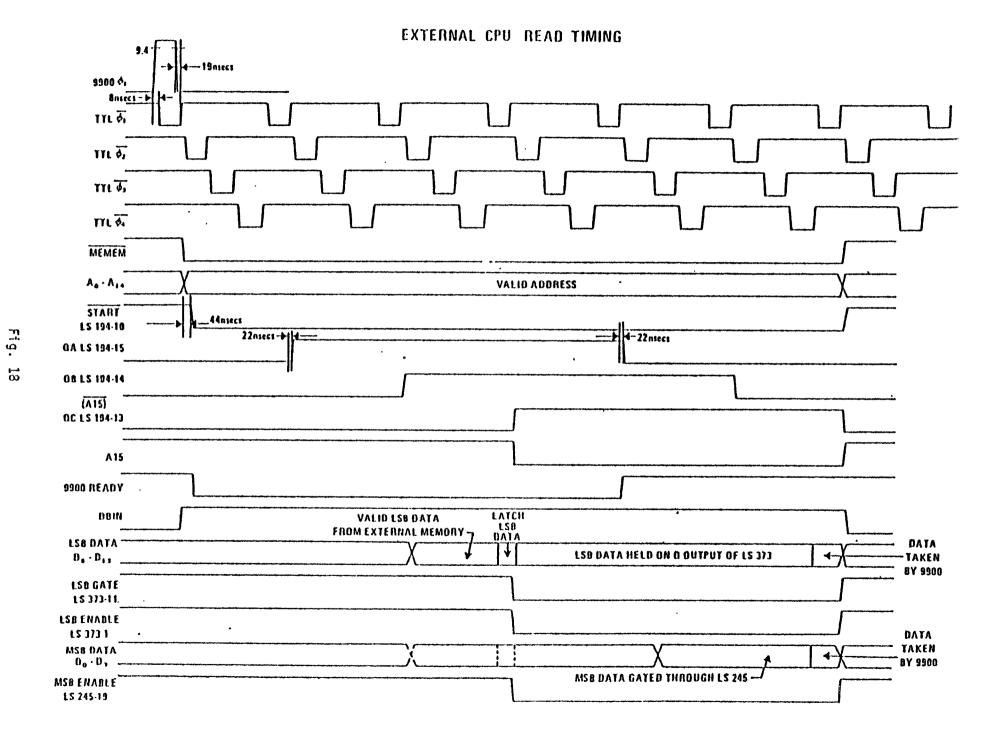

| 18       | External CPU Read Timing                               |

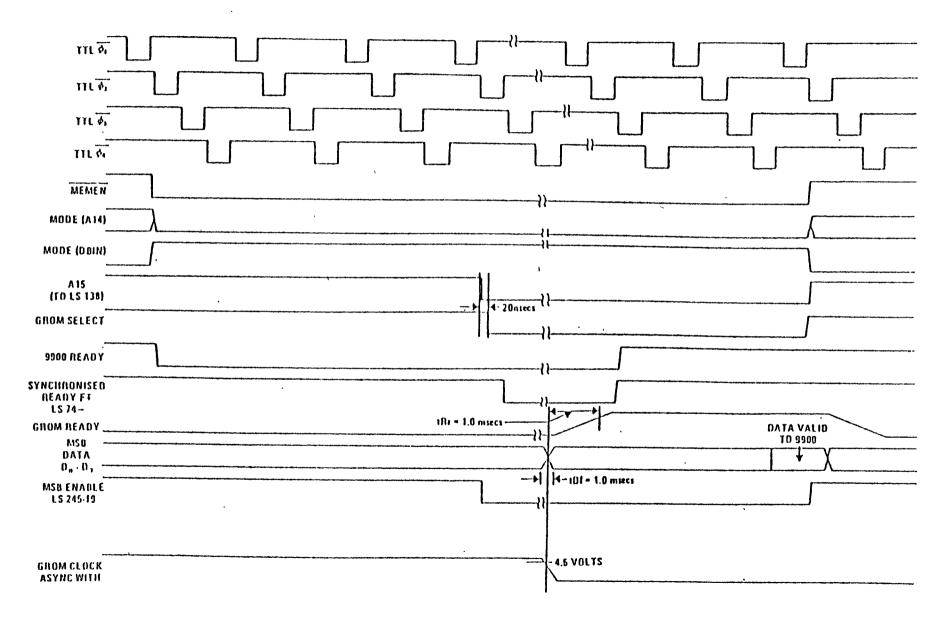

| 19       | GROM Read Timing                                       |

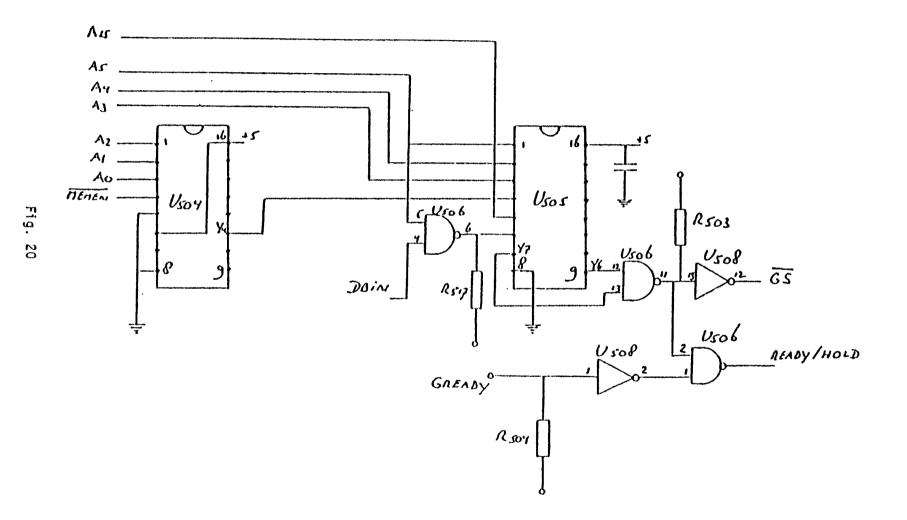

| 20       | GROM Selection And Ready Logic                         |

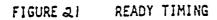

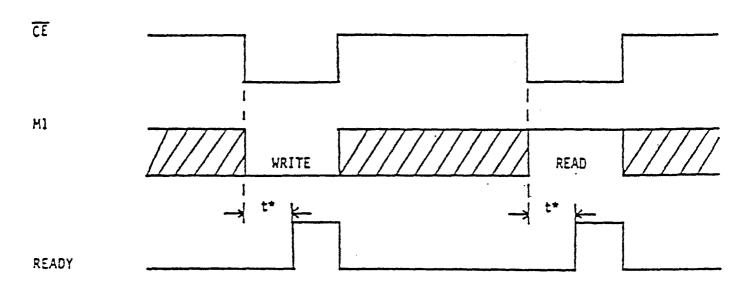

| 21       | Ready Timing                                           |

| 22       | TMS 9901 Pin Assignments And Functions 57              |

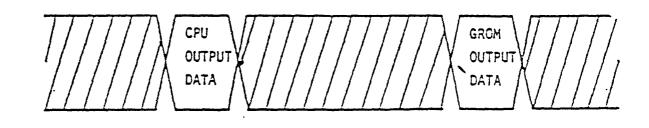

| 23       | TMS 9901 I/O Interface Section Block Diagram           |

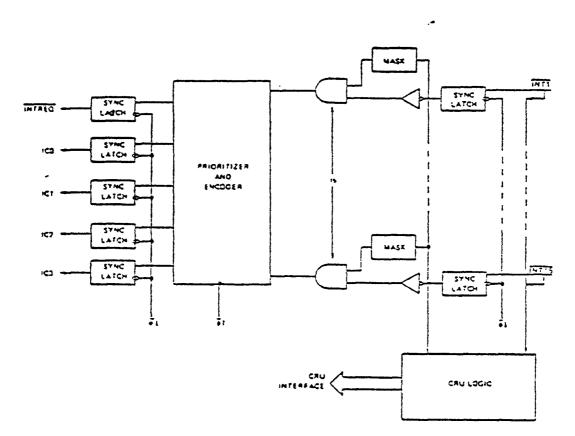

| 24       | TMS 9901 Interupt Handling Logic 61                    |

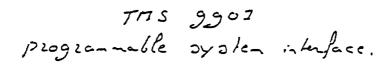

| 25       | TMS 9901 Programmable System Interface                 |

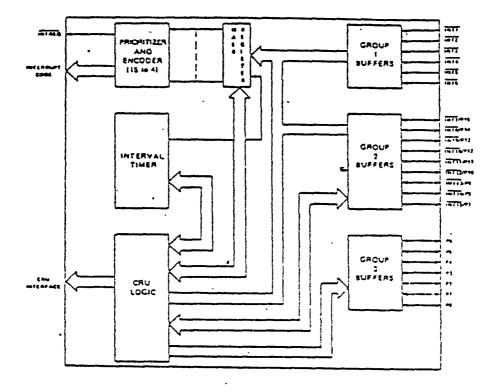

| 25       | TMS 9901 Interval Timer Section                        |

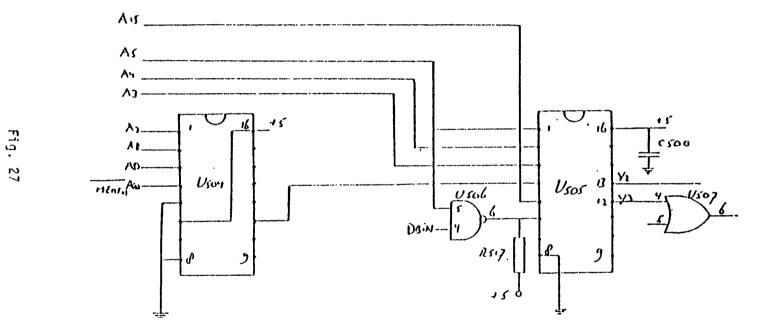

| 27       | VDP Selection Logic 69                                 |

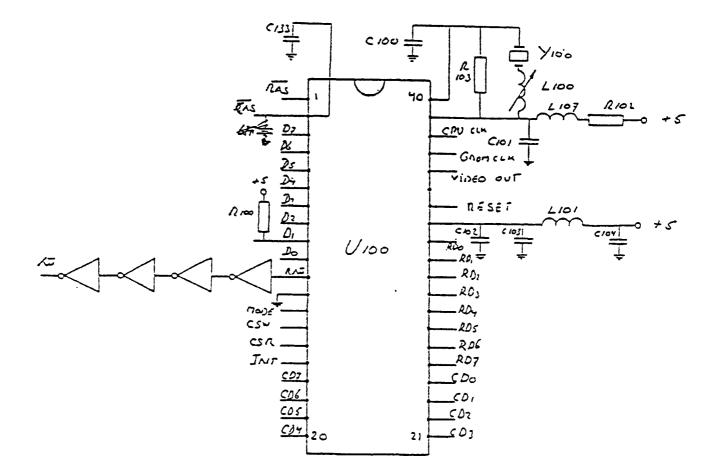

| 28       | Video Display Processor (VDP)                          |

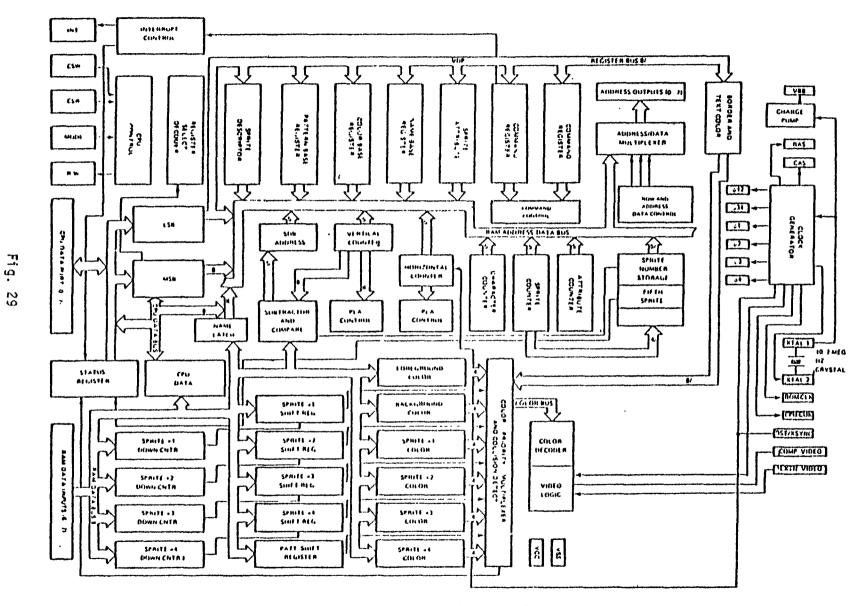

| 29       | TMS 9918 VDP Block Diagram 71                          |

| 30       | TMS 9919 Sound Processor Selection Logic               |

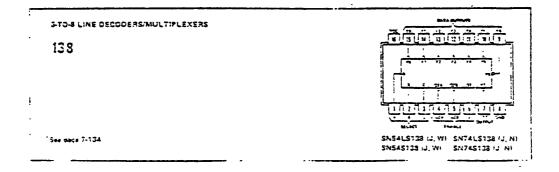

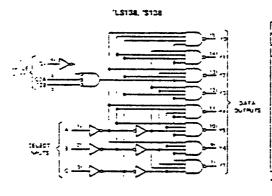

| 31       | LS 138 110                                             |

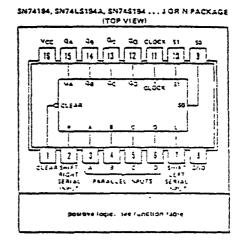

| 32       | LS 194 111                                             |

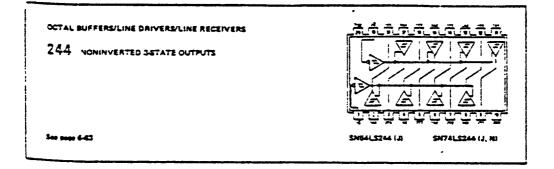

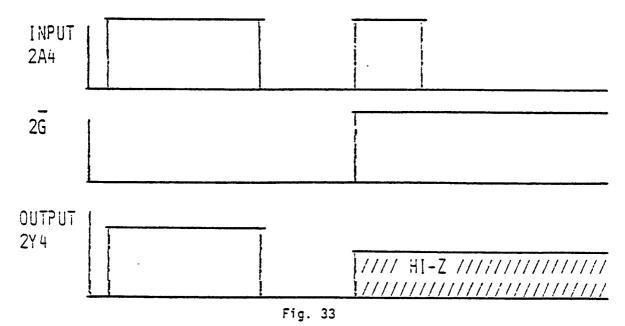

| 33       | LS 244 112                                             |

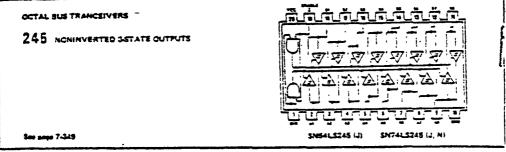

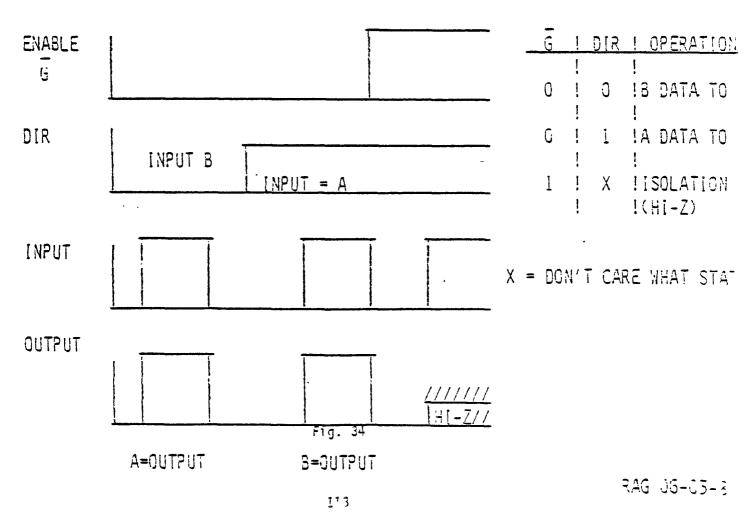

| 34       | LS 245 113                                             |

| 35       | TIM 9904 Four - Phase Clock Generator Driver 114       |

| 36<br>37 | TIM 9904 Four - Phase Clock Generator Driver 115       |

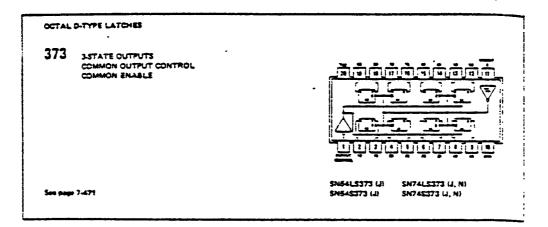

| 38       | LS 373 116                                             |

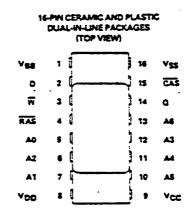

| 30<br>39 | 4116 Dynamic RAM 117<br>MF 4732 ROMS 119               |

| 40       | 6810 RAM                                               |

| 41       | Pin Outs For TMS 9900, U608-511, And U614-616 121      |

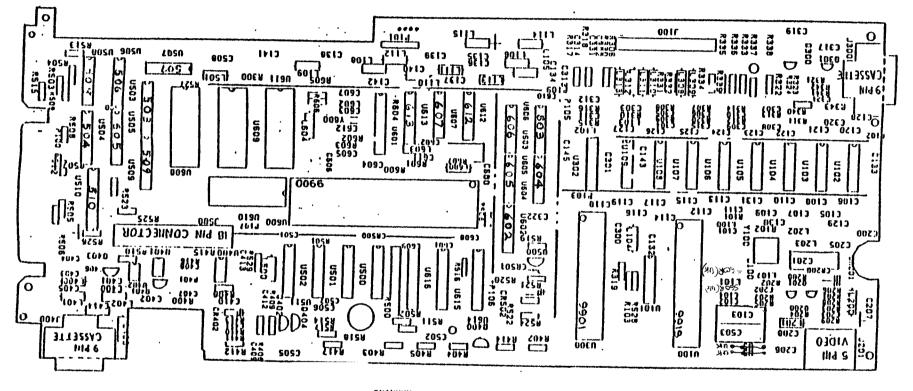

| 42       | Mainframe Board Lay-Out                                |

| 72       | Raini ane bueru Lay-Udt 122                            |

## SCHEMATIC PACKAGE: 99/4

| FIGURE # | DESCRIPTION                                | PAGE # |

|----------|--------------------------------------------|--------|

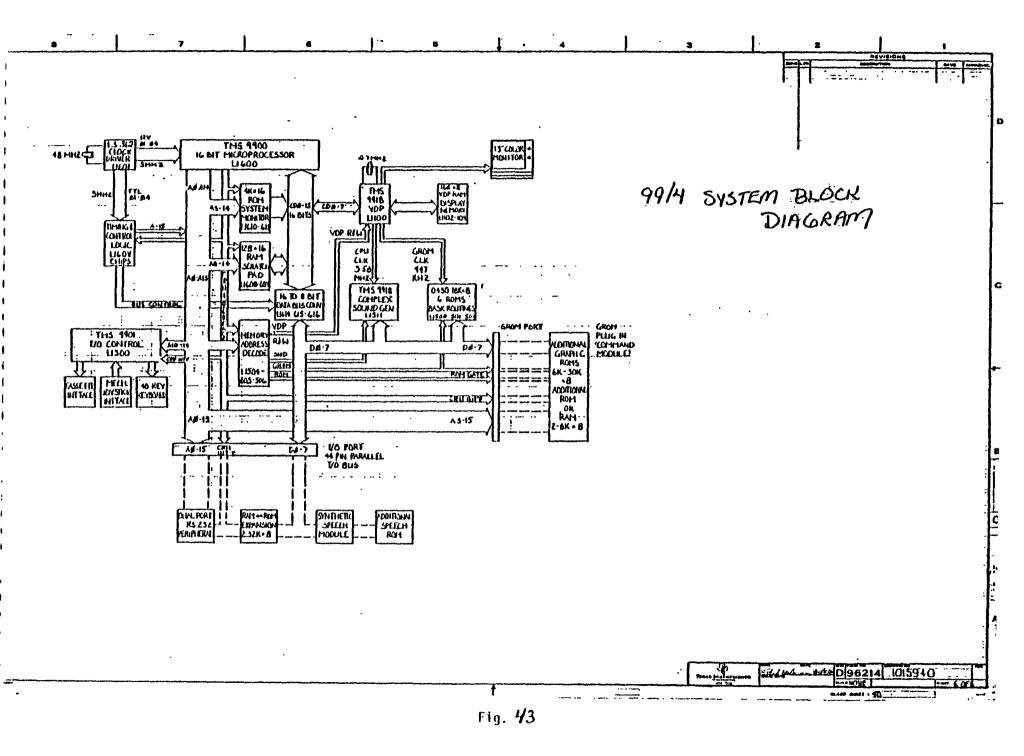

| 43       | System Block Diagram                       | 123    |

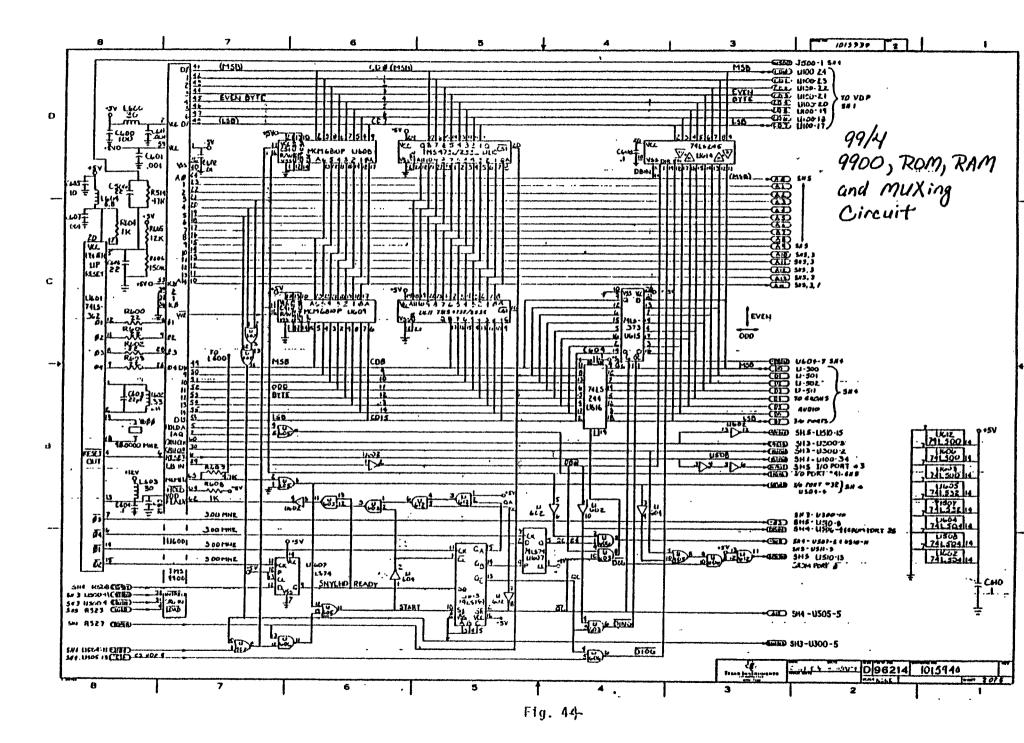

| 44       | 9900, ROM, RAM, And MUXing Circuit         | 124    |

| 45       | GROM And Audio Circuit                     | 125    |

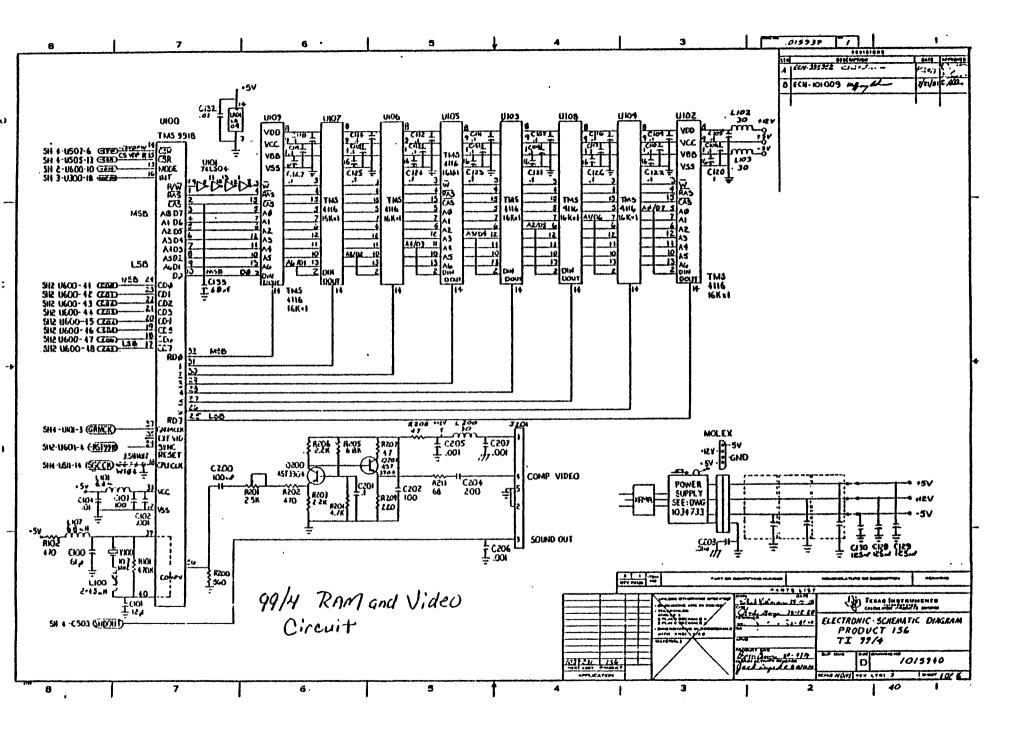

| 46       | RAM And Video Circuit                      |        |

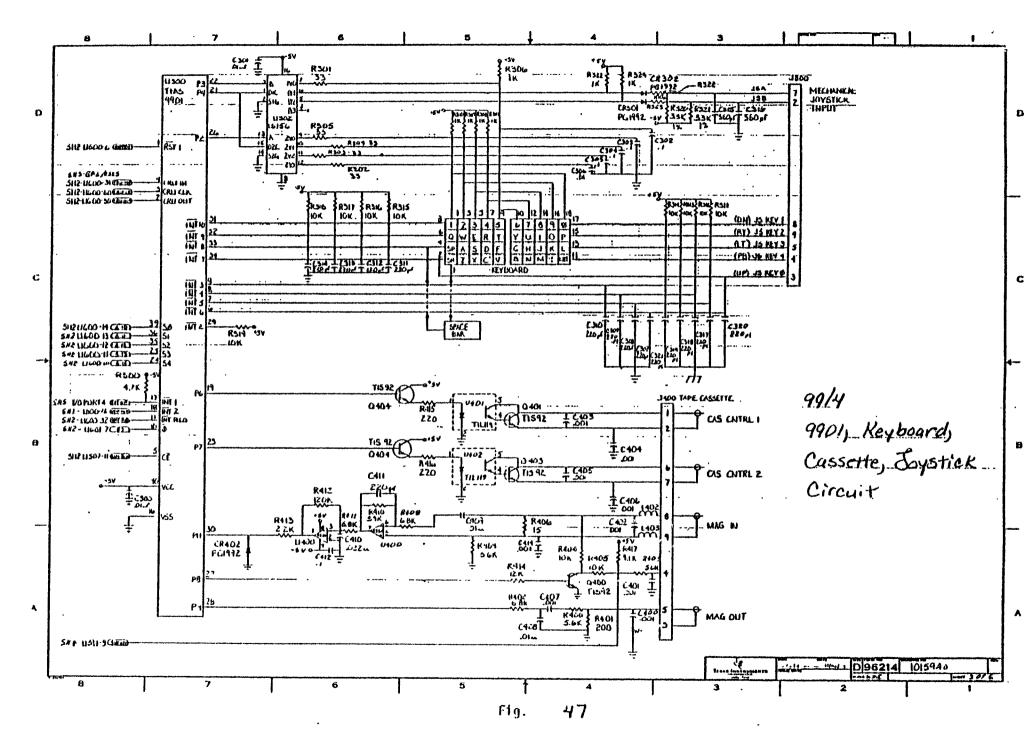

| 47       | 9901, Keyboard, Cassette, Joystick Circuit |        |

| 48       | I/O Buffers And I/O Port                   | 128    |

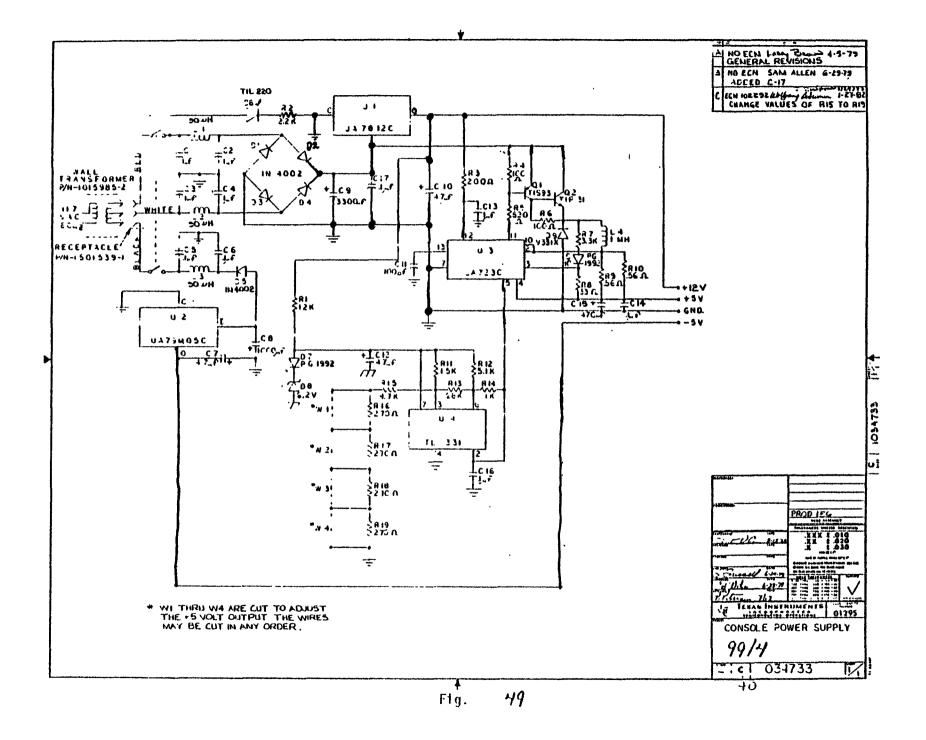

| 49       | Power Supply                               | 129    |

## SCHEMATIC PACKAGE: 99/4A

| 50 | System Block Diagram                       | 130 |

|----|--------------------------------------------|-----|

| 51 | 9900,ROM, RAM, And MUXing Circuit          | 131 |

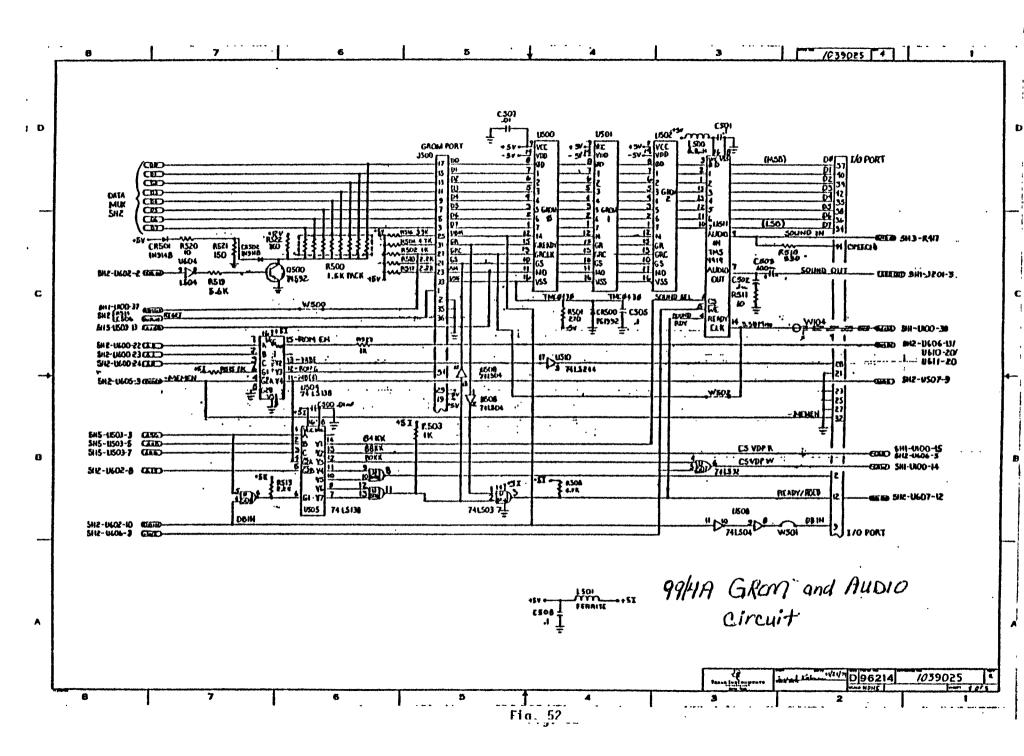

| 52 | GROM And Audio Circuit                     | 132 |

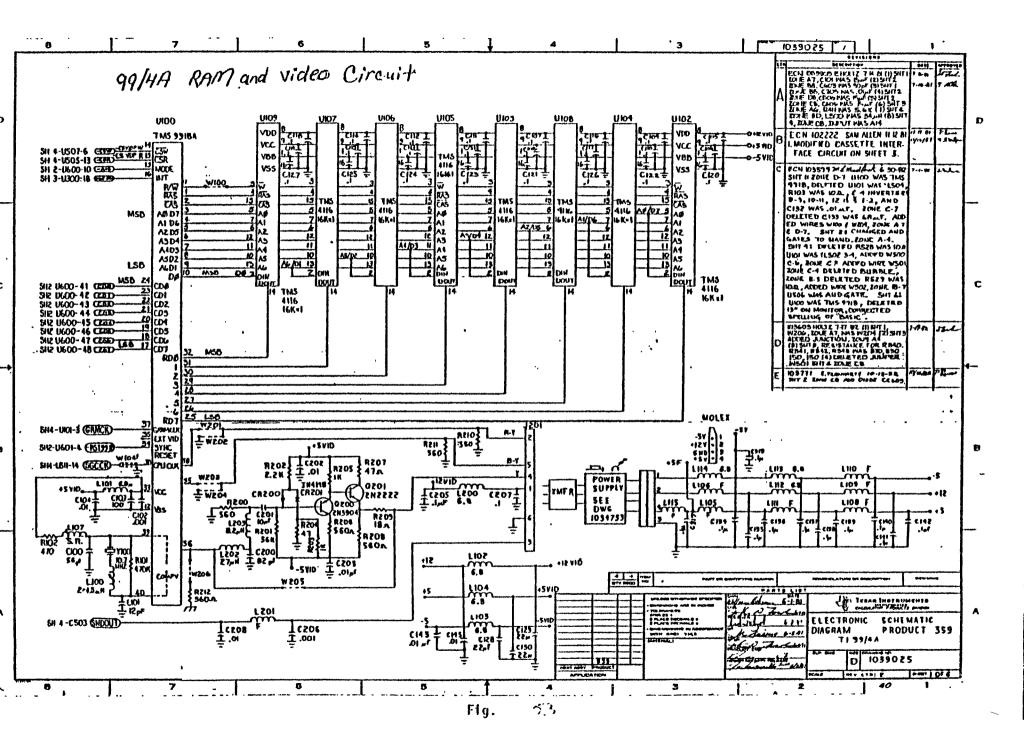

| 53 | RAM And Video Circuit                      |     |

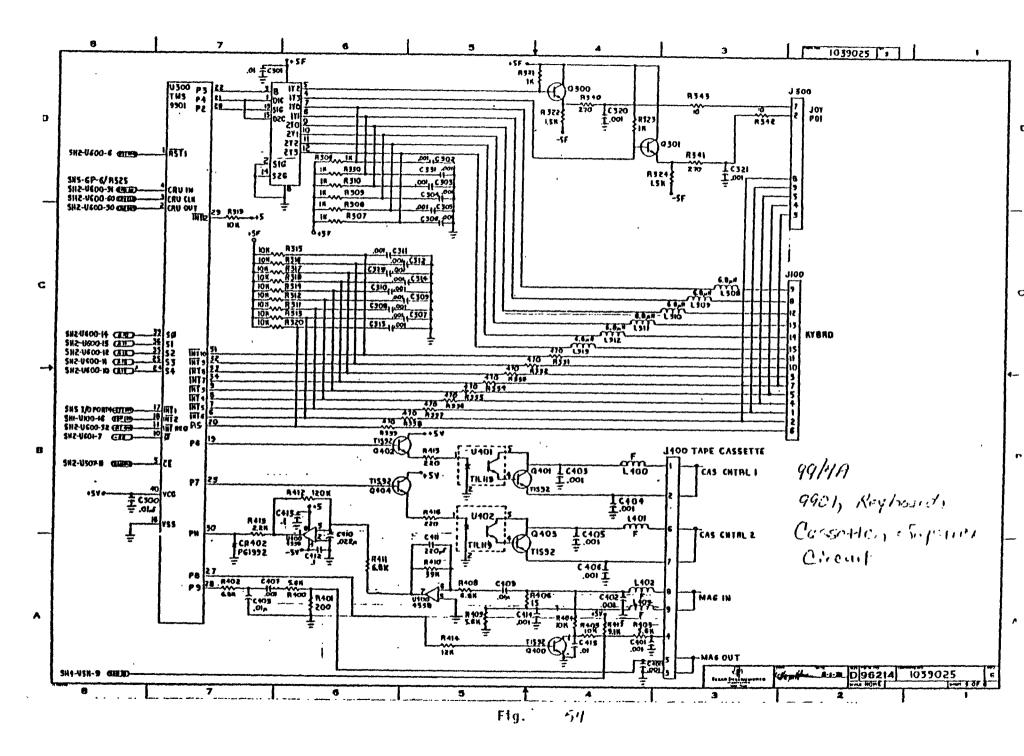

| 54 | 9901, Keyboard, Cassette, Joystick Circuit |     |

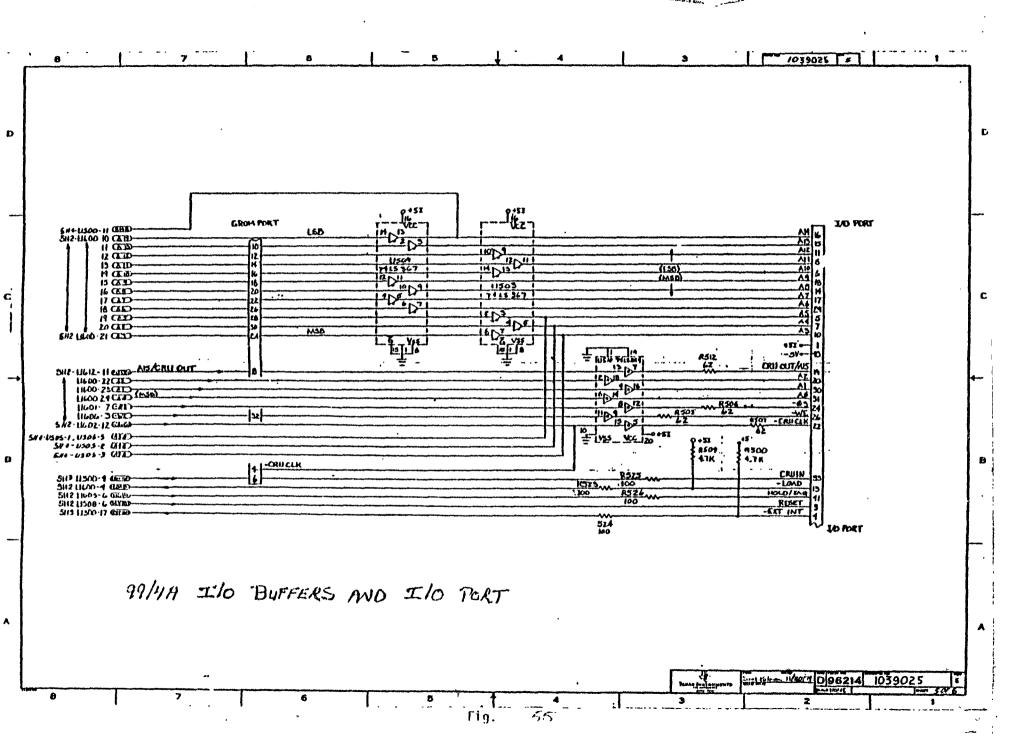

| 55 | I/O Buffers And I/O Port                   | 135 |

.

# LIST OF TABLES

| TABLE #                                                                    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                         | PAGE #                                                         |

|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 01<br>02<br>03<br>04<br>05<br>06<br>07<br>08<br>09<br>10<br>11<br>12<br>13 | Summary Of 9900 Microprocessor Instructions<br>GROM I/O Operations<br>GROM Memory Map<br>9901 Interupt Mapping<br>9901 I/O Mappling<br>Peripheral Addresses On CRU Bus<br>Color Vector Relationships<br>Screen Display Parameters<br>VDP Registers<br>Attenuation Control<br>Noise Feedback Control<br>Noise Generation Frequency Control<br>Register Address Field | 49<br>51<br>58<br>58<br>59<br>65<br>65<br>72<br>73<br>74<br>74 |

## iv

.

#### INTRODUCTION

The TI 99/4 Home Computer was initially presented at the Consumer Electronics Show in June 1979 by Texas Instruments. The TI 99/4 is a TMS 9900-based microprocessor system. presently, the 99/4A mainframe is being manufactured by the Consumer Products Division of Texas Instruments, Inc. in Lubbock, Texas.

The TI 99/4A has many key features. Some of these feature include 16-color graphics, music and sound over four octaves. The TI 99/4A also makes use of an expanded TI Basic. This feature plus the capability for up to 72K bytes of memory (16K RAM internal, 26K ROM, and up to 30K ROM interfaced via the Command Module peripherals) make the TI 99/4A Home Computer a very powerful tool. These key features and the general operation of the TI 99/4A will be presented in the following pages.

#### SYSTEM BLOCK DIAGRAM:

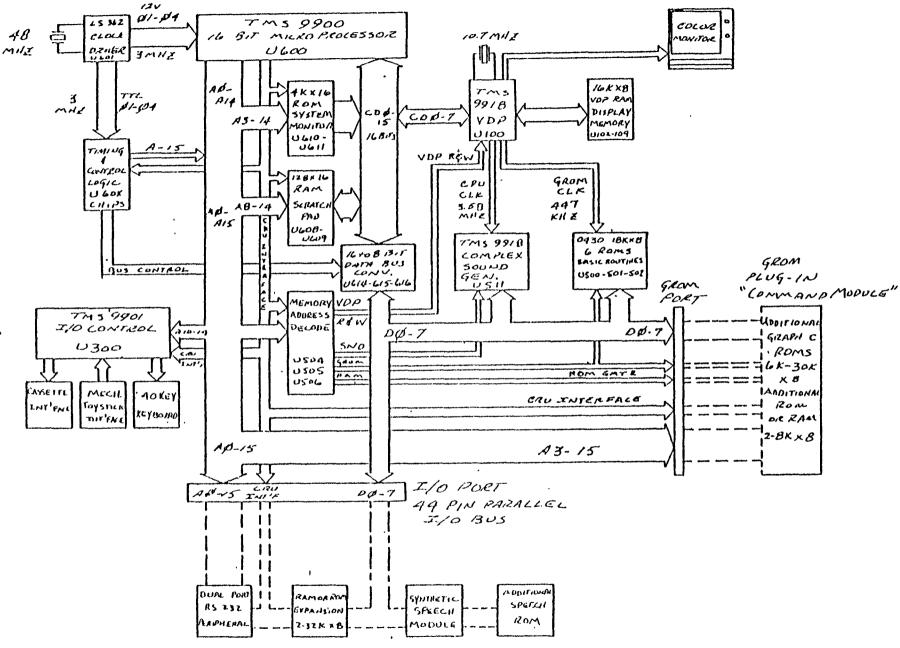

The TI 99/4A Home Computer effectively combines each of the individual features of the unit into a complete and complex system. The basic blocks of the system include the CPU, sound generation, video display, I/O control, plus timing and control logic. These features are interfaced to produce the complete microprocessor system. The system block diagram of the TI 99/4A is shown in Figure 1, p. Q.

٦

99/4 SYSTEM BLOCK DIAGRAM

Fig. 1

#### HOME COMPUTER KEY ARCHITECTURAL FEATURES

- 9900 CPU

- VIDEO PROCESSOR WITH 10.74 MHz CRYSTAL OSCILLATOR FOR NTSC COMPOSITE VIDEO GENERATION AND CONTROL OF GRAPHICS RAM

- GRAPHICS ROMS ONBOARD WITH 6K BYTES EACH, EXPANSION PORT FOR SOFTWARE MODULES WITH UP TO FIVE 6K X 8 GROMS AND 8K ROM OR RAM

- 48 KEY KEYBOARD

- TV INTERFACE VIA VIDEO MODULATOR

- PERIPHERAL CONNECTORS WITH CRU AND 8 BIT MEMORY INTERFACE

.

● 1200' BAUD HOME CASSETT INTERFACE

#### HOME COMPUTER TMS 9918 VIDEO DISPLAY PROCESSOR KEY FEATURES

- REFRESH THE TV SCREEN AT 60 Hz WITHOUT INTERLACE FOR COMPOSITE NTSC VIDEO OUTPUT

- 24 LINES OF 32 CHARACTERS WITH <u>8 X 8 DOT RESOLUTION</u>

- <u>32 MOVABLE CHARACTERS</u> WITH MAGNIFICATION

- **\$** 24 LINES OF 40 CHARACTERS WITH 6 X 8 DOT RESOLUTION

- 9 48 LINES OF 64 INDEPENDENT SPOTS

- EXTERNAL VIDEO INPUT WITH SYNC

- PROVIDE <u>8 COLORS</u> WITH 2 LUMINOUS LEVELS EACH

- PROVIDE 8 SETS OF COLOR SELECT REGISTERS TO PROVIDE SEPARATE COLOR FOR ONES AND ZEROS

- 3 ADDRESS 4-16K BYTES OF RAM FOR CPU OR DISPLAY

- SINGLE 5 VOLT POWER SUPPLY

- 10.74 MHz ONBOARD CRYSTAL OSCILLATOR

- GROM CLOCK

- ✤ 40 PIN PLASTIC PACKAGE

#### HOME COMPUTER TMC Q430 GRAPHICS ROM KEY FEATURES

- € 6144 BYTES MASK PROGRAMMABLE ROM

- 16 BIT ADDRESS REGISTER WITH INCREMENTER

- CHIP SELECT FROM 3 MOST SIGNIFICANT ADDRESS BITS

- INSTRUCTION DECODE FOR FOUR OPERATIONS

- READ BYTE AND INCREMENT

- WRITE HIGH ADDRESS BYTE AND TRANSFER HIGH TO LOW

- READ LOW ADDRESS BYTE

- SPARE TO WRITE RAM OR PROM

- LOW COST P CHANNEL MOS

- 9us CYCLE TIME

- +5, -5 POWER SUPPLIES WITH TTL INTERFACE

- 447.5 KHz CLOCK INPUT

- 16 PIN PACKAGE

## HOME COMPUTER TIM 9919 SOUND GENERATOR KEY FEATURES

- <u>3 VOICES</u> WITH <u>4 OCTAVE MUSCIAL</u> RESOLUTION

- 15 BIT PROGRAMMABLE NOISE SHIFT REGISTER

- 100 MW AUDIO DRIVE WITH <u>30DB CONTROL</u> IN 2DB STEPS

- 8 BIT CPU INTERFACE

- 5V POWER SUPPLY

- I<sup>2</sup>L TECHNOLOGY

- 15 PIN PACKAGE

POWER IS TURNED ON:

- 9900 CPU RESETS AND ADDRESSES LOW EPROM LOCATIONS

- 9900 INITIALIZES

- 9900 SETS UP WORKSPACE REGISTERS IN 6810 RAM

- 9900 BEGINS READING FROM GROMS

- 9900 ENTERS TIME DELAY LOOP TO ALLOW STABILIZATION 5 SEC

- 9919 SOUND CHIP IS TURNED OFF

- -9918 VDP IS INITIALIZED

- 4116 RAM IS CLEARED REQUIRES APPROXIMATELY 1 SEC

- FRONT PANEL DISPLAY IS WRITTEN INTO VDP

- 9919 SOUND CHIP EMITS BEEP

- 9900 CPU ENTERS KEYBOARD SCAN ROUTINE

SYSTEM IS NOW READY FOR USER INPUT

#### ITEMS TO CHECK DURING DEBUG

- 1 CHECK IF FRONT PANEL IS UP "TI LOGO" 2 - CHECK ±5, ±12 VOLT LEVELS THROUGHOUT BOARDS 3 - CHECK IF <u>READY</u> PIN 64 OF 9900 IS LOCKED UP 4 - CHECK THE FOUR 12 VOLT CLOCKS FROM 74362 to 9900 5 - CHECK GROM SELECT PIN 10 0430 GROM READY PIN 15 0430 GROM CLOCK PIN 13 0430 6 - CHECK PIN 38 OF 9918 FOR 3.579520 MHz CLOCK 7 - CHECK VDP (9918) READ PIN 15 9918 WRITE PIN 14 9918. 8 - CHECK DATA OUT OF 4116 RAM PIN 14

- 9 CHECK COMPOSITE VIDEO FROM DIN CONNECTOR

#### HOME COMPUTER CASSETTE INTERFACE

- 1. Operates with byte/manchester encoding format.

- 2. Utilizes redundancy to gain increased reliability.

- 3. Uses wave shaping on input and output to increase reliability.

- 4. Has two motor control circuits which allow computer to control decks.

- 5. Has capability of reading from one deck and writing to another, under computer control.

- 6. The interface is software intensive and relies on 9901 internal timer for it's timing.

PROBLEM AREA OF CASSETTE INTERFACE -

- 1. Reliable recovery of data is dependant on recorder used during save.

- 2. Reliability is directly proportional to frequency response of cassette deck.

- 3. Reliability can be observed by looking for the "eye" or "jitter" phenomenon with an oscilloscope.

- A. Present reliability is dependant on amount of jitter. If jitter is less than 60 ms cassette should work.

- 4. Cassette is also adversely affected by speed changes.

A. Motor control curcuit can under special circumstances cause this.

#### GENERAL DESCRIPTION OF THE 99/4A

The following paragraphs provide a description of the 99/4A system hardware, the VDP chip (TMS 9918), the sound chip (TMS 9919), the GROM (TMC 0430), the associated timing diagrams, the cassette interface circuitry and power supply.

#### 99/4 SYSTEM HARDWARE

The 99/4 has been built around the TMS 9900 microprocessor. Fig. 1 shows a block diagram of the system. In this description the logic of the 99/4A is grouped into the following functional sections.

- Clock generator/driver

- Microprocessor unit

- Memory selection logic

- System ROM & RAM

- 16 to 8 bit interfacing circuit

- Timing and control logic

- GROM memory

- TMS 9901 programmable system interface

- TMS 9918 video display processor

- TMS 9919 sound generator

- Keyboard, remote handheld unit

- Cassette interfacing circuit

- I/O port

- Power supply

- European power supply

- Audio board

The purpose and composition of these functional sections is to provide an overview of the 99/4A system with a detailed description in the succeeding paragraphs.

- The clock generator/driver provides 4 non-overlapping clock signals for the TMS 9900 microprocessor and also internal latch which is used in the reset circuitry.

- The microprocessor unit with the TMS 9900 handles all the processing as required by the on board software as well as the off board software (DSR's and command modules), interrupts, and power-up initialization.

- The memory address/decode logic provides enabling signals to the various RAM's, ROM's, GROM's and interface circuit.

- System RAM consists of 256 bytes static RAM used as a scratch pad memory for all system operations. The system ROM consists of 8K bytes of the following system programs.

- The GPL interpreter.

- Floating point routines.

- String conversation routines.

- Cassette interfacing and I/O programs.

- Basic programs.

- The 16 to 8 bit interfacing circuit enable the 99/4 to access 8 bit devices by multiplexing and demultiplexing the 16 bit data bus of the TMS 9900.

- Timing and control logic provides the timing and enable signals for the 16 to 8 bit interfacing circuit. It also handles the READY and WE signal for memory operations.

- The TMS 9901 I/O controller is the interface used by the keyboard scanning circuit and the cassette interfacing circuit. It also handles interrupts and has an on-chip timer.

- GROM memory consists of 18K bytes of graphics program. (Graphics is the intermediate language used in the 99/4) It contains the following system routines:

| GROM D : | - Monitor routines                                |

|----------|---------------------------------------------------|

|          | - First part of the equation calculator.          |

|          | - The cassette device subroutine contain ROM.     |

| GROM 1 : | - The editor                                      |

|          | - The prescan routine for basic.                  |

|          | - The first part of the basic executing program.  |

| GROM 2 : | - The file management programs.                   |

|          | - The second part of the BASIC executing program. |

|          | - The second part of the equation calculator.     |

Grom memory is expandable up to a limit of 48K through the grom I/O Port.

The GROM port enables the user to run preprogrammed sofware in up to 5 GROM's in a software module. This module may also contain in ROM processing for generating the composite video signal. A part of the 16K byte user RAM contains the character code table which is downloaded in the RAM during the power-up sequence.

- The TMS 9919 sound generator is a one chip device capable of generating 3 tones and noise programmable by the user.

- The keyboard interface is using the TMS 9901 I/O chip. The keyboard scanning is using the multiplexing technique.

- The I/O port provides the capability to the 99/4 to access the ROM in the various peripherals containing the device service routines (DSR's) and is takes care of the data exchange.

- The audio board houses an audio amplifier to drive the 8 ohm loadspeaker in the European version of the 99/4. Volume control is by a slide pot.

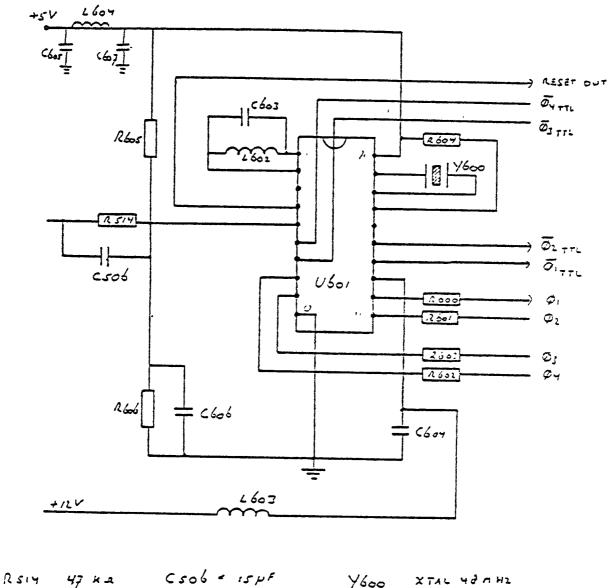

#### OSCILLATOR CIRCUIT

### GENERAL DESCRIPTION

## ------

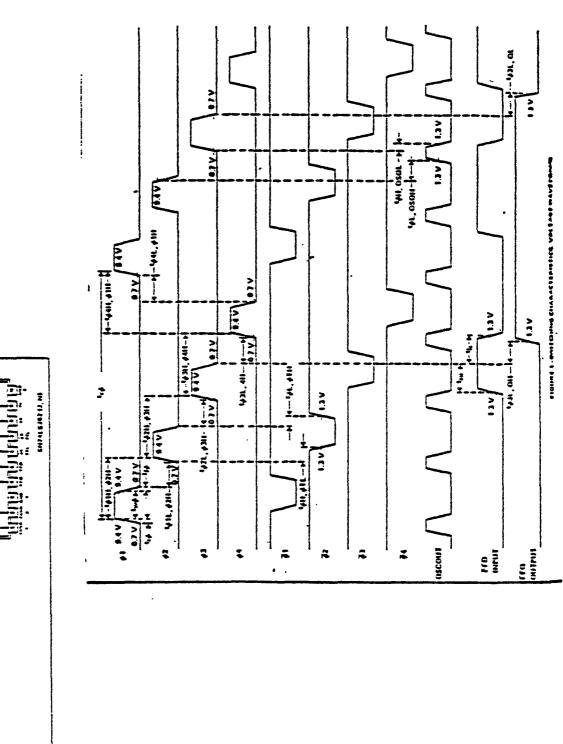

The TMS 9900 microprocessor, as used in the TI99/4, uses four non overlapping clock signals generated by a 74LS362 clock generator/driver. These four clock signals Q1, Q2, Q3, and Q4 have a 12 volt swing. For system synchronization purposes the inverted clock signals (Q1, Q2, Q3 and Q4) are available at TTL level. A timing diagram for the clock signals is given in figure 35, As can be seen from the internal schematics of the 74LS362 figure 35, there is also a D type latch available. This latch, clocked by Q3, is in the reset circuitry.

HARDWARE DESCRIPTION (see figure 2, pir.)

POWER CONNECTIONS

Power connection points are pin 10 for ground, pin 13 for the +12 volt, and pin 20 for the +5 volt supply. L603, L604, C604, C605 and C607 are used for decoupling of noise generated by the 74LS362.

#### POWER UP

Pin 17, conected to the 5 volt power supply by serie resistor R604 enables the clock outputs.

#### RESONATOR PART

A third overtone, 48MHz crystal, connected between pin 18 and 19 determines the clock frequency. The tank circuit with L602 and L603 connected between PINS 1 and 2 selects the third overtone. Some units may use a RMHZ crystal with tank components to select the primary frequency.

#### CLOCK SIGNALS

Pin 8, 9, 11 and 12 are the four 12 volt clock outputs for the TMS 9900. The four series resistors R601, R602 and R603 minimize over and undershoot. The inverted clock signals on pin 6, 7, 14 and 15 are used internally in the 99/4 for timing purposes.

#### RESET

Reset is accomplished during power-up and when a solid state software command module is inserted.

C606 will be slowly charged by resistor R605 after applying power to the console. Thus for a short period the D input of pin 5 of the 74LS362 is low. The 74LS362 clocks this zero binary value to the reset out of pin 4. This signal resets the TMS 9900 until a binary 1 value is sensed on pin 5. When the system is switched off, R606 discharges C606, thus enabling a new reset. When a solid state software command module is inserted, the reset line is connected to -5 volt. C606 is then partly discharged by C506, thus dropping the voltage at pin 5 for a short time to the binary low level, generating a reset. When the solid state software command module is removed, resistor R514 will descharge C506 to enable a new reset.

- R 600 C 603 22 2 22 pF R Goi 22 2 C 604 تمس ا . R 602 22 2 Cbos 10 pF R 603 22 . C 606 79 21 R 604 IKR C 607 1 NF 2605 12 KA R 606 150 x 2

- Y600 XTAL 48 A H2 U601 74 LS 362

Fig. 2

#### CENTRAL PROCESSING UNIT

## GENERAL DESCRIPTION

-----

The 99/4 Home Computer uses the Texas Instruments TMS 9900 microprocessor. It provides the system with a 15 bit address and 16 bit data bus for communication with external memory. It also has input and output pins for serial in and output, interrupt handling and memory control (see figures  $3 \text{ cnd} \rightarrow$ , fr 30-23)

#### MEMORY INTERFACING

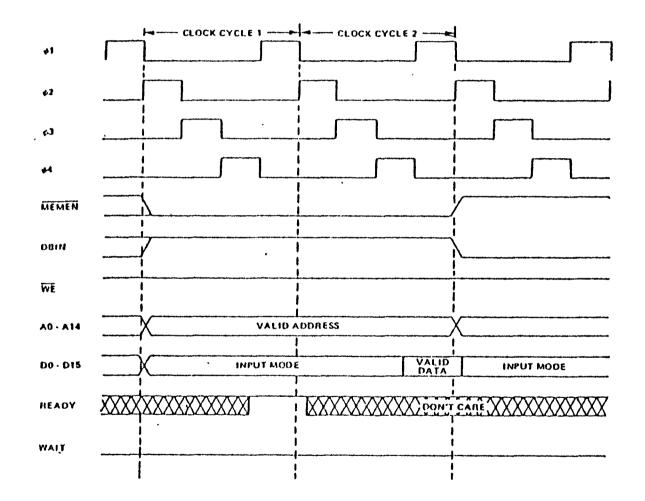

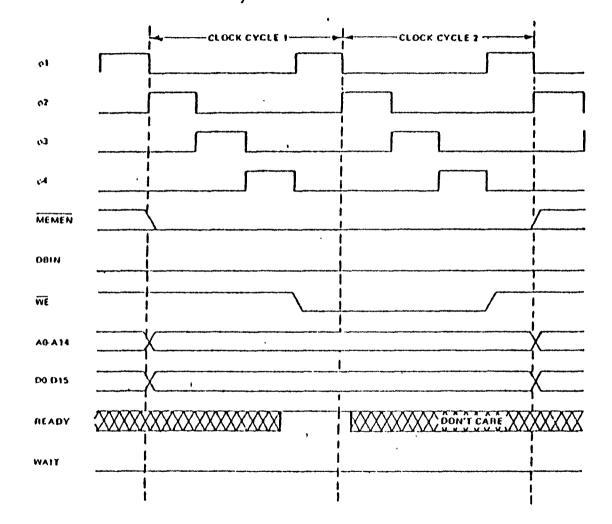

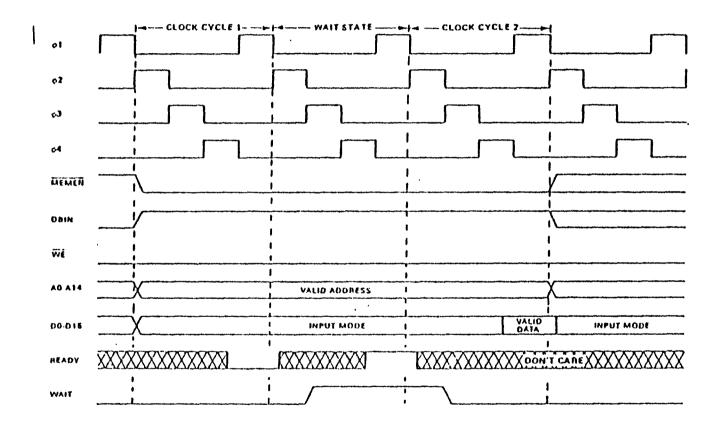

The TMS 9900 interfaces with memory by means of a 16 bit data bus (DO-D15), the 15 bit address bus (AO-A14) and the following control signals.

- MEMEN MEMORY ENABLE. When active (low), MEMEN indicates that the address bus contains a memory address.

- WE WRITE ENABLE. When active (low), WE indicate that memory write data is available from the TMS 9900 to be written into memory.

- DBIN DATA BUS IN. When active (high), DBIN indicates that the TMS 9900 has diabled its output buffers to allow memory to place read data on the data bus during MEMEN.

- READY READY. When active (high), READY indicates that memory will be ready to read or write during the next clock cycle. When not ready is indicated during a memory operation, the TMS 9900 suspends further operating (e.g. enters a wait state) until READY becomes active again, after which the memory read/write cycle is completed. This signal enables the use of slow memory devices with the TMS 9900.

- WAIT WAIT. When active (high), WAIT indicates that the TMS 9900 has entered a wait state because of a not-ready condition from memory.

Timing diagrams for read and write cycles, with and without wait states, are given in figures 5-6, pp. a5-ab.

#### DIRECT MEMORY ACCESS

Performing memory access without interference of the TMS 9900 is called direct memory access (DMA). For this purpose the following control lines are available.

HOLD HOLD. When active (low), HOLD indicates to the processor that an external controller disires to use address, data and memory control signals. The TMS 9900 enters the hold state following a hold signal when it has completed its present memory cycle. The processor then places the address and data buses in the high-impedance state along with MEMEN, WE and DBIN and responds with a holdackowledge signal (HOLDA). When HOLD is removed, the processor returns to normal operation. HOLDA HOLD ACKNOWLEDGE. When active (high), HOLDA indicates that the processor is in the hold state and that the outputs (MEMEN, WE and DBIN) are in the high inpedance state thus making is possible for an external device to use the buses and access memory.

The timing diagram for direct memory access is given if figure 9, p. 24.

- IN AND OUTPUT (I/O)

- The TMS 9900 has two possibilities for communicating with external devices: A. Addressing the device as memory.

- B. Using the communication resister unit (CRU).

The CRU makes it possible to communicate with external devices with fewer lines. Only A3 through A14, CRUIN, CRUOUT and CRUCLK are used. The CRU I/O bus makes it also possible to address bits instead of bytes or words.

#### OUTPUT

Output with the CRU interface is performed as follow. The processor addresses the bit to be set. This address is decoded and enables a latch to the data present on the CRUOUT line on CRUCLK.

#### INPUT

Input is performed only with the address bus and CRUIN. Again the processor addresses the bit to be read. The system hardware decodes the bit address on A3 through A14 and enables the addressed bit to put its value on the CRUIN line. The bit is then fetched by the TMS 9900.

#### TIMING DIAGRAM

A timing diagram of CRU operations is given in figure  $10, f \cdot 30$ .

The TI 99/4 home computer uses both ways of I/O to communicate with internal and external devices.

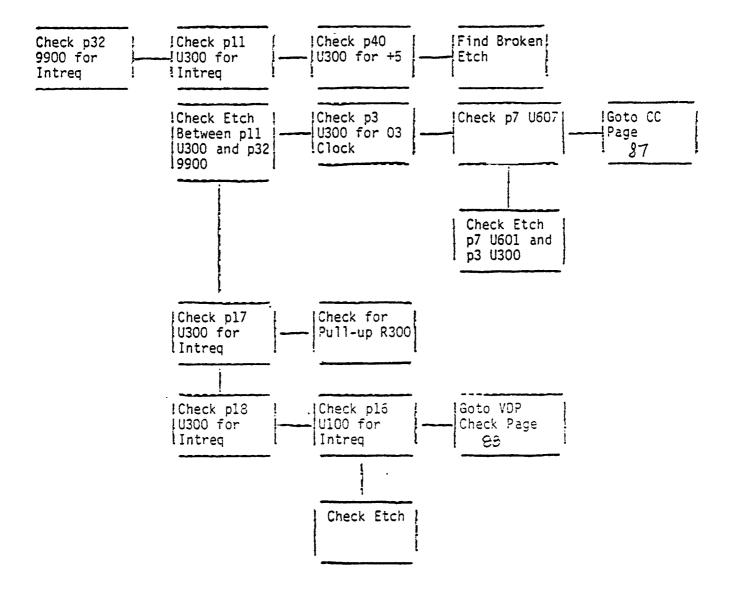

#### INTERRUPT HANDLING

Interrupt processing logic on the TMS 9900 uses the following inputs.

INTREQ INTERRUPT REQUEST. When active (low) INTREQ indicates that an external interrupt is requested. If INTREQ is active, the processor loads the data on the interrupt-code input lines ICO through IC3 into the internal interrupt-code storage resister. This code is compared to the interrupt mask bits of the enabled interrupt level, the TMS 9900 interrupt sequences is initiated. If the comparison fails, the processor ignores the request. INTREQ should remain active and the processor will continue to sample ICO through IC3 until the program enables a sufficiently low priority to accept the requested interrupt.

ICOINTERRUPT CODES. ICO is the most significant bit of the interruptIC1code, which is sampled when INTREQ is active. When ICOIC2through IC3 are LLLH, the highest external priority interruptIC3and when HHHH the lowest priority interrupt is being requested.

In this system, ICO, IC's, and IC2 are tied to VSS, and IC3 is tied to VCC, thus if INTREQ is active, it is always considered the highest priority.

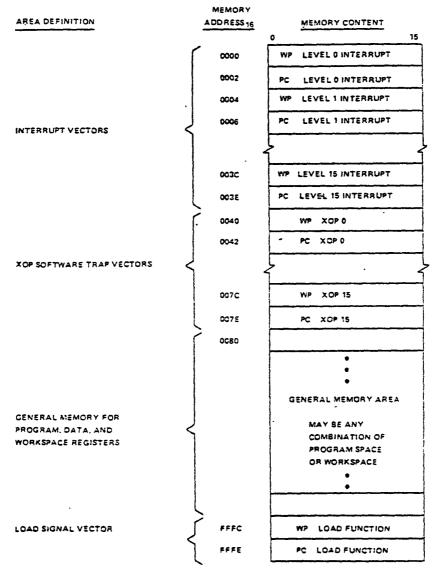

TIMING SIGNAL The TMS 9900 has an additional timing signal IAQ which becomes high during any memory cycle when the TMS 9900 is acquiring an instruction. This signal can be used for timing purposes. SUPPLY VOLTAGES The TMS 9900 requires 3 voltages with respect to ground. VBB - 5 volt supply voltage + 5 volt supply voltage VCC VDD +12 volt supply voltage VSS system ground CLOCK INPUTS Four clock signals Q1, Q2, Q3 and Q4 have to be provided on the four clock input pins for internal timing of the TMS 9900. Note that these inputs require a 12 volt swing. SYSTEM START UP The following signals can be used for system start up. RESET RESET. When active (low), RESET resets the processor. When RESET is released the TMS 9900 starts execution of its programs with the first memory address fetched from memory location 0002. LOAD LOAD. When active (low), the processor starts execution of its programs on the address in memory location FFFE. During a reset or load the microprocessor also fetches the workspace pointer. This is the starting address of a memory field of 16 words in RAM memory which is used as a register field. During reset the workspace pointer is fetched from adress 0000, during load from address FFFC.

HARDWARE DESCRIPTION

A drawing of the connections to the TMS 9900 as used in the 99/4 is given in figure -1,  $\rho \cdot 21$ .

The following list describes the connections in more detail.

POWER CONNECTIONS

- + 5 volt. The +5 volt power supply is connected to PIN 2 and 59 of the TMS 9900. L600, C600 and C611 are acting as a filter to reduce system noise on PIN 2 and C603 is used for the same purpose on PIN 59.

- +12 volt. The +12 volt power supply is connected to PIN 27 L601 and C612 are acting as a filter to reduce noise.

- 5 volt. The -5 volt power supply is connected to PIN 1 with C602 for decoupling.

GROUND

Pin connections 26 and 40 are for ground.

CLOCK INPUTS Clock inputs Q1, Q2, Q3 and Q4 are input on pins 8, 9, 25 and 28 respectively. ADDRESS BUS The 99/4 uses the address bus internally without further buffering, except for A14, which is used on the GROMS (see I/O bus description). DATA BUS Internal ROM and RAM uses the data bus without buffering. To connect the data bus to internal 8 bit devices and for in and output, a special 16 to 8 bit interfacing circuit is used. CRU BUS CRUOUT, CRUIN and CRUCLK are used internally without buffering. INTERRUPT HANDLING Interrupt vector pins 33 through 36 are preset to code LLLH, the highest external priority interrupt. So the 99/4 knows only one interrupt level. The INTREQ line is connected to the TMS 9901, which handles the interrupts. RESET The system resets during power up or when a solid state software command module is inserted. This is done by connecting RESET pin 6 to pin 4 of the system clock generator (U601). LOAD The load function or pin 4 is connected to the I/O Port via resistor R523. WRITE ENABLE The WE function or pin 61 is used by fast system RAM without buffering and is modified by timing and control for other devices. IAO/HOLDA The instruction aquisition signal on pin 7 and the hold acknowledge signal on pin 5 are combined on OR-gate U605 to generate a combined signal. MEMORY ENABLE (MEMEN) This signal is buffered by OR-gate U605 for further use in and outside the 99/4. R607 is used as a pull up resistor to +5 volt to assure that memory is disabled during power up. DBIN The DBIN signal on pin 29 is buffered twice by inverting cates U602 for use within the 99/4 system. READY/HOLD READY and HOLD on pins 62 and 64 are combined to form one signal.

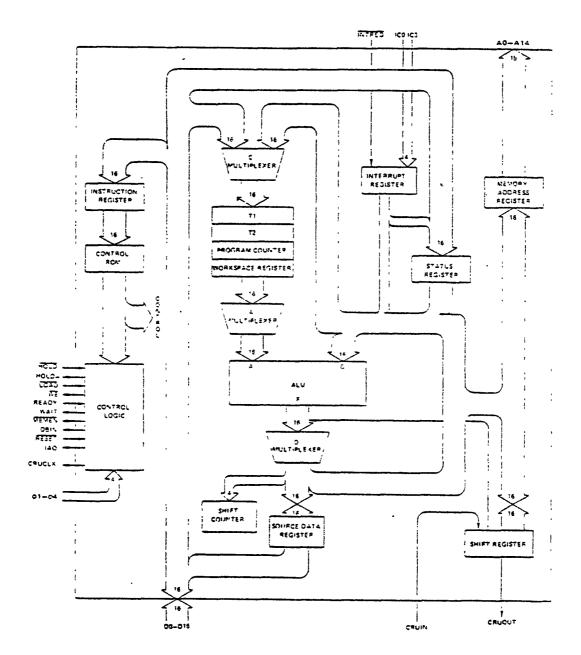

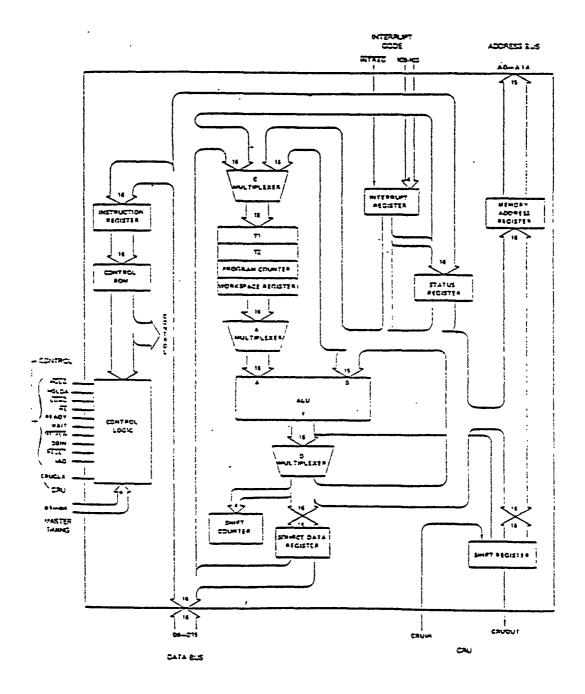

A study of 9900's internal structure is useful when trying to understand the operation of the IC. The architecture of the 9900 microprocessor is shown in the diagram of Fig.3, p.20. This shows the internal features within the CPU. These features include:

- \* The ALU

- \* 3 Multiplexer Busses

- \* Control Logic and Control ROM

- \* Internal Registers: Memory address register, shift register, status register, source data register, shift counter, workspace register, instruction register, and auxillary register T1 and T2.

The ALU (Arithmetic Logic Unit) is a 16-bit, parallel logic network used in the execution of the 9900's instructions. The unit performs arithmetic functions, log, and comparisons. The multiplexer busses are used in the transfer of flow of data in the CPU. The control circuitry provides the signals necessary for correct gating.

The control logic and control ROM provide the necessary signals for the correct sequencing or operation of the CPU's instructions. This is accomplished with the aid of the input control signals and master timing. Among the internal registers there are three which are key architectural features of the CPU. These registers are the workspace pointer, the program counter, and the status register. the workspace pointer contains the location of the first word in the workspace. The program counter contains the address for the next word which is to be used in the execution of an instruction. The status register determines if the conditions necessary for an instruction execution have been met. This is done by the setting of flags.

In the operation of the 9900, sixty-nine instruction words can be used. A list of the 9900's instruction set can be found in Table 1, *p*.31. These instructions are used to perform arithmetic operations, logic, comparisons, and manipulation operations on data. They are also used for the loading and storing of data within the CPU's internal registers. Data transfer between the external memory system and external devices is also made possible with the instructions via the CRU. Instructions are also used as control functions within the CPU.

The external memory used with the TMS 9900 in the TI99/4 and TI99/4A consists of two TMS 4732's and two MCM 6810P's. The TMS 4732's are 4K X 8 bit ROMS and are addressed via lines A3-A14 of the address bus. However, one of the 4732's uses the D1-D7 lines on the data bus while the other uses data lines D8-D15, thus combining the two 4732's into a 4K X 16 bit ROM. The MCB 6810P's are 128 X 8 bit static RAM and are used as a scratch pad by the CPU. In a manner similar to the 4732's the two 6810's are combined to form a 128 X 16 bit RAM. One slight difference from the 4732's is that the 6810's are addressed by address lines A8-A14.

The 9900 uses three control signals during operation of the external memory read and write to control the use of the address and data busses. These signals are DBN, -MEMEN, and -WE. During memory read, DBIN and -MEMEN are active, while -WE is not. The active signals allow an output onto the address buss indicating the disired memory lacation to be read. DBIN and -MEMEN are deactivate the data bus output.

FIGURE 1 - ARCHITECTURE

176

Figure 2. THE 9900 ARCHITECTURE

Fig. 3

.

#### Product Data Book

## TMS 9900 ARCHITECTURE

#### 2.8 TMS 9900 PIN DESCRIPTION

معر Table 2 defines the TMS 9900 pin assignments and describes the function of each pin.

TABLE 2 THS 9900 PIN ASSIGNMENTS AND FUNCTIONS

| SIGNATURE  | PIN    | 1/0          | DESCRIPTION                                  |             |       | TMS                  | 9900 PIN ASSIGNA | AENTS           |            |

|------------|--------|--------------|----------------------------------------------|-------------|-------|----------------------|------------------|-----------------|------------|

|            | 1      | i            | ADORESS BUS                                  | Vas         | 1     | 5                    |                  | E 54            | FOLD       |

| AO (MSB)   | 24     | ουτ          | A0 through A14 comprise the address bus.     | Vcc         |       |                      | 2                | E 63            | MEMEN      |

| A1         | 23     | i aur        | This 3-state bus provides the memory-        | WAIT        | 3     | =                    |                  | 62              | READY      |

| A2         | 22     | , <b>OUT</b> | activess vector to the external-memory       | LOAD        | 4     |                      |                  | 61              | ne -       |

| 22         | 21     | דטס          | system when MEMEN is acove and I/O-bit       | HCLDA       | 5     |                      |                  | 20              | CRUCLX     |

| A4         | 20     |              | addresses and external-instruction addresses | RESET       | 6     | 1                    |                  | 53              | Vcc        |

| 24         | 19     | out          | to the I/O system when MEMEN is inactive.    | IAO         | 7     | 1                    |                  | 53              | NC ·       |

| A5         | 18     | OUL          | The address bus assumes the high-impedance   | <b>#1</b>   |       | 1                    |                  | 57              | NC +       |

| A7         | 17     | OUT          | state when HOLDA is active.                  | •2          | 9     | 1                    |                  | 2 25            | D15        |

| 84         | 16     |              |                                              | A14         |       |                      |                  | <b>55</b>       | 014        |

| A9         | 15     | , •••        |                                              |             |       | 1                    |                  | Ця              | 013        |

| AIG        |        | יטס          |                                              |             |       |                      |                  | <b>53</b>       |            |

| A11        | 13     | , cr.        |                                              |             |       |                      |                  | 52              |            |

| A12        | 1      | OUT          |                                              |             |       |                      |                  | 51              |            |

| A13        | 11     | OUT          | 1                                            | 84          |       |                      |                  | 50              | 09         |

| A14 (LS8)  | 10     | out          | 5<br>}                                       | 84          |       |                      |                  | <b>49</b>       | D6         |

|            | i      | •            | DATA BUS                                     |             |       |                      |                  | <u>C</u> 4      | 07         |

| CO (MSa)   |        | :            | CATA BUS                                     |             |       |                      |                  | 547             | 26         |

| 01         | 42     |              | 3-state data bul. This bus transfers memory  |             | 2     |                      |                  |                 | <b>C</b> 5 |

| 02         | 43     |              | • • • • • • • • • • • • • • • •              | -           |       | $\tilde{\mathbf{z}}$ |                  |                 | 04         |

| 53         | 1      | ; 1/0        | reacine) the external-memory system when     |             |       |                      |                  |                 | 3          |

| C4         | 45     | : :/0        | MEMEN is active. The cata bus assumes the    |             | 2 21  | $\simeq$             |                  | 100             | 02<br>D1   |

| 05         | 45     | 1/0          | mon-mpedance state when HOLDA is             |             |       | $\geq$               |                  |                 | 20         |

| 26         | 47     | 1/0          |                                              |             |       | $\geq$               |                  | ( <del></del> . | vss<br>Vss |

| 07         | 48     | 01           |                                              |             |       | $\Xi$                |                  | Ĩ,              | NC NC      |

| CS         | 49     | 1/0          |                                              | Voo         |       |                      |                  | <b>E</b> 3      | NC         |

| C9         | 50     | 1/0          |                                              |             | 2     |                      |                  | C 37            | NC         |

| 010        | 51     | 10           | •<br>•<br>•                                  | DBIN        |       | <u></u>              |                  | <b>C</b> 38     | 100        |

| 011        | 52     | 1/0          | 5                                            | CRUOUT      | 34    | s 🗄                  |                  | 23              | 101        |

| 012        | 53     | 1/0          | \$<br>1                                      | CRUIN       | 1 31  |                      |                  | 234             |            |

| 013        | 54     | 1/0          |                                              | INTREC      | 1 2   |                      |                  | 23              | 103        |

| 014 .      | 55     | 1/0          | ł                                            |             |       | _                    |                  |                 |            |

| 015 (158)  | 15     | 1/0          | ŧ                                            |             |       |                      |                  |                 |            |

|            | 1      |              | !                                            | C - Ne in   | 12.87 | <b>1</b> 91 ctt      | mertion.         |                 |            |

|            | ł      | !            | POWER SUPPLIES                               |             |       |                      |                  |                 |            |

| VIS        | 1      | 1            | Supply voltage (-5 V NCM)                    |             |       |                      |                  |                 |            |

| ¥cc        | ' 2,59 | •            | Suddy voltage IS V NOMI, Pirs 2 and 59 m     | 1457 De con | med   | ted 10               | Baraties.        |                 |            |

| Y00        | 27     | 1            | Sucory voltage (12 V NOM)                    |             |       |                      |                  |                 |            |

| VSS        | 25,40  | 1            | Ground reterence. Pins 15 and 40 must be o   |             | n 5   | arzilei,             |                  |                 |            |

|            | ł      | :            | CLOCXS                                       |             |       |                      |                  |                 |            |

| <b>21</b>  | 1 S    | IN           | Phase-1 clock                                |             |       |                      |                  |                 |            |

| 32         | 9      | 1 JN         | , Plase? sloc=                               |             |       |                      |                  |                 |            |

| <b>e</b> 3 | 28     | - 1%         | Phase 3 clock                                |             |       |                      |                  |                 |            |

| -          | 1 25   | IN           | Phase-4 docs                                 |             |       |                      |                  |                 |            |

Fig. 4

. . .

## TMS 9900 ARCHITECTURE

| SIGNATURE | PIN | vo  | DESCRIPTION                                                                                                                                |

|-----------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------|

|           |     |     | BUS CONTROL                                                                                                                                |

| DBIN      | 29  | 007 | Data bus in. When active (high), DBIN indicates that the TMS 9900 has disabled its output buffers to                                       |

|           |     |     | slow the memory to place memory-read data on the data but during MEMEN. DBIN remains low if                                                |

|           |     |     | all other cases except when HQLDA is active.                                                                                               |

| MEMEN     | ස   | CUT | Memory enable. When active flow), MEMEN indicates that the address bus contains a memory address.                                          |

| NE        | 51  | OUT | Write enable. When active Ilow), WE indicates that memory write cate is available from the TMS 9900                                        |

| 12        |     | 001 | to be written into memory.                                                                                                                 |

|           |     |     |                                                                                                                                            |

| CRUCLK    | ಉ   | OUT | CRU clocx. When active (high), CRUCLK indicates that external interface logic should sample the                                            |

|           |     |     | -output data on CRUOUT or should decode external instructions on A0 through A2.                                                            |

| CRUIN     | 31  | IN  | CRU data in CRUIN, normally driven by 3-state or open-collector devices, receives input data from                                          |

|           |     |     | external interface logic. When the processor executes a STCR or TB instruction, it samples CRUIN for                                       |

|           |     |     | the level of the CRU input bit specifies by the address bus (A3 through A14),                                                              |

|           |     |     |                                                                                                                                            |

| CRUCUT    | 30  | 007 | CRU data out. Senal I/O data sporars on the CRUOUT line when an LDCR, SEC, or SEO instruction                                              |

|           |     |     | <ul> <li>is executed. The data on CRUOUT should be tampled by external I/O interface logic when CRUCL's<br/>goes active (high).</li> </ul> |

|           |     | ;   | INTERRUPT CONTROL                                                                                                                          |

| NTREO     | 32  | IN  | Interrupt request, When active Bowl, INTREQ indicates that an external interrupt is requested. I                                           |

|           | ł   | į ! | INTRED is active, the processor loads the cata on the interrupt-code-input lines ICO through IC3 inte                                      |

|           | 1   |     | the internal internuot-code-storage register. The code is compared to the internuot mask bits of in                                        |

|           | İ   |     | status register. If equal or higher priority than the enabled interrupt level linterrupt code equal or les                                 |

|           | 1   |     | then status register bits 12 through 15) the TNIS 9300 interrupt sequence is initiated, if th                                              |

|           | 1   |     | comparison fails, the processor ignores the request, INTREQ should remain active and the processo                                          |

|           |     |     | will continue to sample ICO through ICO until the program enables a sufficiently low priority to accept                                    |

|           |     |     | the request interrupt.                                                                                                                     |

| 100 (MSB) | 36  | IN  | Interrupt codes, ICD is the MSB of the interrupt code, which is sampled when INTEED is active. When                                        |

| ICT       | 35  | IN  | ICO through ICO are LLLH, the highest external-priority interrupt is being requested and when HintHh                                       |

| 102       | 34  | IN  | the lowest-priority interrupt is being requested.                                                                                          |

| 103 (LSB) | 33  | IN  |                                                                                                                                            |

|           |     | •   | MEMORY CONTROL                                                                                                                             |

| HOLD      | 64  | IN  | Hold, When active (low), HOLD indicates to the processor that an external controller (e.g., DM.                                            |

|           | 1   |     | dence) desires to utilize the address and data buses to transfer data to or from memory. Th                                                |

|           | 1   |     | TMS 2900 enters the hold state following a hold signal when it has completed its present memor                                             |

|           | 1   | 1 1 | cycle." The processor then praces the address and cata buses in the high-imbedance state (along will                                       |

|           |     |     | WE, MEMEN, and DSIN) and responds with a hold-acknowledge signal (HOLDAI, When HOLD removed, the processor returns to normal operation.    |

|           |     |     | •                                                                                                                                          |

| HOLDA     | 5   | CUT | Hold acknowledge. When active [high], HOLDA indicates that the processor is in the hold state an                                           |

|           |     |     | the accress and data buses and memory control outputs IWE, MEMEN, and DEINI are in th                                                      |

|           | ł   |     | high-impedance state.                                                                                                                      |

| READY     | 62  | IN  | Ready, When active (high), READY indicates that memory will be ready to read or write during th                                            |

|           | l   |     | next clock cycle. When not-ready is indicated during a memory operation, the TMS 9900 enters a wa                                          |

|           |     |     | state and suspends internal operation until the memory systems indicate ready.                                                             |

| TIAW      | 3   | CUT | Wait, When active (high), WAIT indicates that the TMS 9950 has entered a west state Secause of                                             |

| TAL       | 1 3 |     | nature active inight, mart indicates the the the sous here to a work sure accuse of<br>natureacy condition from memory.                    |

"If the cycle following the present memory cycle is also a memory cycle, it, too, a completed before the TMSB900 enters the hold state. The measurem number of consecutive memory cycles is three.

Fig. 4 (continued)

#### **Product Data Book**

# TMS 9900 ARCHITECTURE

| TABLE 2 (CONCLUDED) |     |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|---------------------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SIGNATURE           | PIN | 1/0 | OF SCHIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                     |     |     | YIMING AND CONTILOL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| IAG                 | 7   | our | Instruction acquisition, TAO is active litight during any memory cycle when the TMS 9900 is acquiring an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|                     |     |     | Instruction, IAO can be usual to detect alogal op codes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| LOAD                | 4   | IN  | I part. When active thous, $\overline{10000}$ causes the TMS 0000 to execute a nonmarkable Interrupt with memory address FTFC <sub>16</sub> containing the trap vector tWP and PCD. The toad sequence begins after the instruction being concuted to complete $\overline{10000}$ to the trap of PCD. The toad sequence begins after the instruction being concuted to complete $\overline{10000}$ will also terminate an life state. If EOAD is active during the time RESET is released, then the TOAD trap vector after the THESET function is completed. TOAD should remain active for one instruction period. TAO can be used to determine the instruction boundaries. This signal can be used to indicate the instruction is can be undernead outlines can be used to determine to the state. It is undernead outlines to be the fourtee to be the instruction is control. TAO and to determine the instruction is can be used to determine to the panel outlines the state of the panel outlines and the panel outlines and to determine the state of the panel outlines to be the state of the panel outlines and to determine the total state outlines to be underlined outlines to be the state of the panel outlines and to determine the state outlines can be underlined outlines to be the panel outlines and software control coutines to control the panel outlines and software control coutines to control the panel outlines and to determine the state. |  |  |  |

| TIF SE F            | 6   | IN  | Heave When active Bowl, HESET raises the processor to be reset and Johlblis WE and CRUCLK: When<br>RESET is released, the TMS 9/00 then initiates a level zero Interrupt sequence that acquires WP and PC<br>from locations 0000 and 0(8)2, sets all status register birs to zero, and starts execution. RESET will also<br>terminate an life state. At 5CT must be tiefd active for a minimum of three clock cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

2

FIGURE 2 - MEMORY MAP

.

Three internal registers are accessible to the user. The program counter (PC) contains the address of the instruction following the current instruction being executed. This address is referenced by the processor to fatch the next instruction from memory and is then automatically incremented. The status register (ST) contains the processor to fatch the processor and will be further defined in Section 3.4. The workspace pointer (WP) contains the address of the first word in the currently active set of workspace registers.

A workspace-register file occupies 16 contiguous memory words in the general memory area (see Figure 2). Each workspace register may hold data or addresses and function as operand registers, accumulators, address registers, or

Drivers are deactivated to prevent the input data from conflicting with output data. Memory write makes use of -MEMEN also -WE both active, and DBIN deactivated. Under these conditions the 9900 ouputs on the address and data busses and holds these outputs for the duration required by RAM.

#### CRU ALLOCATION

Of the available 4K of CRU bits, the first 1K (addresses 0000-07FE) are used internally in the Home Computer. The second 1K (adresses 0800-0FFE) are reserved for future use. The last 2K (addresses 1000-1FFE) are reserved for the peripherals to be plugged in the I/O port. A block of 128 CRU bits is assigned to each peripheral as listed below.

.

#### CRU ASSIGNMENTS

| CRU<br>ADDRESSES                                                                                                                            | A3                                                  | A4                                                       | A5                                             | A6                                        | A7                                                  | USE                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------|------------------------------------------------|-------------------------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0000-0FFE<br>1000-10FE<br>1100-11FE<br>1200-12FE<br>1300-13FE<br>1400-14FE<br>1500-15FE<br>1600-16FE<br>1700-17FE<br>1800-18FE<br>1900-1FFE | 0<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | X<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>1<br>1 | X<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>0<br>X | X<br>0<br>1<br>1<br>0<br>1<br>1<br>0<br>X | X<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>X | INTERNAL USE<br>RESERVED<br>DISK CONTROLLER<br>RESERVED<br>RS 232 (I)<br>RESERVED<br>RS 232 (11)<br>RESERVED<br>RESERVED<br>THERMAL PRINTER<br>FUTURE EXPANSION |

#### INTERRUPT HANDLING

The interrupt available on the I/O port is one of the maskable interrupts of the TMS 9901 Programmable Systems Interface.

#### 9900 INTERRUPTS

| INTERRUPT<br>LEVEL                 | VECTOR LOC.<br>(MEMORY ADDR.<br>IN HEX) | CPU<br>PIN            | DEVICE<br>ASSIGNMENT            |

|------------------------------------|-----------------------------------------|-----------------------|---------------------------------|

| (High<br>est O<br>Prior- 1<br>ity) | 0000<br>FFFC<br>0004                    | RESET<br>LOAD<br>INT1 | RESET<br>LOAD<br>EXT DEV (9901) |

Lower priority CPU interrupt are not used. The additional interrupts available are implemented on 9901.

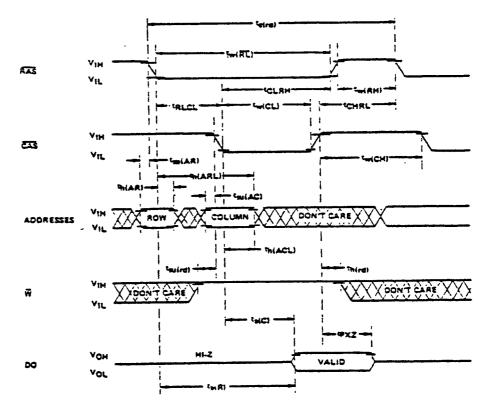

MEMONY READ CYCLE TIMING

25

REMONY WRISE CYCLE TIMING.

Fig.

თ

3

MEMONY-READ CYCE TIMING WITH ONLE WAIT STATE

Fig.

-

Dinecs MENONY Access Timing

2

SO.

о 11

CAU INITERFACE TIMING.

.

.

e1 01 63 34 CAU HIT ADDRESS . CRU ADDRESS m UNKNOWN CAU ADOMESS . + 1 A0 A15 CAUCLE OUTPUT CHUDATA OUT . CRUDATA OUT . + I UNKNOWH UNKNOWN CAUGUI XXX THOIFT CARE XXX INPUT VALID INPUT DIE M COU INPUT CAU OU FPUT

Fig.

ы

3

۰.

# TABLE 1. SUMMARY OF 9900 MICROPROCESSOR INSTRUCTIONS

.

.

.

.

| Mnemonic | Instruction Code Description      |

|----------|-----------------------------------|

| A        | Add Words                         |

| AB       | Add Bytes                         |

| ABS      | Absolute Value                    |

| AI       | Add Immediate                     |

| ANDI     | AND Immediate                     |

| В        | Branch                            |

| BL       | Branch and Link                   |

| BLWP     | Branch and Load Workspace Pointer |

| С        | Compare Words                     |

| СВ       | Compare Bytes                     |

| CI       | Compare Immediate                 |

| CKOF     | Clock Off (control instruction)   |

| CKCN     | Clock On (control instruction)    |

| CLR      | ÇLEAR                             |

| 000      | Compare Ones Corresponding        |

| CZC      | Compare Zeroes Corresponding      |

| DEC      | Decrement                         |

| DECT     | Decrement By Two                  |

| DIV      | Divide                            |

| IDLE     | Idle (control instruction)        |

| INC      | Increment                         |

| INCT     | Increment By TWO                  |

| INV      | Invert                            |

.

21

# SUMMARY OF 9900 MICROPROCESSOR INSTRUCTIONS (CONTINUED)

.

۶

| Mnemonic | Instruction code Description             |

|----------|------------------------------------------|

| JEQ      | Jump If Equal to                         |

| JGT      | Jump If Greater Than                     |

| JH       | Jump If Greater Than (Logic)             |

| JHE      | Jump If Greater Than Or Equal To (Logic) |

| JL       | Jump If Less Than                        |

| JLE .    | Jump If Less Than Or Equal To (Lcgic)    |

| JLT      | Jump If Less Than                        |

| JMP      | Unconditioned Jump                       |

| JNC      | Jump If No Carry                         |

| JNE      | Jump If Not Equal                        |

| JNO      | Jump If No Overflow                      |

| JOC      | Jump On Carry                            |

| JOP      | Jump On Odd Parity                       |

| LDCR     | Load <u>CRU</u>                          |

| LI       | Load Immediate                           |

| LIMI     | Load Interrupt Mask Immediate            |

| LREX     | Restart (control instruction)            |

| LWPI     | Load Workspace Pointer Immediate         |

| MOV      | Move (word)                              |

| MOVB     | Move Syte                                |

| MPY      | Multiply                                 |

| NEG      | Negative                                 |

| ORI      | OR Immediate                             |

| RSET     | Reset (control instruction)              |

i.

# -SUMMARY OF 9900 MICROPROCESSOR INSTRUCTIONS (continued)

.

| Mnemonic | Instruction Code Description      |

|----------|-----------------------------------|

| RTWP     | Return With Workspace Pointer     |

| S.       | Subtract Words                    |

| SB       | Subtract Bytes                    |

| SBO      | Set Bit To Logic One              |

| SBZ      | Set Bit To Logic Zero             |

| SETO     | Set To One                        |

| SLA      | Shift Left Arithmetic             |

| SOC      | Set One Corresponding             |

| SOCB     | Set Ones Corresponding            |

| SRA      | Shift Right Arithmetic            |

| SRC      | Shift Right Circular              |

| SRL      | Shift Right Logical               |

| STCR     | Store CRU                         |

| STST     | Store Status                      |

| STWP     | Store Workspace Pointer           |

| SWPB     | Swap Bytes                        |

| SZC      | Set To Zeroes Corresponding       |

| SZCB     | Set To Zeroes Corresponding Bytes |

| ТВ       | Test Bit                          |

| Χ.       | Execute                           |

| XOP      | Extended Operation                |

| XOR      | Exclusive OR                      |

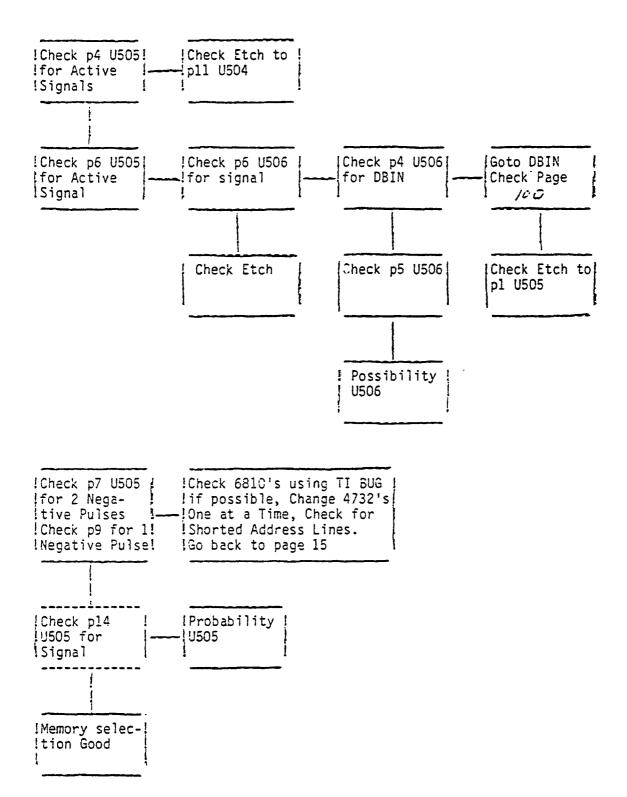

#### MEMORY SELECTION LOGIC

### GENERAL DESCRIPTION

#### -----

The memory selection logic decodes the more significant address lines for selecting fast ROM and RAM memory. Also the output of the decoder is used for a second decoder, which selects internal devices such as VDP, sound etc...

#### HARDWARE DESCRIPTION

The schematics of the memory selection logic with a memory map is given in figure  $H_1$ ,  $\rho \cdot 35$ . When MEMEN is active, U504 (74LS138) decodes the three most significant address lines AO through A3, dividing the address space in the following 8 blocks of 8 bytes.

#### BLOCK 0

Memory Block 0 (>0000->1FFF) is used to select the system read only memory (ROM).

#### BLOCK 1

Memory Block 1 (>2000->3FFF) is reserved for memory expansion.

#### BLOCK 2

Memory Block 2 (>4000->5FFF) is used to select read only memory in external devices, such as RS232 interface. The ROM in these devices contains the device service routine (MBE).

#### BLOCK 3

Memory block 3 (>6000->7FFF) is used for the optional read only memory in solid state software command modules (ROMG).

#### BLOCK 4

Memory block 4 (>8000->9FFF) is used divided in several parts. Memory locations > 8000 to >83FF are used for the fast system read-and-write memory. This further decoding of the address space is done in or-gates U507. This part of the circuitry also generate the RAMBLK signed, which is used to select the TMS 9901 programmable system interface. Furthermore the MB4 signal is used to select a second 74LS138 which divides memory block 4 in more parts.

#### BLOCK 5, 6 AND 7

These blocks are used along with Block 1 for memory expansion.

#### START SIGNAL

By combining the CSRAM and ROMEN signals, together with MEMEN in NAND-gate U606 and OR-gate U605 the START signal is developed. This signal is used in the al6 to 8 bit interfacing circuit.

۰.

| SIGNAL | ADDRESSED MEMORY LOCATION | USE                        |

|--------|---------------------------|----------------------------|

| ROMEN  | 0000 - 1FFF               | SYSTEM ROM SELECT          |

| MBE    | 4000 - 5FFF               | EXT. DEVICE ROM SELECT     |