As you are now the owner of this document which should have come to you for free, please consider making a donation of £1 or more for the upkeep of the (Radar) website which holds this document. I give my time for free, but it costs me money to bring this document to you. You can donate here <u>https://blunham.com/Misc/Texas</u>

Many thanks.

Please do not upload this copyright pdf document to any other website. Breach of copyright may result in a criminal conviction.

This Acrobat document was generated by me, Colin Hinson, from a document held by me. I requested permission to publish this from Texas Instruments (twice) but received no reply. It is presented here (for free) and this pdf version of the document is my copyright in much the same way as a photograph would be. If you believe the document to be under other copyright, please contact me.

The document should have been downloaded from my website <u>https://blunham.com/</u>, or any mirror site named on that site. If you downloaded it from elsewhere, please let me know (particularly if you were charged for it). You can contact me via my Genuki email page: <u>https://www.genuki.org.uk/big/eng/YKS/various?recipient=colin</u>

You may not copy the file for onward transmission of the data nor attempt to make monetary gain by the use of these files. If you want someone else to have a copy of the file, point them at the website. (<u>https://blunham.com/Misc/Texas</u>). Please do not point them at the file itself as it may move or the site may be updated.

It should be noted that most of the pages are identifiable as having been processed by me.

If you find missing pages, pages in the wrong order, anything else wrong with the file or simply want to make a comment, please drop me a line (see above).

It is my hope that you find the file of use to you.

Colin Hinson In the village of Blunham, Bedfordshire.

I put a lot of time into producing these files which is why you are met with this page when you open the file.

The Engineering Staff of TEXAS INSTRUMENTS INCORPORATED Semiconductor Group

# SBP 9900 A SYSTEMS DEVELOPMENT MANUAL

**AUGUST 1978**

The Engineering Staff of TEXAS INSTRUMENTS INCORPORATED Semiconductor Group

AUGUST 1978

PRELIMINARY RELEASE

(Review Copy)

# **TEXAS INSTRUMENTS**

INCORPORATED

#### PREFACE

This SBP 9900A System Development Manual is intended to guide the design engineer in the specification, design, and implementation of an SBP 9900A based microprocessor system. This manual describes the SBP 9900A's general system level operation; and contains interfacing details, suggested hardware configurations, power source considerations, and electrical requirements. The reader is assumed to be familiar with the SBP 9900A instruction set and architecture as described in: 1) section three of the *Bipolar Microcomputer Components Data Book*, [as supplemented by the information contained in Appendix A of this manual] and 2) the *Model 990 Computer, Assembly Language Programmer's Guide*. Also, the information contained in the 990 Computer Family System Handbook will be useful as a supplement to the systems description provided herein. These documents are available from your Texas Instruments sales representative.

#### **IMPORTANT NOTICES**

Texas Instruments reserves the right to make changes at any time in order to improve design and to supply the best product possible.

TI cannot assume any responsibility for any circuits shown or represent that they are free from patent infringement.

Copyright © 1978 Texas Instruments Incorporated

Post Office Box 1443 Houston, Texas 77001

# **TABLE OF CONTENTS**

# Paragraph

# Title

Page

# SECTION I. INTRODUCTION

| 1.1 | General Descri | iption . | <br>• • • • | . <i>.</i> | <br>            | <br> | <br> | <br>1-1 |

|-----|----------------|----------|-------------|------------|-----------------|------|------|---------|

| 1.2 | Key Features   |          | <br>••••    |            | <br>• • • • • • | <br> | <br> | <br>1-1 |

# SECTION II. SBP 9900A ARCHITECTURE

| 2.1   | Registers                                                             | 2-1  |

|-------|-----------------------------------------------------------------------|------|

| 2.1.1 | Workspace-Pointer (WP) Register                                       | 2-2  |

| 2.1.2 | Workspace-Registers                                                   | 2-3  |

| 2.1.3 | Program-Counter (PC) Register                                         | 2-3  |

| 2.1.4 | Status Register (ST)                                                  | 2-3  |

| 2.2   | Memory-to-Memory Operators                                            | 2-4  |

| 2.3   | Bus Structures                                                        | 2-4  |

| 2.3.1 | Memory Bus                                                            |      |

| 2.3.2 | CRU Bus                                                               | 2-5  |

| 2.3.3 | Interrupt Bus                                                         | 2-5  |

| 2.4   | Context Switching                                                     | 2-6  |

| 2.5   | Machine Cycles                                                        | 2-7  |

| 2.5.1 | ALU Machine Cycles                                                    | 2-7  |

| 2.5.2 | Memory Read Machine Cycles                                            | 2-7  |

| 2.5.3 | Memory Write Machine Cycles                                           | 2-7  |

| 2.5.4 | CRU Output Machine Cycles                                             | 2-7  |

| 2.5.5 | CRU Input Machine Cycles                                              | 2-7  |

| 2.5.6 | Instruction Execution Examples                                        | 2-7  |

| 2.6   | Machine Cycle Min/Max Limits; Maximum Latency to Enter the Hold State | 2-9  |

| 2.7   | Cycles End "CYCEND" Signal                                            | 2-10 |

# SECTION III. MEMORY

| 3.1   | Memory Organization                                   |      |

|-------|-------------------------------------------------------|------|

| 3.1.1 | RESET Transfer Vectors                                |      |

| 3.1.2 | Hardware Interrupt Transfer Vectors                   |      |

| 3.1.3 | XOP Instructions: Software Interrupt Transfer Vectors |      |

| 3.1.4 | LOAD Transfer Vectors                                 | 3-3  |

| 3.1.5 | Transfer Vector Storage Requirements                  |      |

| 3.2   | Memory Control                                        |      |

| 3.2.1 | Memory Read Cycle                                     |      |

| 3.2.2 | Memory Write Cycle                                    |      |

| 3.2.3 | Read/Write Control with DBIN                          |      |

| 3.2.4 | Slow Memory                                           |      |

| 3.2.5 | Memory Access-Time Calculation                        |      |

| 3.2.6 | Wait State Calculation                                | 3-16 |

|       |                                                       |      |

# TABLE OF CONTENTS (Continued)

# Paragraph

## Title

| 3.3   | Static Memory                    |

|-------|----------------------------------|

| 3.3.1 | Static Fixed Memory              |

| 3.3.2 | Static Memory Timing and Loading |

| 3.4   | Other Memories                   |

| 3.5   | Memory Parity                    |

| 3.6   | Direct Memory Access             |

| 3.6.1 | , HOLD/HOLDA Block DMA           |

| 3.6.2 | Clock-Stopped Block DMA 3-23     |

| 3.6.3 | Transparent DMA                  |

| 3.7   | Memory Layout                    |

# SECTION IV. INTERRUPTS

| 4.1   | <b>RESET</b>                     |

|-------|----------------------------------|

| 4-2   | <u>LOAD</u> 4-2                  |

| 4.3   | Maskable Interrupts 4-3          |

| 4.3.1 | Interrupt Service                |

| 4.3.2 | Interrupt Signals                |

| 4.3.3 | Interrupt Masking                |

| 4.3.4 | Interrupt Processing Example 4-7 |

# SECTION V. INPUT/OUTPUT

| 5.1   | Direct Memory Access                   | . 5-1 |

|-------|----------------------------------------|-------|

| 5.2   | Memory Mapped I/O                      | . 5-1 |

| 5.3   | Communications Register Unit (CRU)     |       |

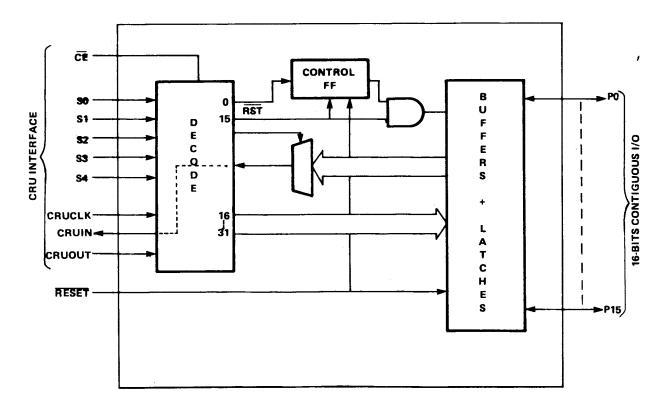

| 5.3.1 | CRU Interface                          | . 5-4 |

| 5.3.2 | CRU Machine Cycles                     |       |

| 5.3.3 | CRU Data Transfer                      | . 5-4 |

| 5.3.4 | CRU Interface Logic                    | . 5-8 |

| 5.4   | I <sup>2</sup> L CRU-Based Peripheral  | 5-10  |

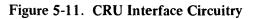

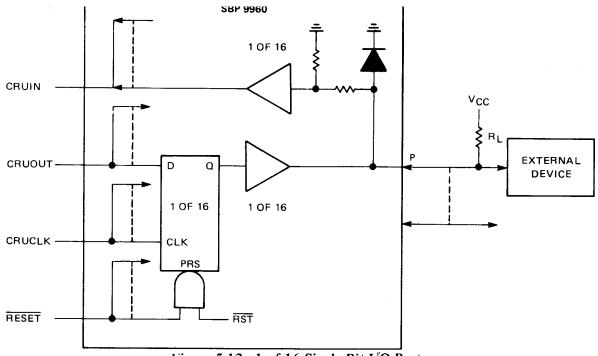

| 5.4.1 | SBP 9960 Programmable CRU I/O Expander | 5-10  |

| 5.4.2 | SBP 9961 Interrupt-Controller/Timer    | 5-19  |

| 5.5   | Software — UART                        |       |

| 5.6   | I <sup>2</sup> L Microprocessor System | 5-33  |

# SECTION VI. AUXILIARY SYSTEM FUNCTIONS

| 6.1   | Unused OP Codes           | 6-1 |

|-------|---------------------------|-----|

| 6.1.1 | Unused OP Code Detection  | 6-1 |

| 6.1.2 | Unused OP Code Processing | 6-1 |

| 6.2   | Software Front Panel      | 6-2 |

| 6.2.1 | Memory Requirements       | 6-3 |

| 6.2.2 | Description of Operation  | 6-3 |

# **TABLE OF CONTENTS (Continued)**

# Paragraph

# Title

| 6.3   | Software Examples            | 7 |

|-------|------------------------------|---|

| 6.3.1 | Signed Multiply Routine      | 7 |

| 6.3.2 | Signed Divide Routine        | 7 |

| 6.3.3 | Interger Square Root Routine | 7 |

# SECTION VII. POWER SOURCE CONSIDERATIONS

| 7.1   | I <sup>2</sup> L Operations                                    | 7-1  |

|-------|----------------------------------------------------------------|------|

| 7.1.1 | I <sup>2</sup> L Current Utilization                           | 7-1  |

| 7.1.2 | Current Steering Control                                       | 7-1  |

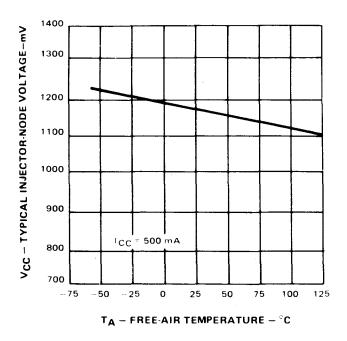

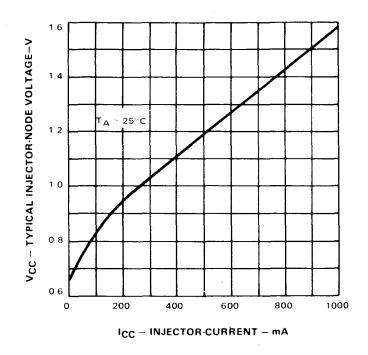

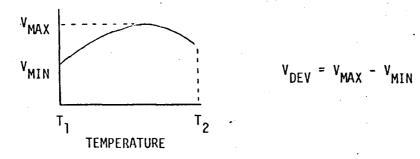

| 7.2   | Node Voltage (VINJ) Variations, Supply Current (INJ) Terminals | 7-4  |

| 7.3   | SBP 9900A Registor Current Supply                              | 7-7  |

| 7.3.1 | Temperature Effects on the Resistance of "R"                   | 7-9  |

| 7.3.2 | Calculations for RON                                           | 7-9  |

| 7.3.4 | Register Power Dissipation at Elevated Temperatures            | 7-11 |

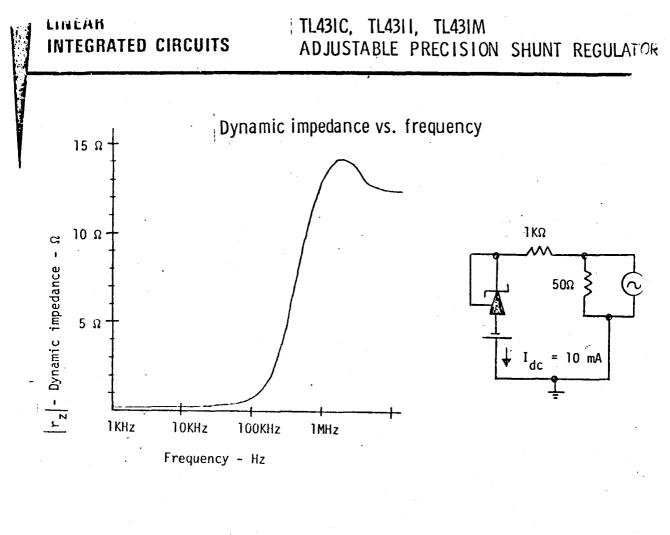

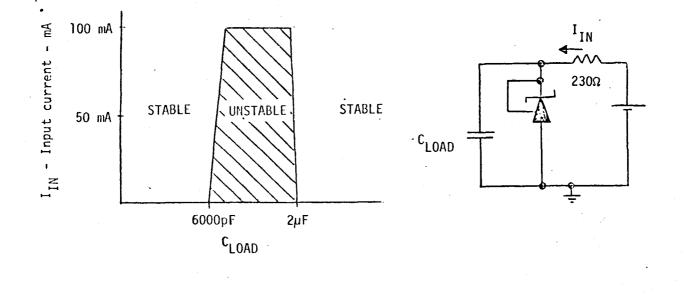

| 7.4   | TL061M Feedback Regulated Current                              | 7-11 |

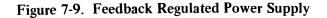

| 7.5   | LM117 Feedback Regulated Current Supply                        | 7-12 |

# SECTION VIII. ELECTRICAL REQUIREMENTS

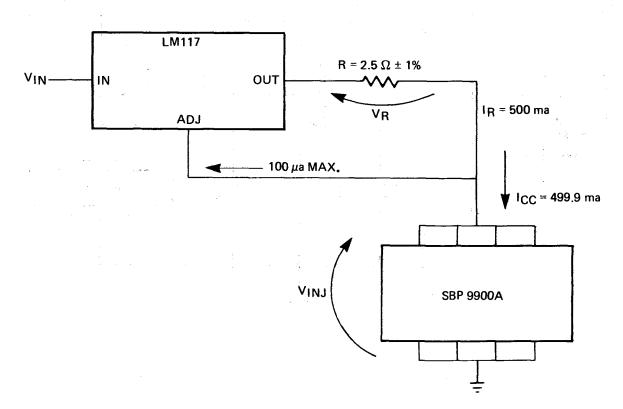

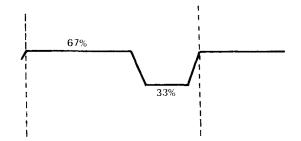

| 8.1   | SBP 9900A Clock Generation   | 8-1 |

|-------|------------------------------|-----|

| 8.1.1 | SBP 9900A Clock Generation   | 8-1 |

| 8.2   | SBP 9900A Signal Interfacing | 8-1 |

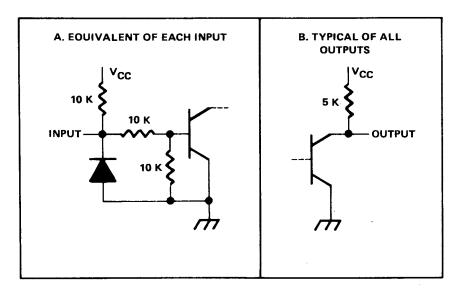

| 8.2.1 | Input Interfacing            | 8-5 |

| 8.2.2 | Output Interfacing           | 8-6 |

| 8.2.3 | Output Load Resistor Guide   | 8-6 |

# APPENDIXES

# Appendix

# Title

# Page

| SBP 9900A Specifications                  | A-1                                                                                                                                                                                                                                                                                         |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SBP 9900A Machine Cycles                  | B-1                                                                                                                                                                                                                                                                                         |

| SBP 9900A HI-REL Specifications           | C-1                                                                                                                                                                                                                                                                                         |

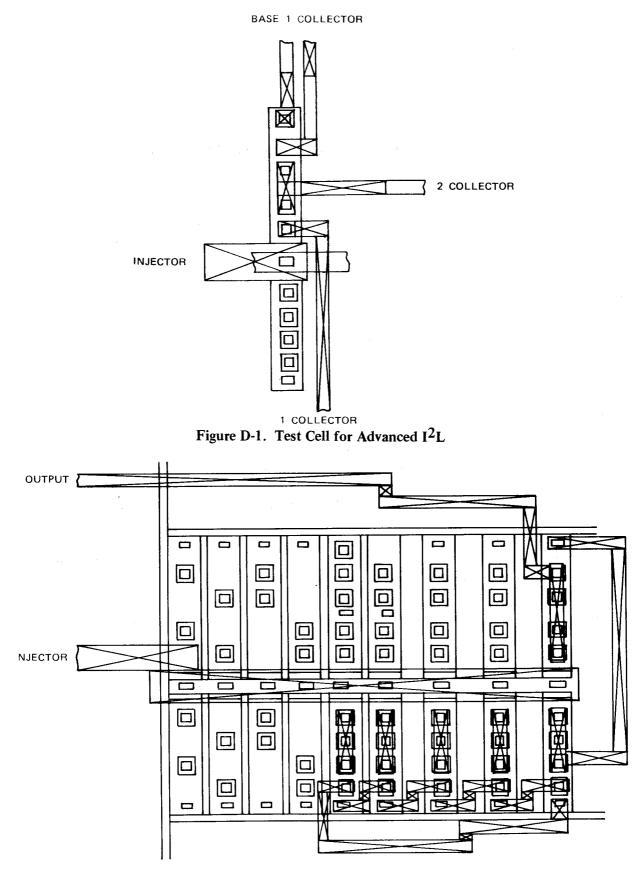

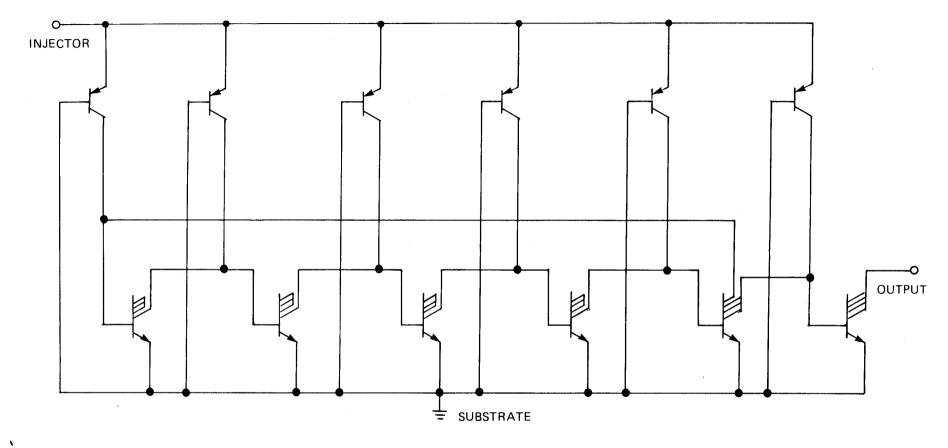

| Preliminary Radiation Test Results        | D-1                                                                                                                                                                                                                                                                                         |

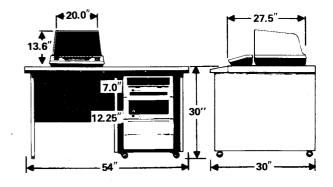

| Hardware/Software System Development Aids | E-1                                                                                                                                                                                                                                                                                         |

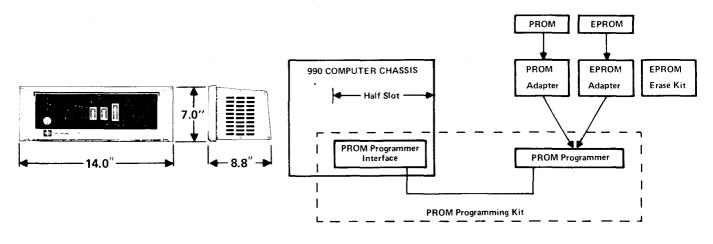

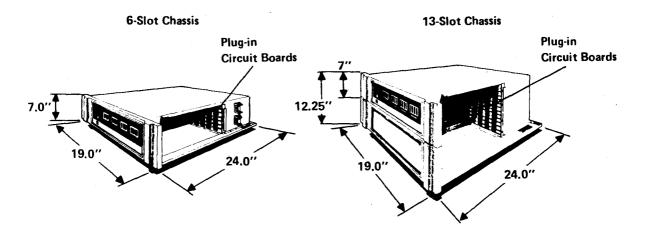

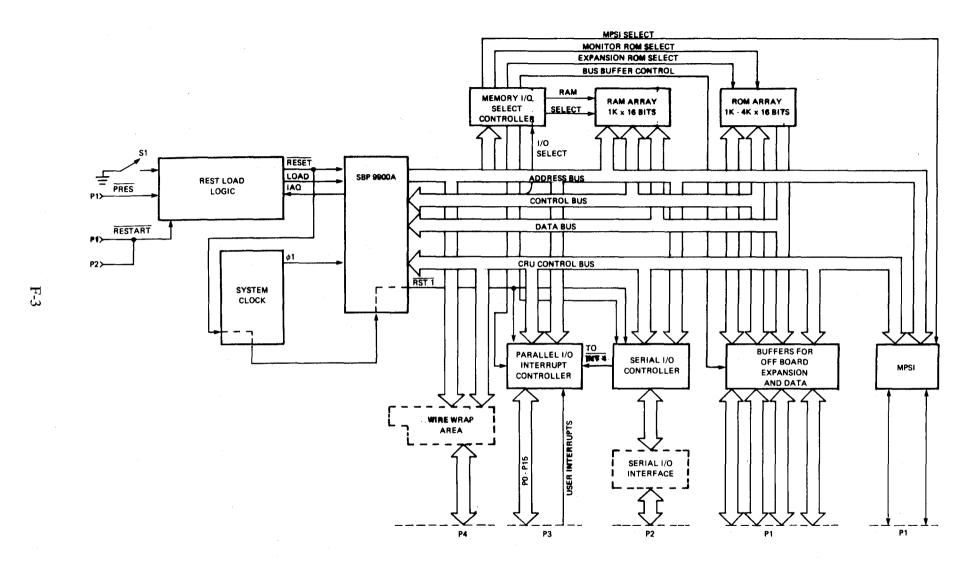

| SBP 9900A-Based TM 990/110M Microcomputer | F-1                                                                                                                                                                                                                                                                                         |

| Dynamic Memory                            | G-1                                                                                                                                                                                                                                                                                         |

| Data Sheets                               | H-1                                                                                                                                                                                                                                                                                         |

|                                           | SBP 9900A Specifications         SBP 9900A Machine Cycles         SBP 9900A HI-REL Specifications         Preliminary Radiation Test Results         Hardware/Software System Development Aids         SBP 9900A-Based TM 990/110M Microcomputer         Dynamic Memory         Data Sheets |

# LIST OF ILLUSTRATIONS

| Figure | Title                                                               | Page |

|--------|---------------------------------------------------------------------|------|

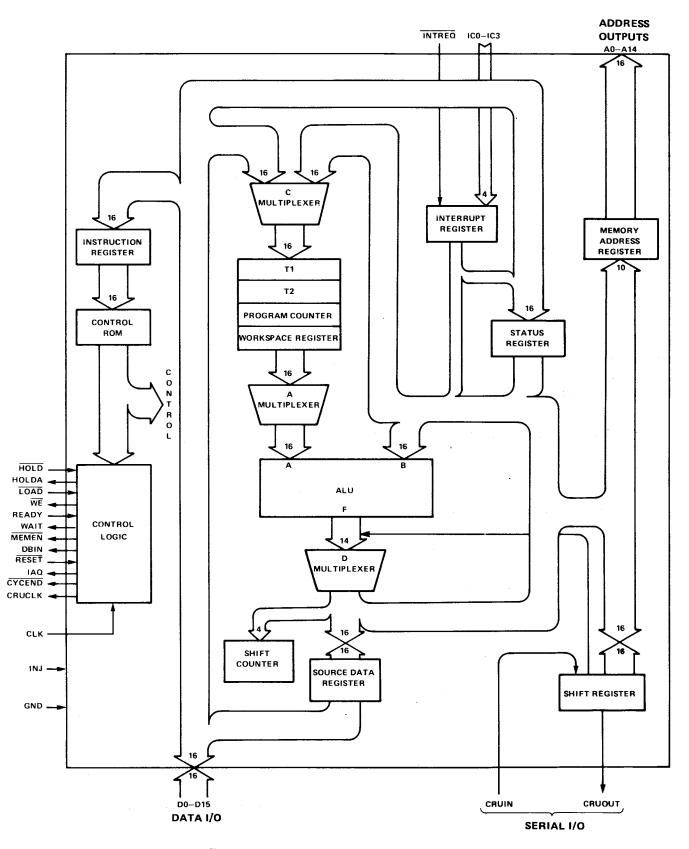

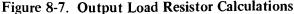

| 1-1    | SBP 9900A Architecture                                              |      |

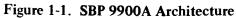

| 1-2    | SBP 9900A Functional Description                                    |      |

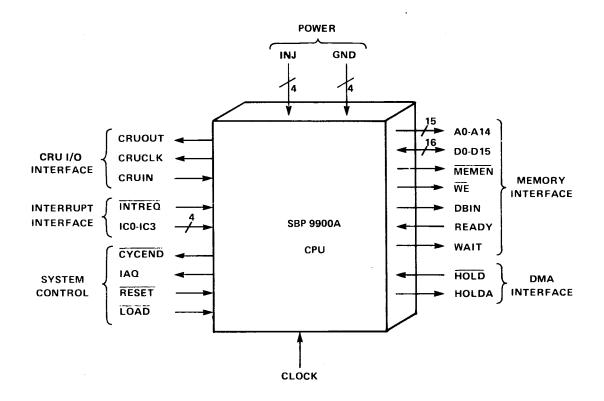

| 1-3    | SBP 9900A System                                                    |      |

| 2-1    | SBP 9900A Memory-to-Memory Architecture                             |      |

| 2-2    | Register Supporting Immediate SBP 9900A Program                     |      |

| 2-3    | SBP 9900A System Bus Structure                                      |      |

| 2-4    | SBO Instruction Machine Cycles                                      |      |

| 2-5    | STCR Instruction Machine Cycles                                     |      |

| 2-6    | RTWP Instruction Machine Cycles                                     |      |

| 2-7    | 'A' Instruction Machine Cycles                                      |      |

| 3-1    | Memory Bank Mapping Via CRU Bit                                     |      |

| 3-2    | SBP 9900A General Memory Map                                        |      |

| 3-3    | Timing for Three Back-to-Back Memory Read Cycles                    |      |

| 3-4    | Memory Write Cycle Timing                                           |      |

| 3-5    | READ/WRITE Generation                                               |      |

| 3-6    | Memory-Read Cycle Timing                                            |      |

| 3-7    | Write Memory Cycle Timing with One Wait State                       |      |

| 3-8    | Single Wait State for Slow Memory                                   |      |

| 3-9    | Double Wait States for Slow Memory                                  |      |

| 3-10   | Maximum Memory Accesses Time vs. RL, CL                             |      |

| 3-11   | SBP 9900A Buffered Memory System                                    |      |

| 3-12   | Memory Wait Time for Slow Memory                                    |      |

| 3-13   | Static Mixed Memory                                                 |      |

| 3-14   | Memory System Using SBP 9818 I <sup>2</sup> L ROM and TMS 40L45 RAM |      |

| 3-15   | Memory Parity Generator Checker                                     |      |

| 3-16   | HOLD/HOLDA Block DMA                                                | 3-22 |

| 3-17   | SBP 9900A Hold Timing                                               | 3-23 |

| 3-18   | Clock-Stopped Block DMA                                             | 3-24 |

| 3-19   | Transparent DMA                                                     |      |

| 4-1    | RESET Machine Cycles                                                | 4-1  |

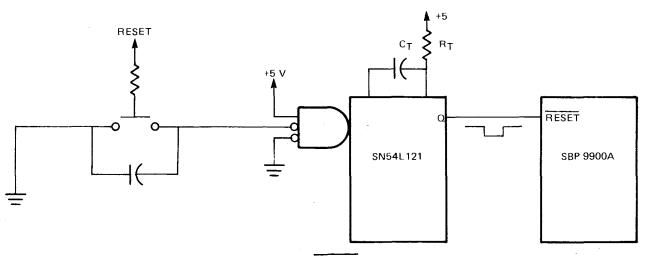

| 4-2    | RESET Generation                                                    | 4-2  |

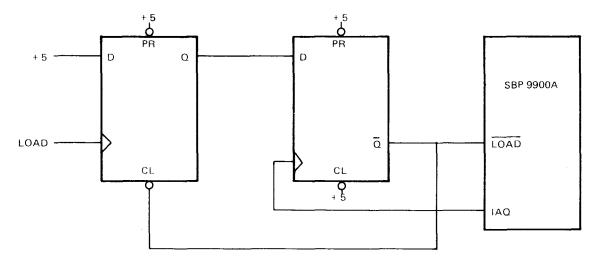

| 4-3    | LOAD Generation                                                     | 4-2  |

| 4-4    | LOAD Machine Cycle Sequence                                         | 4-3  |

| 4-5    | Interrupt Linkage                                                   | 4-4  |

| 4-6    | Interrupt Processing Machine Cycle Sequence                         | 4-4  |

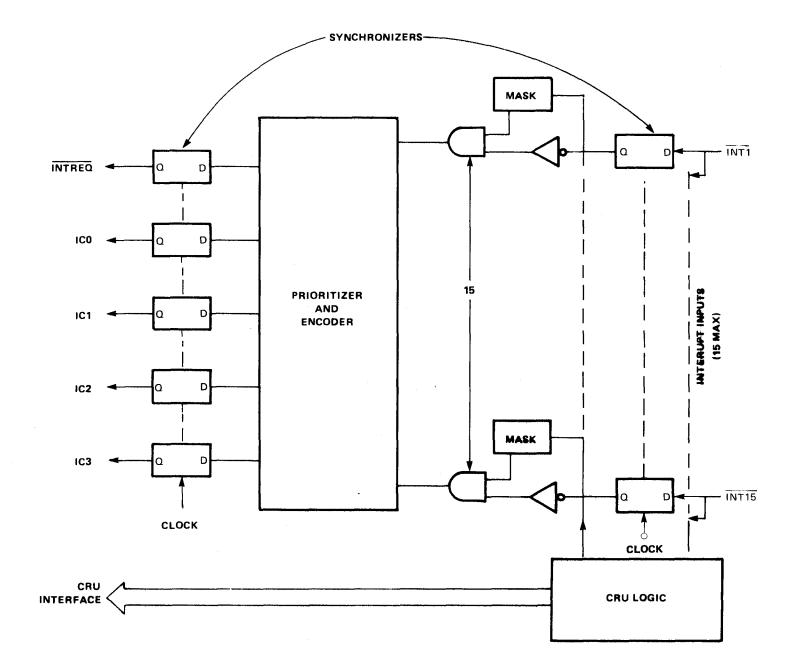

| 4-7    | Interrupt Control Logic                                             | 4-6  |

| 4-8    | Single Interrupt System                                             | 4-7  |

| 4-9    | LIMI Instructions                                                   | 4-7  |

| 5-1    | SBP 9900A I/O Capability                                            | 5-2  |

| 5-2    | SBP 9965 Memory Mapped I/O Interface                                | 5-3  |

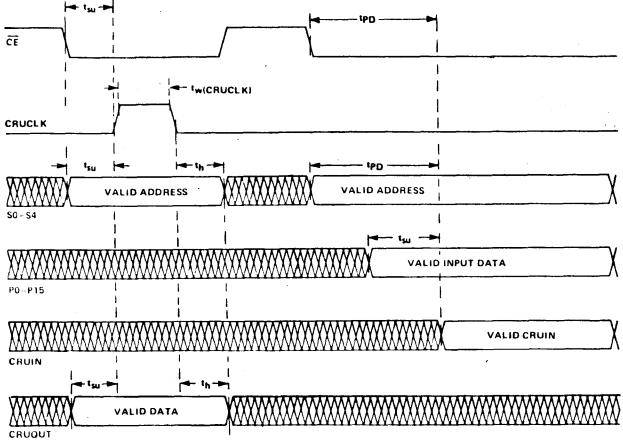

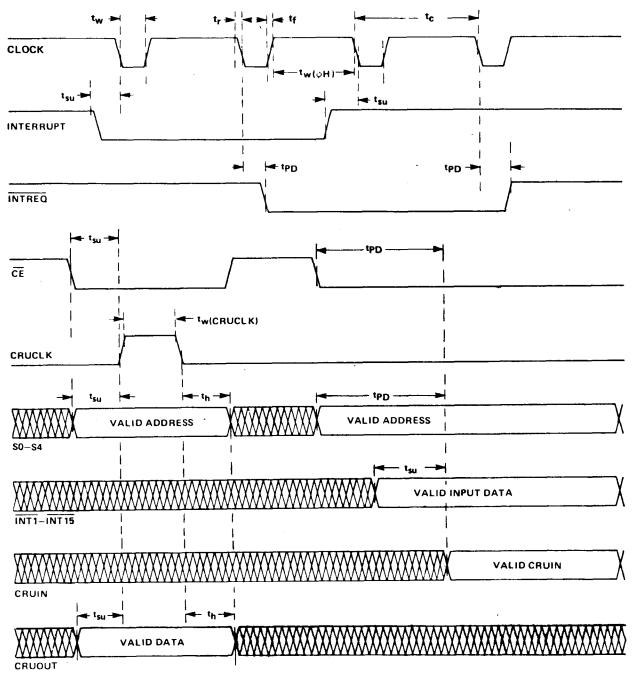

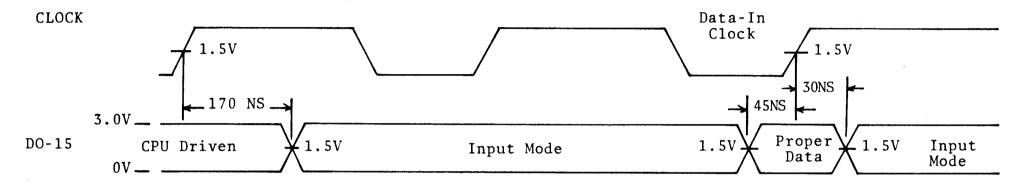

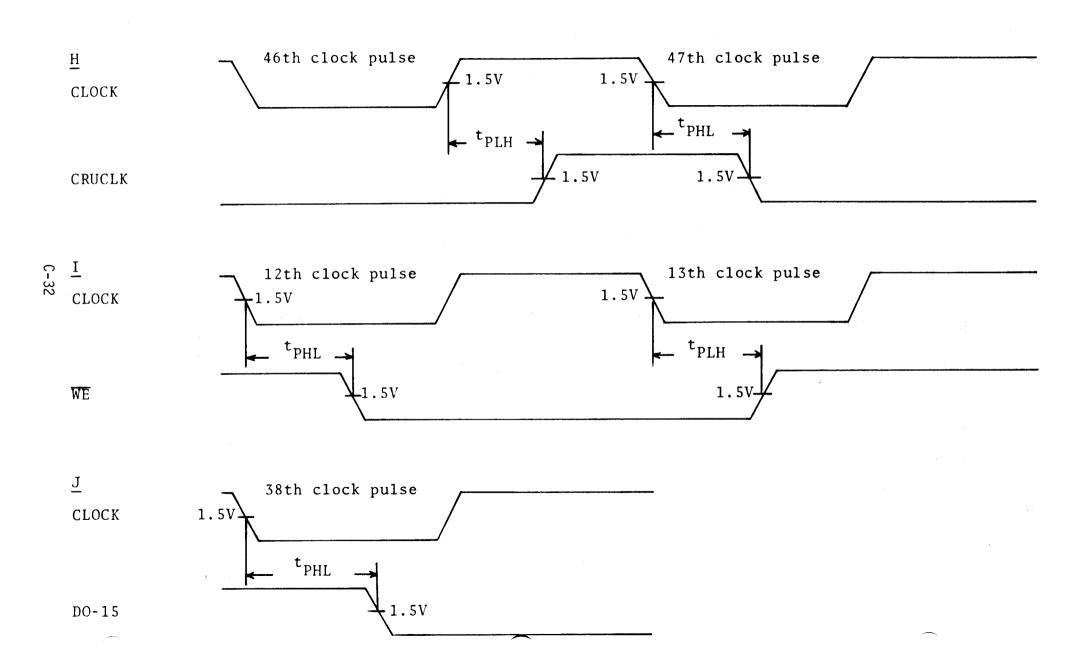

| 5-3    | CRU Output Machine Cycle Timing                                     | 5-5  |

| 5-4    | CRU Control Strobe Generation                                       | 5-5  |

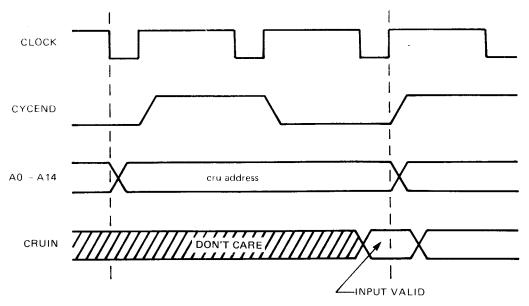

| 5-5    | CRU Input Machine Cycle Timing                                      |      |

# LIST OF ILLUSTRATIONS (Continued)

| Figure | Title                                                    | Page |

|--------|----------------------------------------------------------|------|

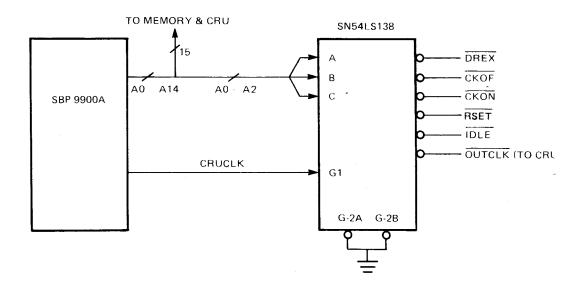

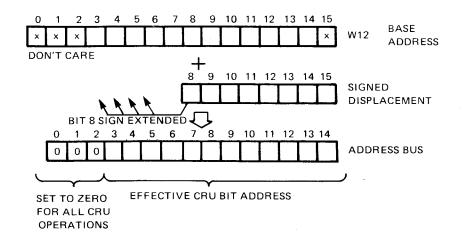

| 5-6    | SBP 9900A Single-Bit CRU Address Development             | 5-7  |

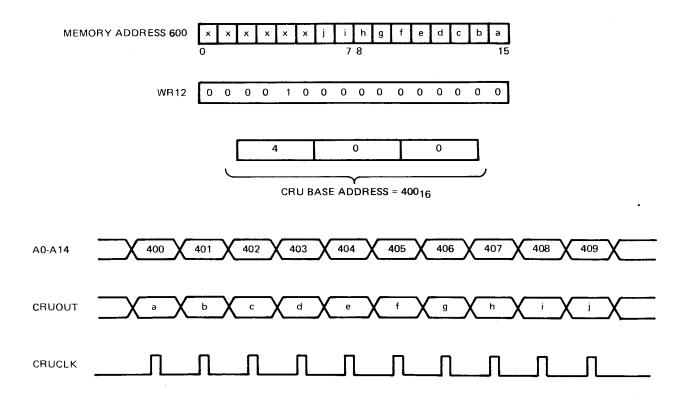

| 5-7    | Multiple-Bit CRU Output                                  | 5-7  |

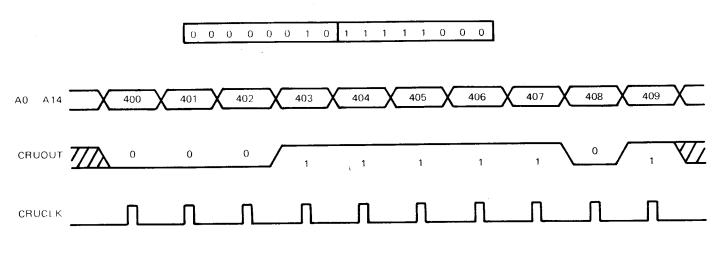

| 5-8    | Output of 02F816                                         | 5-8  |

| 5-9    | CRU Input Example                                        | 5-9  |

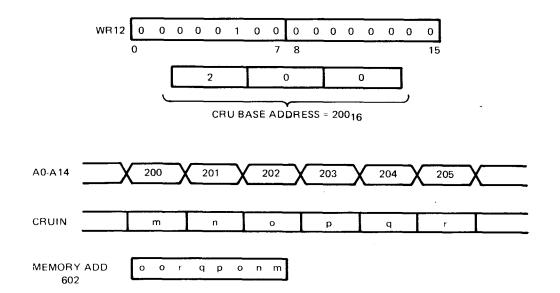

| 5-10   | Multiple-Bit CRU Input                                   | 5-9  |

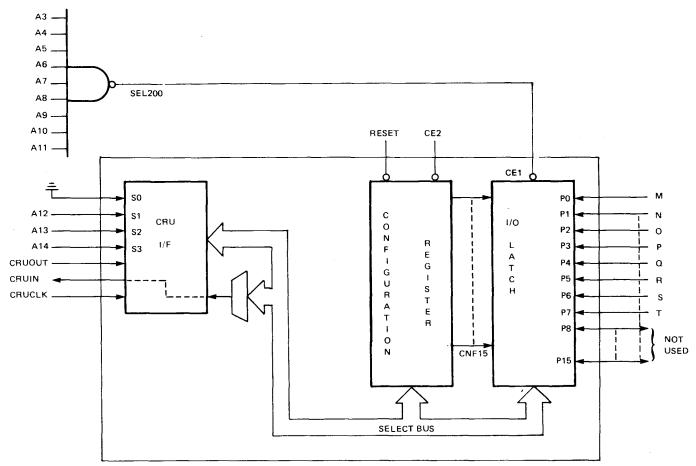

| 5-11   | CRU Interface Circuitry                                  | 5-11 |

| 5-12   | 1 of 16 Single Bit I/O Ports                             | 5-12 |

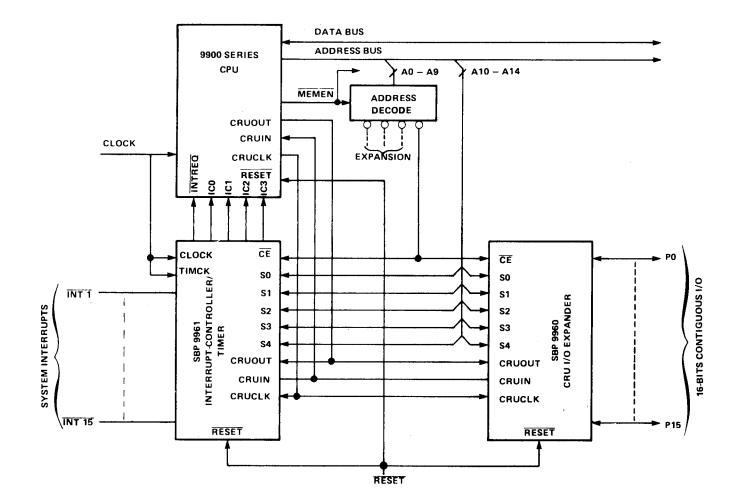

| 5-13   | SBP 9960/SBP 9961 System Configuration                   | 5-14 |

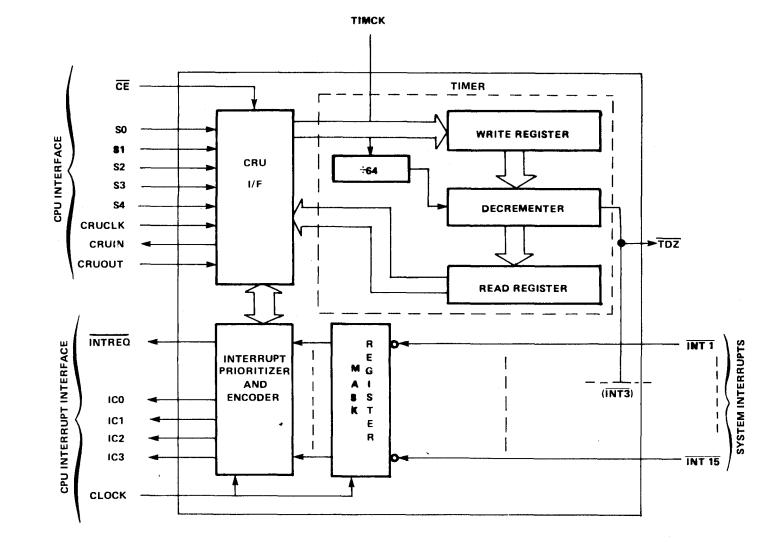

| 5-14   | SBP 9961 Block Diagram                                   | 5-21 |

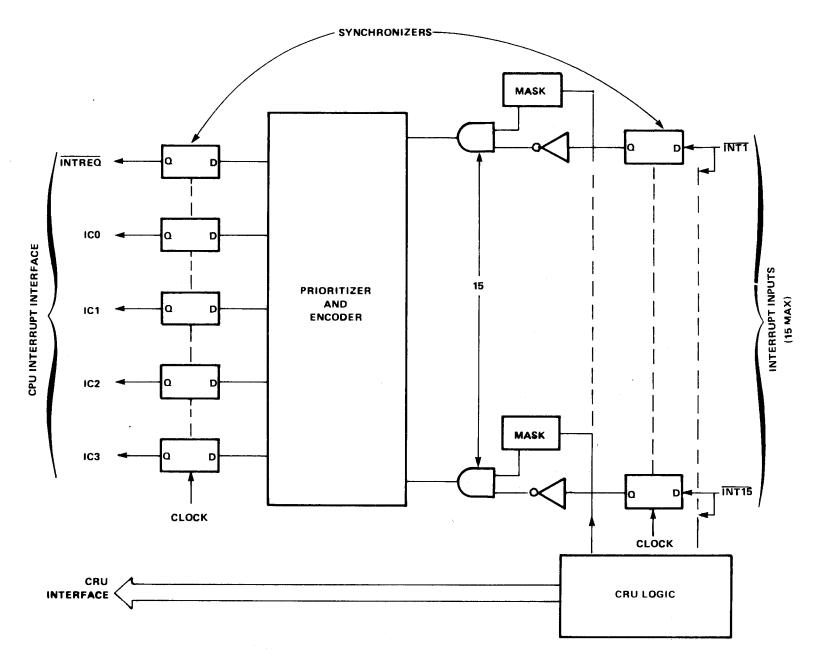

| 5-15   | Interrupt Control Logic                                  | 5-22 |

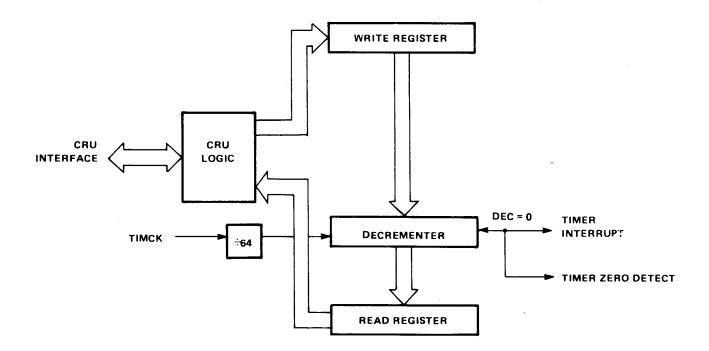

| 5-16   | Interval/Event Timer                                     | 5-24 |

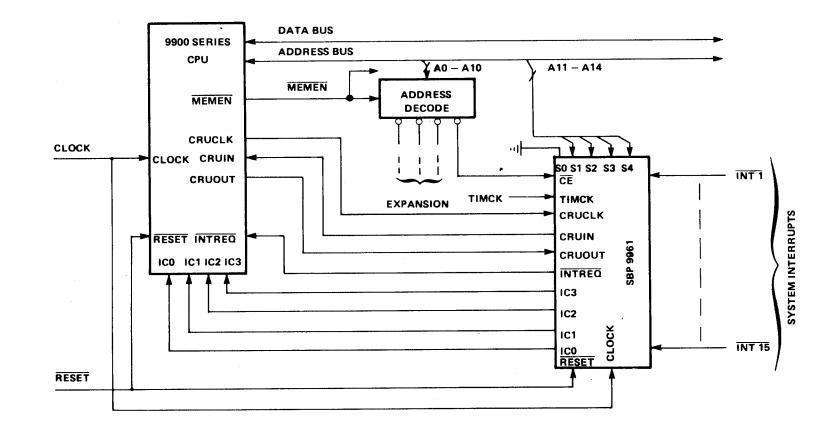

| 5-17   | SBP 9961 System Configuration                            | 5-26 |

| 5-18   | SBP 9961 Configuration with SBP 9960                     | 5-27 |

| 5-19   | Software UART CRU Interface                              |      |

| 5-20   | Software UART Control Program                            | 5-34 |

| 5-21   | I <sup>2</sup> L Microprocessor System                   |      |

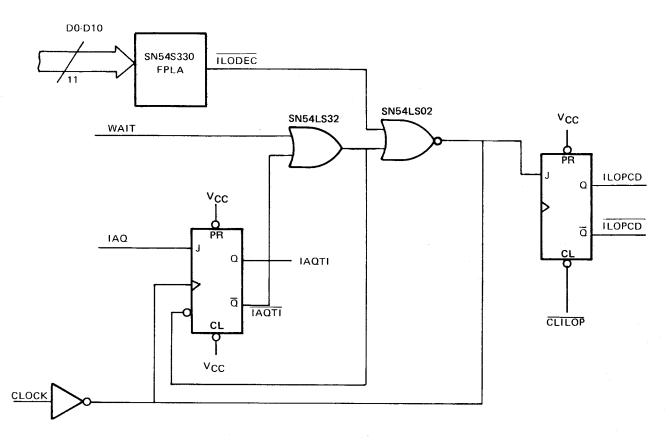

| 6-1    | Illegal Op Code Detector Circuitry                       |      |

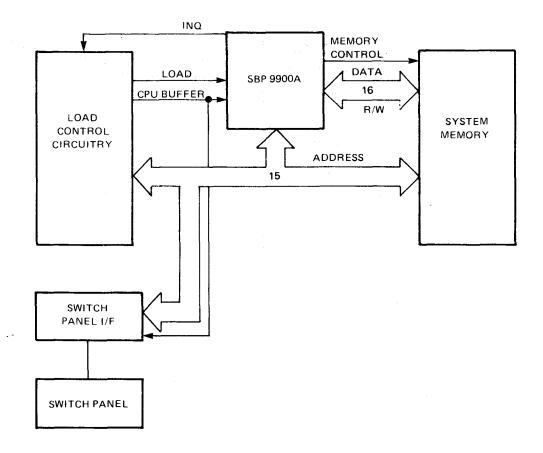

| 6-2    | System Configuration for Software Front Panel            |      |

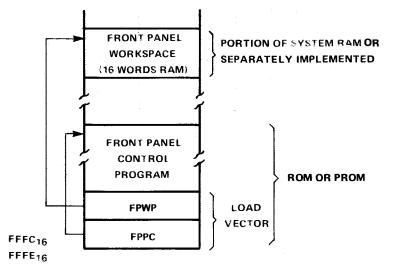

| 6-3    | Software Front Panel Memory Requirements                 |      |

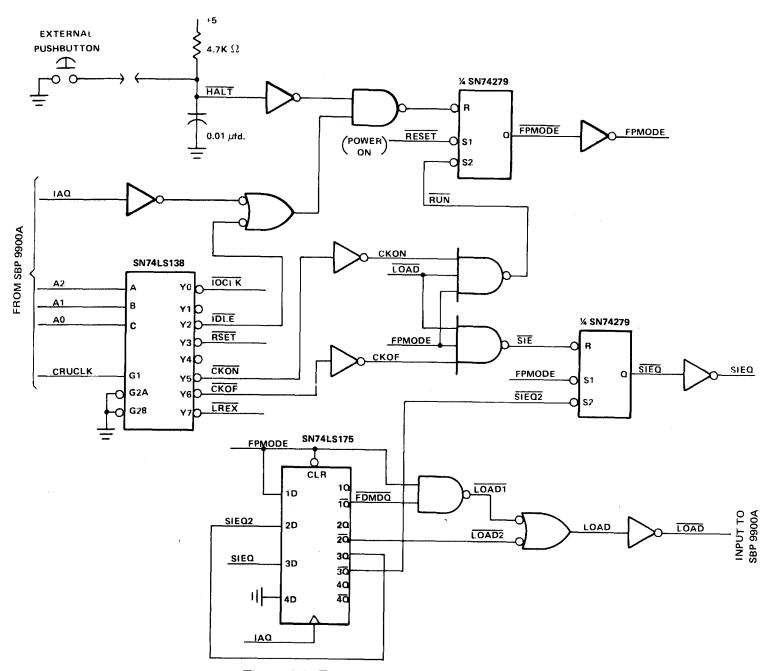

| 6-4    | Front Panel Control Circuitry                            |      |

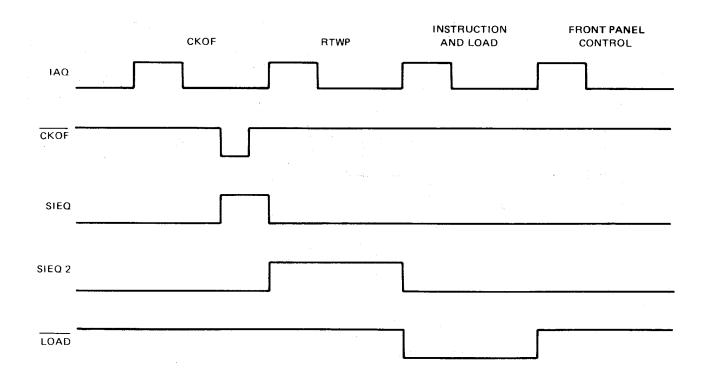

| 6-5    | Single Instruction Execution Timing                      |      |

| 6-6    | Signed Multiply Routine                                  | 6-8  |

| 6-7    | Signed Divide Routine                                    |      |

| 6-8    | Integer Square Root Routine                              | 6-10 |

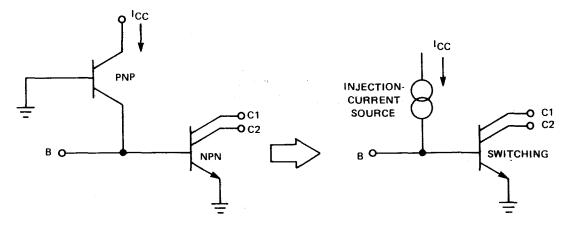

| 7-1    | Basic I <sup>2</sup> L Converter                         |      |

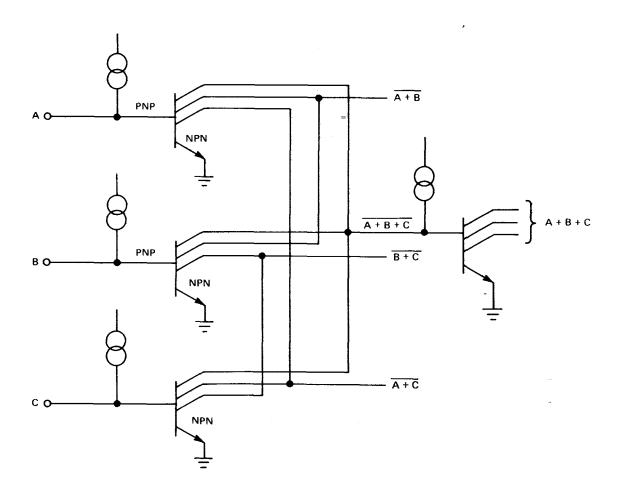

| 7-2    | I <sup>2</sup> L Positive NOR Functions                  | 7-2  |

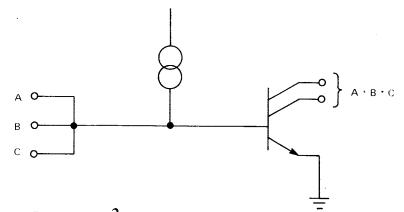

| 7-3    | I <sup>2</sup> L Positive NAND Functions                 | 7-3  |

| 7-4    | Current Steering Control                                 | 7-3  |

| 7-5    | SBP 9900A Resembles a Silicon Switching Diode            | 7-5  |

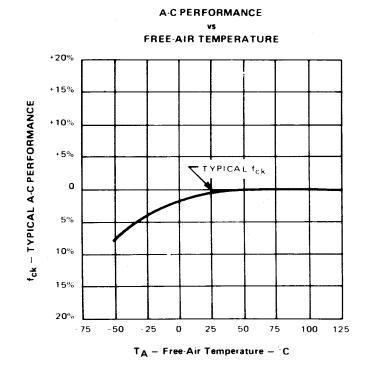

| 7-6    | Effects of Temperature and Process Functions             | 7-6  |

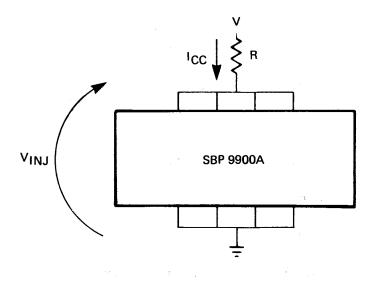

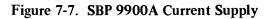

| 7-7    | SBP 9900A Current Supply                                 | 7-8  |

| 7-8    | TTL Voltage Source                                       | 7-8  |

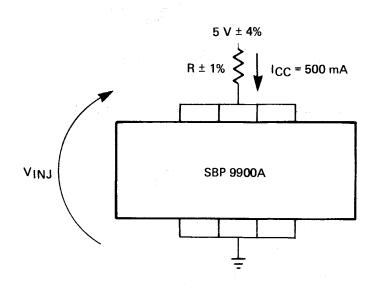

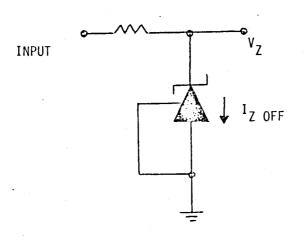

| 7-9    | Feedback Regulated Power Supply                          | 7-11 |

| 7-10   | Regulated Current Source                                 | 7-12 |

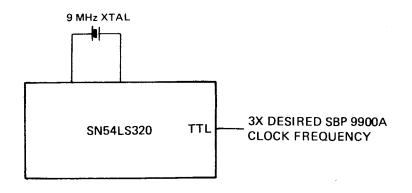

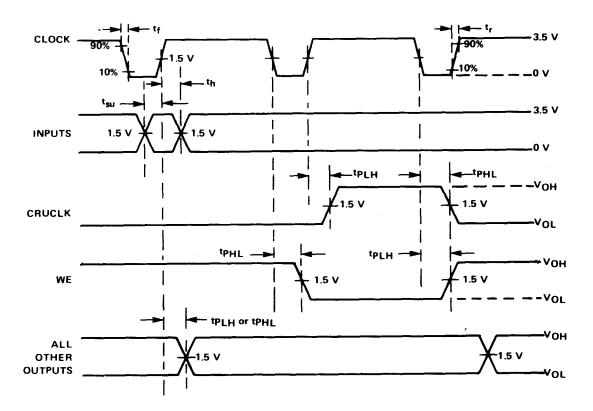

| 8-1    | SBP 9900A Clock Timing                                   | 8-1  |

| 8-2    | SBP 9900A Clock Generator                                |      |

| 8-3    | Voltage Controlled Oscillator                            |      |

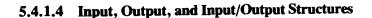

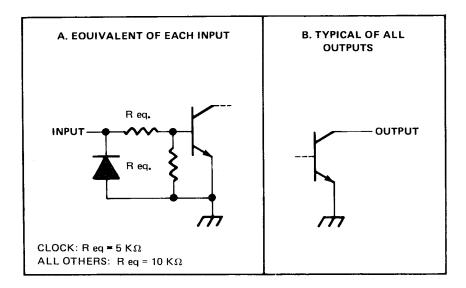

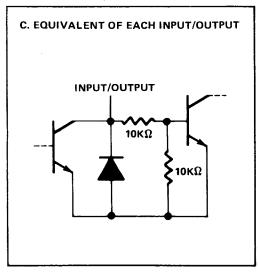

| 8-4    | Schematics of Equivalent Inputs, Outputs, Inputs/Outputs |      |

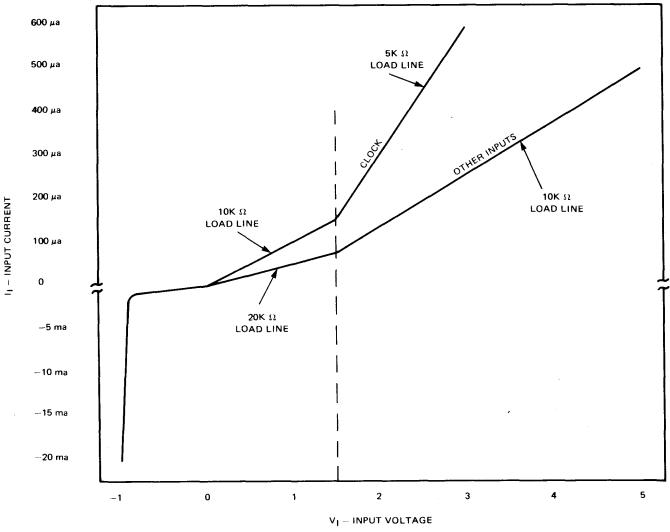

| 8-5    | Typical Input Characteristics                            |      |

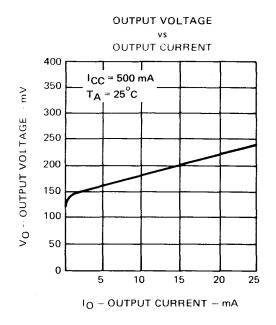

| 8-6    | Typical Output Characteristics                           |      |

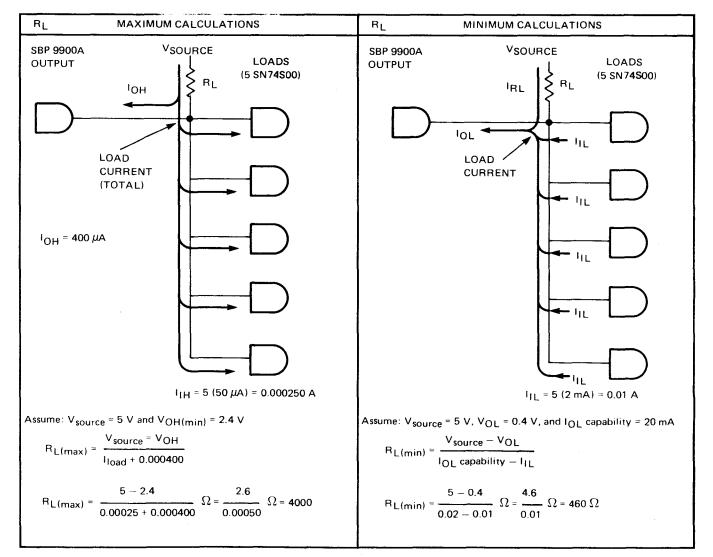

| 8-7    | Output Load Registor Calculations                        | 8-7  |

#### LIST OF TABLES

#### Title

#### 2 - 12-2 3-1 4-1 5-1 Instructions Generating CRU Cycles 5-4 5-2 SBP 9960 CRU Bit Assignments 5-13 5-3 5-4 5-5 6-1 7-1 8-1 8-2 8-3

#### Page

# Table

# SECTION I INTRODUCTION

#### **1.1 GENERAL DESCRIPTION**

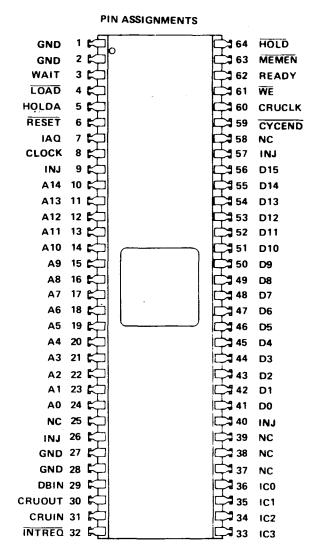

The SBP 9900A microprocessor, architecturally and functionally shown in Figure 1-1, 1-2, and 1-3, is a ruggedized monolithic parallel 16-bit Central Processing Unit (CPU) fabricated with oxide separated Integrated Injection Logic (I<sup>2</sup>L) technology. The SBP 9900A combines the properties of I<sup>2</sup>L technology with an advanced memory-to-memory achitecture, the flexibility of word/byte/bit data handling, and the versatility of a full 16-bit minicomputer instruction set, to extend the end application reach of Texas Instruments 9900 series microprocessor family into those applications requiring highly reliable, stable performance under severe operating conditions including nuclear radiation environments. I<sup>2</sup>L technology enables the SBP 9900A to operate over a very wide ambient temperature range from a single d-c current source. Static logic is used throughout with TTL compatible I/O. This allows use with standard logic/memory devices and thereby eliminates the need for specialized clock and interface functions. SBP 9900A software is directly compatible with other 9900 series microprocessor family members and is upward compatible with Texas Instruments 990 series minicomputer family.

#### **1.2 KEY FEATURES**

- Parallel 16-Bit Word Length

- Full Minicomputer Instruction Set Includes Multiply and Divide

- Directly Addresses Up to 65,536 Bytes/32,768 Words of Memory

- Advanced Memory-To-Memory Architecture

- Multiple 16-Word Register Files (Work Spaces) Reside in Memory

- Separate I/O, Memory, and Interrupt Bus Structures

- 16-Prioritized Hardware Interrupts

- 16 Software Interrupts (XOPS)

- Programmed, and DMA, I/O Capability

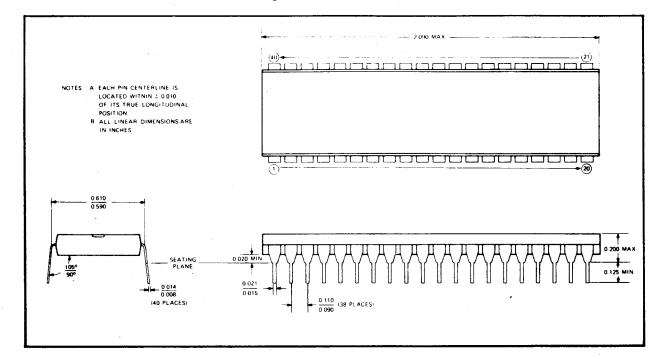

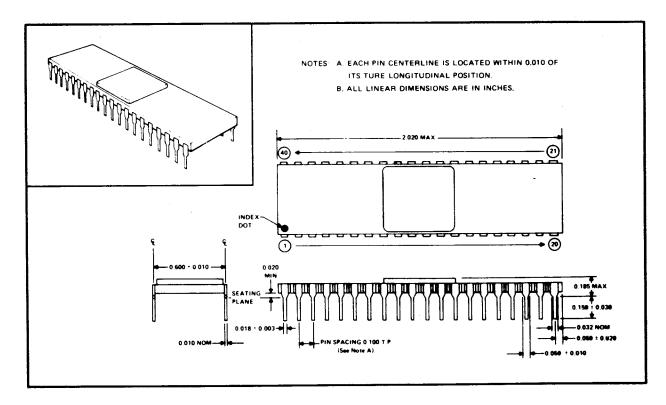

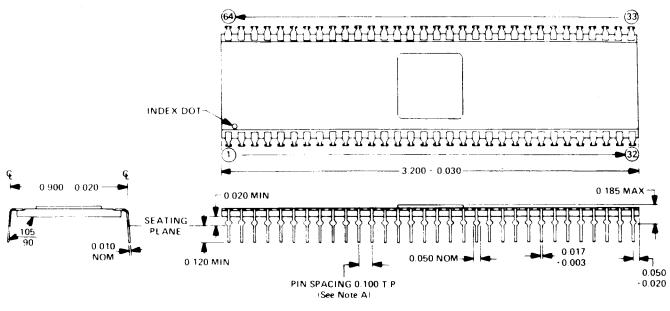

- 64-Pin Package

- Software Compatible with TI 9900 Microprocessor/990 Minicomputer Family

- I<sup>2</sup>L Technology:

- DC to 3 MHz Guaranteed Clock Frequency Range

- Single d-c Power Supply

- Fully Static Operation

- --- Single Phase, Edge-Triggering Clock

- Directly TTL Compatible I/O (Including Clock)

- Wide Ambient Temperature Operation: SBP 9900 ACJ: 0°C to +70°C

SBP 9900 AEJ: -40°C to +85°C

SBP 9900 ANJ: -55°C to +125°C

SBP 9900 AMJ: -55°C to +125°C (High Reliability Processing).

Figure 1-2. SBP 9900A Functional Description

Figure 1-3. SBP 9900A System

1-4

# SECTION II SBP 9900A ARCHITECTURE

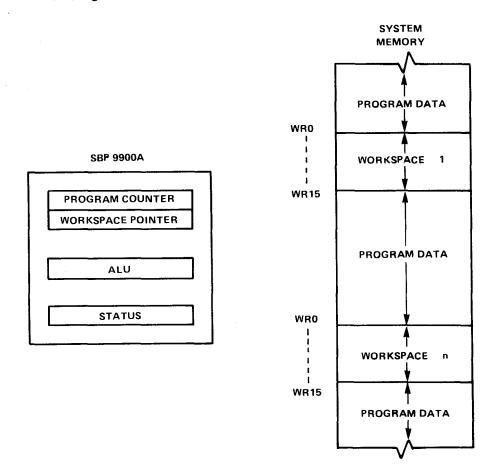

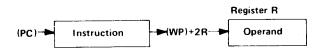

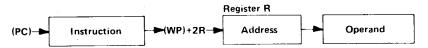

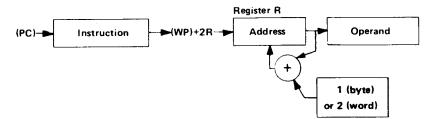

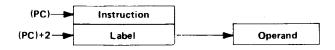

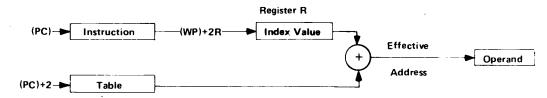

The SBP 9900A employs an advanced memory-to-memory architecture, as shown in Figure 2-1, which replaces the concept of a hardware register file internal to the CPU, with the concept of multiple register files external to the CPU. Each individual external register file is referred to as a "workspace" and is implemented as 16 contiguous system memory words. Each word may function as a general register holding either data, an address, an index value, or accumulated results. Therefore, the SBP 9900A commands the flexibility of multiple 16-word general-register workspaces limited in number only by the depth of the system memory itself.

## 2.1 REGISTERS

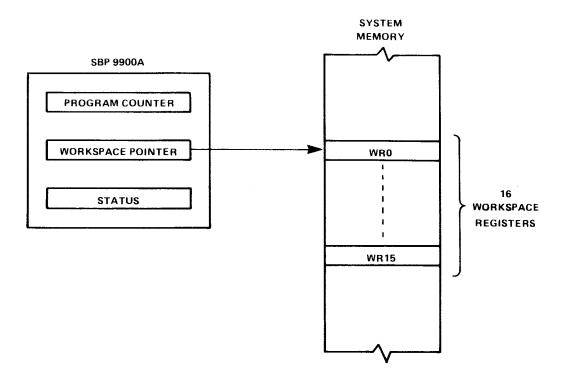

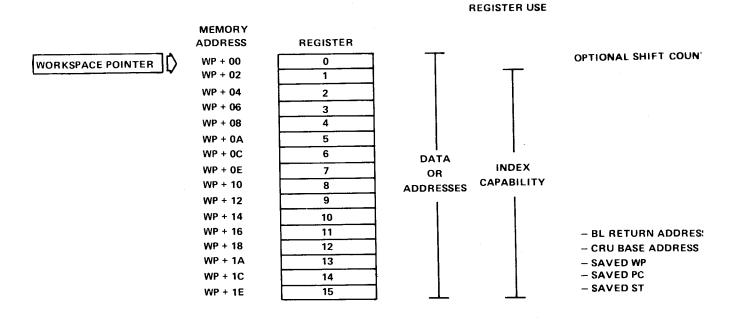

In support of an *active* SBP 9900A program environment, 19 registers (shown in Figure 2-2) which are accessible to the user, include those 16 workspace-register memory words which constitute the active workspace plus three hardware registers internal to the SBP 9900A: the workspace-pointer (WP) register, the program-counter (PC) register, and the status (ST) register.

Figure 2-1. SBP 9900A Memory-to-Memory Architecture

Figure 2-2. Registers Supporting Immediate SBP 9900A Program

**2.1.1** WORKSPACE-POINTER (WP) REGISTER. The workspace-pointer (WP) register is a 16-bit register that defines an *active* workspace by specifying the memory address (shown in Table 2-1) of the first of 16 contiguous memory word locations which together form the workspace. The SBP 9900A automatically calculates the memory address of a specific workspace-register (WR), within the active workspace, by adding the WP value to the specified WR number weighted by a factor of two:

MA = WP plus 2R where R = 0 through  $F_{16}$ .

When either a different or extended set of workspace-registers is required, the program simply activates a new workspace by loading the WP with the initial memory word address of that new workspace. Through proper selection of the new WP value, the new workspace may either overlap\* or be exclusive from the old workspace. This highly efficient procedure for switching from one workspace to another results in a significant reduction in system overhead when compared to internal-register-file based microprocessors which must perform "n" memory-write operations to save the contents of "n" internal file registers; then perform "n" memory-read operations to redefine the contents of "n" internal file registers.

<sup>\*</sup>When overlapping workspaces, caution must be exercised such that when utilizing those registers common to each workspace, the individual functional definitions of each register (see 2.1.2) do not conflict.

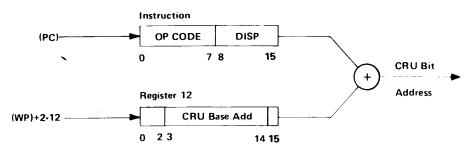

**2.1.2** WORKSPACE-REGISTERS. A workspace is comprised of 16 contiguous 16-bit memory words (shown in Table 2-1) which function as general workspace-registers to store temporary data, addresses, or accumulated results. Additionally, bits 12 through 15 of WRO may specify the number of bit positions an operand is to be shifted by the instructions SLA, SRA, SRC, and SRL. WR1 through WR15 may each be used as an index register to specify a bias from the contents of memory word location PC plus 2 in selection of an operand located anywhere in general memory. WR11 will store the return PC value when the Branch and Link (BL) instruction is executed. Bits 3 through 14 of WR12 contain the 12-bit CRU base address used in conjunction with the Communications Register Unit (CRU) instructions SBO, SBZ, TB, LDCR, and STCR. WR13 through WR15 of a *new* workspace, activated under program control through execution of either the Branch and Load Workspace Pointer (BLWP) instruction or an Extended Operation (XOP) instruction, or activated under hardware control in response to either an interrupt or the LOAD/RESET signal commands, will store the *old* WP, PC, and ST values for preservation of return linkage.

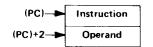

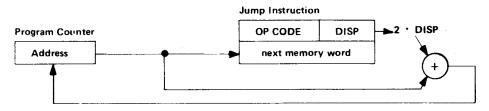

**2.1.3 PROGRAM-COUNTER (PC) REGISTER.** The program-counter (PC) register is a 16-bit register similar in function to that of other microprocessors. It contains the memory address of the next instruction to be executed. As each instruction is in turn executed, the PC is either incremented by 2 to the next consecutive memory word address or altered directly by the executing instruction.

2.1.4 STATUS REGISTER (ST). The status register (ST) is a 16-bit register similar in function to that of other microprocessors. It is composed of flag-bits which indicate the results of the most recent arithmetic or Boolean operation performed. Additionally, bits ST12 through ST15 contain a 4-bit interrupt mask which defines the lowest priority interrupt that will be recognized. This interrupt mask may be altered under program control through execution of the Load Interrupt Mask Immediate (LIMI) instruction, or automatically altered under hardware control in response to acceptance of an interrupt.

# 2.2 MEMORY-TO-MEMORY OPERATIONS

The instructions of the SBP 9900A are not limited to workspace-registers as operand sources or result destinations. Any of the general-source/general-destination instructions permit operations to be performed on any general memory location by any other general memory location. In other words, a single two-address instruction has the capability to:

- a. fetch an operand from any general memory location,

- b. fetch a second operand from another general memory location,

- c. combine the operands, and

- d. store the results in that general memory location from which the second operand was fetched.

For example, a single Add (A) instruction can add any memory word to any other memory word within the 32K word memory space. To accomplish this same operation, the architectures of other microprocessors require execution of a series of instructions through which memory contents are moved to internal registers, added, and then returned to memory. Consequently, the memory-to-memory architecture of the SBP 9900A supports lower memory cost plus lower system development cost by:

- a. minimizing program storage requirements through reduction of the number of instructions required to accomplish execution of a given task,

- b. reducing program complexity,

- c. reducing program documentation, and

- d. reducing program debug time.

# 2.3 BUS STRUCTURES.

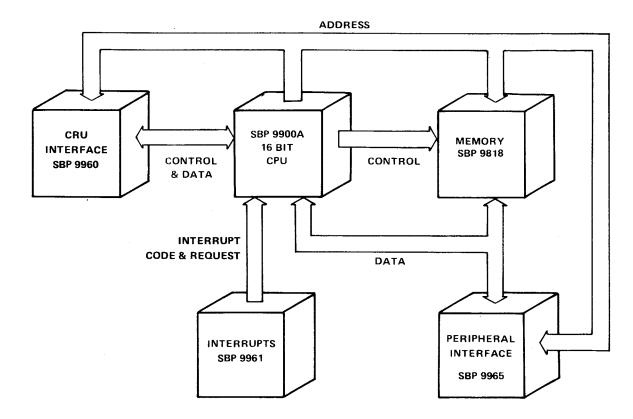

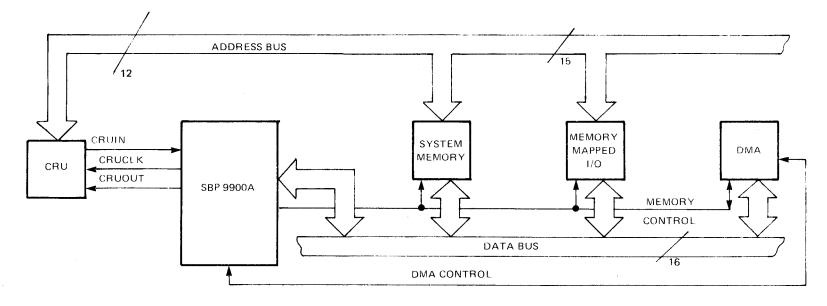

The SBP 9900A employs separate memory, CRU, and interrupt bus structures as shown in Figure 2-3. Each bus is optimized for its individual function.

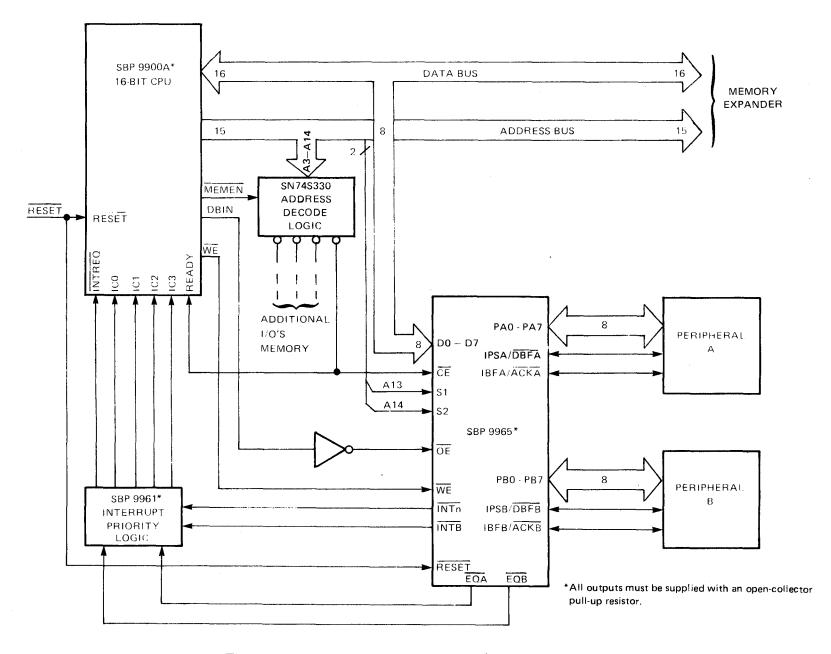

**2.3.1 MEMORY BUS.** The memory bus handles uniform width memory words which are transferred in parallel between memory or memory-mapped peripheral I/O devices (i.e., SBP 9965). The memory reference instructions operate on parallel words or bytes, with additional masking instructions available to isolate individual bits. The SBP 9900A maintains separate address outputs, control I/O, and data I/O to optimize communication with standard memories; the SBP 9900A employs HOLD and HOLDA handshaking signals, similar in function to other micro-processors, to aid system implementation of DMA capability. The non-multiplexed memory bus structure of the SBP 9900A simplifies board layout and lowers system cost by precluding the need for external bus demultiplexing devices. A complete discussion of memory interface to the SBP 9900A is contained in Section 3.0.

Figure 2-3. SBP 9900A System Bus Structure

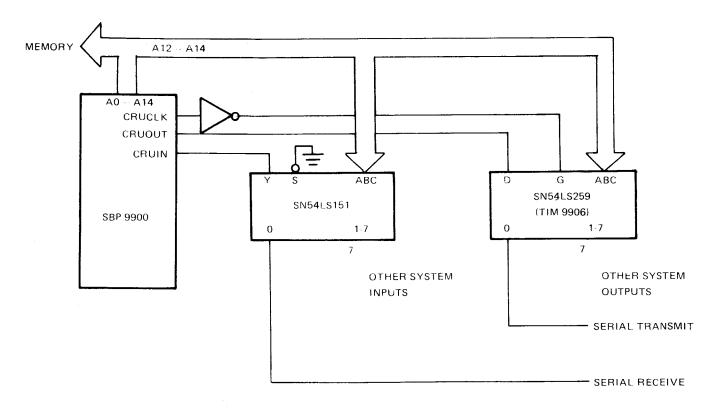

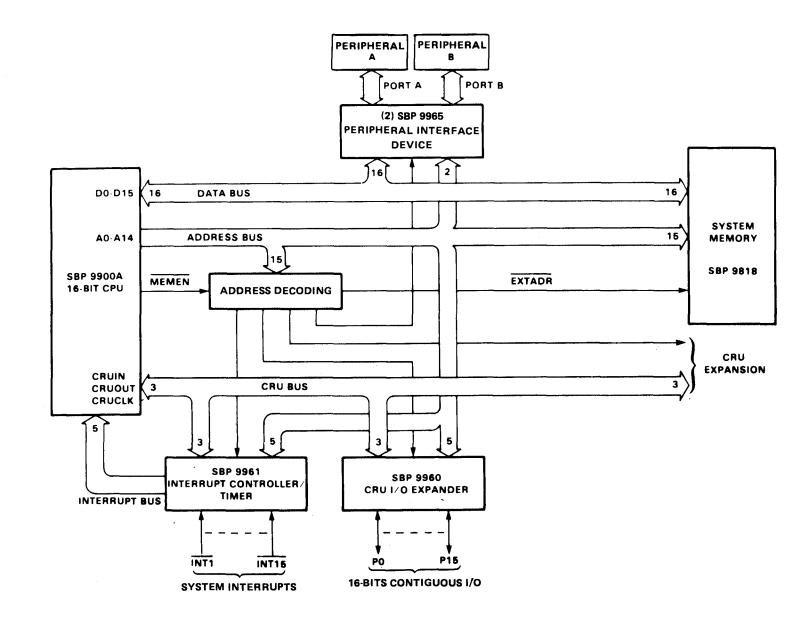

**2.3.2 CRU BUS.** The CRU bus handles variable bit-length data each bit of which is addressed in parallel and transferred serially between the SBP 9900A and Communications Register Unit (CRU) interface devices such as the SBP 9960 and SBP 9961. Those interface devices in turn communicate with auxillary systems devices ranging from bit-oriented sensors and actuators to word/byte/n-bit-field oriented peripherals. Therefore, the Communications Register Unit (CRU) is a cost-effective flexible means by which the SBP 9900A may be interfaced to peripheral I/O devices independent of the memory data bus. As a result, the necessity to reserve a memory address for each I/O device is eliminated. For I/O device interfacing, the SBP 9900A supports CRU expansion up to 4096 individually addressable output bits. A single CRU instruction can operate on an individual CRU bit or on variable CRU bit-fields ranging anywhere from one to 16 bits in length. A complete discussion of the operation, implementation, and flexibility of the CRU is contained in Section 5.0.

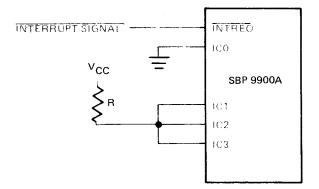

**2.3.3 INTERRUPT BUS.** The SBP 9900A handles multiple prioritized interrupts with internal generation of associated trap vectors. The interrupt bus provides the SBP 9900A with an interrupt request plus a 4-bit code identifying the priority level of the interrupt requesting service. A complete discussion of SBP 9900A interrupt processing is contained in Section 4.0.

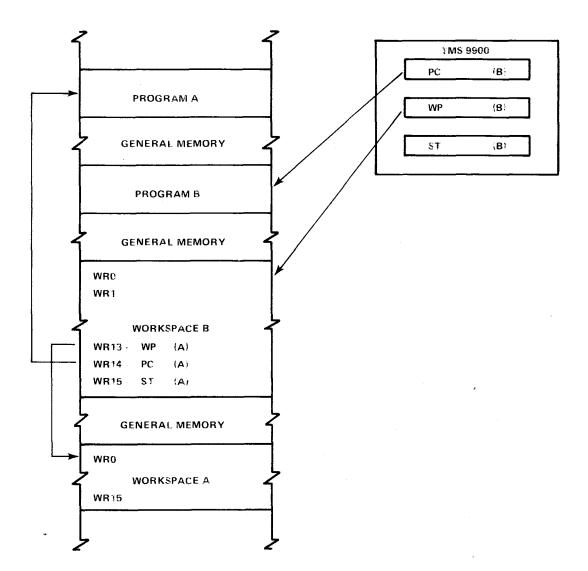

# 2.4 CONTEXT SWITCHING

An operation referred to as a "context switch" is automatically performed by the SBP 9900A in response to:

- a. recognition of an interrupt,

- b. assertion of a LOAD or RESET signal command, or

- c. execution of an XOP or BLWP instruction.

The purpose of a context switch is to expeditiously perform a hardware branch from the present (old) program environment to a new program environment with preservation of return linkage to the original (old) program environment. The hardware effect of a context switch is to initiate new WP and PC values, yet preserve the original (old) WP, PC, and ST values for return linkage. Dedicated memory locations described in Section 3.1, contain the new WP and PC values associated with:

- a. each individual interrupt priority level,

- b. the  $\overline{\text{LOAD}}$  or  $\overline{\text{RESET}}$  signal command, or

- c. each individual XOP instruction.

The new WP and PC values associated with the BLWP instruction are contained in consecutive memory word locations defined through the active addressing mode of the BLWP instruction under execution. The sequence of hardware events which are accomplished during a context switch are:

- a. the new WP value is fetched from memory and loaded into the SBP 9900A's temporary T<sub>1</sub> register,

- b. the present (old) ST value is preserved in WR15 of the new workspace defined by  $T_1$ ,

- c. the present (old) PC value is preserved in WR14 of the new workspace defined by T<sub>1</sub>,

- d. the present (old) WP value is preserved in WR13 of the new workspace defined by T<sub>1</sub>,

- e. the contents of T<sub>1</sub> (the new WP value) is transferred into the SBP 9900A's WP register,

- f. the new PC value is fetched from memory and loaded into the SBP 9900A's PC register,

- g. the first instruction of the new program environment is fetched from that location addressed by the PC (new PC value) register, and

- h. instruction execution begins in the new program environment.

When the new program executes a Return Workspace Pointer (RTWP) instruction, the original (old) WP, PC, and ST values (preserved in WR13, 14, and 15 respectively of the new workspace) are automatically restored to the SBP 9900A thereby reactivating the old workspace and the original (old) program environment. Consequently, the workspace-oriented memory-to-memory architecture of the SBP 9900A in conjunction with its automatic context switching flexibility, is the basic hardware mechanism which allows the SBP 9900A to expeditiously handle unlimited nesting of interrupts and/or subroutines.

# 2.5 MACHINE CYCLES

Each operation performed by the SBP 9900A consists of a sequence of machine cycles. In each machine cycle the SBP 9900A performs a data transfer with memory or the CRU, and/or an internal arithmetic or Boolean operation.

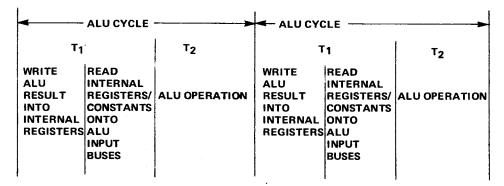

**2.5.1** ALU MACHINE CYCLES. Each ALU machine cycle is two clock periods in length. In an ALU cycle, the ALU performs an arithmetic or Boolean operation on two operands contained internally. No external data transfers occur during an ALU cycle.

**2.5.2 MEMORY READ MACHINE CYCLES.** The function of the memory read cycle is to transfer a word of data contained in memory to the SBP 9900A. An ALU operation can be performed during a memory read cycle. Memory read cycles are a minimum of two clock periods in length. If wait states are inserted to allow access to slow memories, the length of the memory read cycle is extended one clock period for each wait state.

IAQ is active (high) during any CPU initiated instruction acquisition memory read cycle. IAQ is held active for the duration of the entire memory read cycle.

**2.5.3 MEMORY WRITE MACHINE CYCLES.** The memory write cycle is identical to the memory read cycle, except that data is written to rather than read from memory.

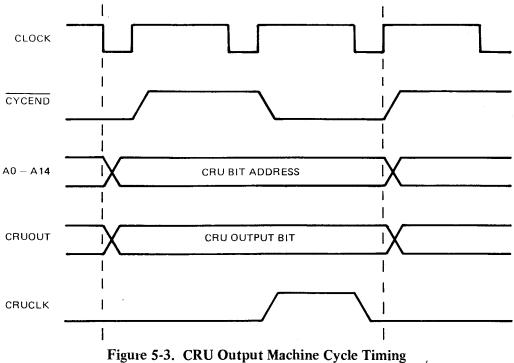

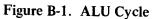

**2.5.4** CRU OUTPUT MACHINE CYCLES. Each CRU output machine cycle is two clock periods in length. In addition to outputting a bit of CRU data, an ALU operation may also be performed.

**2.5.5 CRU INPUT MACHINE CYCLES.** The CRU input machine cycle is identical to the CRU output cycle, except that one bit of CRU data is input rather than output.

**2.5.6 INSTRUCTION EXECUTION EXAMPLES.** Examples of how sequences of machine cycles are used to execute instructions are shown in Figures 2-4 to 2-7. For additional information on instruction machine cycles refer to Appendix B. Note that the first machine cycle of each instruction is always an instruction fetch memory read cycle; the second is always an ALU cycle.

#### SBO

| CYCLE | TYPE        | FUNCTION                  |

|-------|-------------|---------------------------|

|       | -           |                           |

| 1     | Memory Read | Instruction Fetch         |

| 2     | ALU         | Decode Op Code            |

| 3     | ALU         | Calculate Address of WR12 |

| 4     | Memory Read | Fetch (WR12)              |

| 5     | ALU         | Calculate CRU Address     |

| 6     | CRU Output  | Output Bit, Increment PC  |

|       |             |                           |

Figure 2-4. SBO Instruction Machine Cycles

# STCR RO,5

| CYCLE | TYPE         | FUNCTION                  |

|-------|--------------|---------------------------|

| 1     | Memory Read  | Instruction Fetch         |

| 2     | ALU          | Decode Op Code            |

| 3     | Memory Read  | Fetch (WRO)               |

| 4     | ALU          | Calculate Address of WR12 |

| 5     | Memory Read  | Fetch (WR12)              |

| 6     | ALU          | Set Up                    |

| 7     | ALU          | Set Up                    |

| 8-12  | CRU Input    | Transfer 5 Bits           |

| 13    | ALU          | Set Up                    |

| 14    | ALU          | Set Up                    |

| 15-17 | ALU          | Zero Filling              |

| 18    | ALU          | Parity Generation         |

| 19    | ALU          | Load WRO Address in MA    |

| 20    | ALU          | Byte Positioning          |

| 21    | Memory Write | Store Data in WRO,        |

|       |              | Increment PC              |

Figure 2-5. STCR Instruction Machine Cycles

#### RTWP

| CYCLE | TYPE        | FUNCTION                  |

|-------|-------------|---------------------------|

|       |             |                           |

| 1     | Memory Read | Instruction Fetch         |

| 2     | ALU         | Decode Opcode             |

| 3     | ALU         | Calculate Address of WR15 |

| 4     | Memory Read | Restore Status from WR15  |

| 5     | Memory Read | Restore PC from WR14      |

| 6     | Memory Read | Restore WP from WR13      |

| 7     | ALU         | Load PC into MA           |

|       |             |                           |

#### Figure 2-6. RTWP Instruction Machine Cycles

| CYCLE | TYPE         | FUNCTION             |

|-------|--------------|----------------------|

| 1     | Memory Read  | Instruction Fetch    |

| 2     | ALU          | Decode Opcode        |

| 3     | Memory Read  | Fetch (WR1)          |

| 4     | ALU          | Set Up               |

| 5     | Memory Read  | Fetch ((WR1))        |

| 6     | ALU          | Set Up               |

| 7     | Memory Read  | Fetch (WR2)          |

| 8     | ALU          | Addition             |

| 9     | Memory Write | Store Result in WR2, |

|       |              | Increment PC         |

#### A \*R1,R2

Figure 2-7. 'A' Instruction Machine Cycles

#### 2.6 MACHINE CYCLE MIN/MAX LIMITS; MAXIMUM LATENCY TO ENTER THE HOLD STATE

Machine cycle minimum/maximum limits, useful information for system design, are listed in Table 2-2. The SBP 9900A can enter the hold state only during an ALU, CRU input, CRU output, or combination CRU/ALU machine cycle. Consequently, the maximum number of back to-back memory cycles determines the maximum machine cycle latency for the SBP 9900A to enter the hold state. Table 2-2 shows the maximum number of back-to-back memory cycles to be three consecutive memory read cycles. As a result, the maximum latency for the SBP 9900A to enter the hold state is seven clocks: MAXIMUM HOLD LATENCY = setup (1 clock) plus three consecutive memory read cycles (6 clocks assuming no wait states).

|                                       | MINIMUM     | MAXIMUM |

|---------------------------------------|-------------|---------|

| Consecutive memory read cycles        | l           | 3       |

| Consecutive memory write cycles       | , t         | 1       |

| Consecutive ALU cycles                | 1           | 51      |

| Consecutive CRU cycles                | 1           | 16      |

| Frequency of consecutive memory cycle | 5 pairs     |         |

| to non-memory cycle events            | (64 machine |         |

|                                       | cycles      |         |

|                                       | during      |         |

|                                       | DIV)        |         |

# TABLE 2-2. MACHINE CYCLE MINIMUM/MAXIMUM LIMITS

# 2.7 CYCLE END "CYCEND" SIGNAL

When active, the CYCEND signal of the SBP 9900A indicates that a new machine cycle will be initiated on the next positive-going transition of the clock. Since  $\overline{\text{MEMEN}}$  remains active-low for as many as three back-to-back memory read cycles, CYCEND may be used in conjunction with  $\overline{\text{MEMEN}}$  to allow external logic to identify the boundaries of each individual memory read cycle.

# SECTION III MEMORY

The SBP 9900A, as discussed in Section 2.1, utilizes system memory for implementation of multiple workspaceregister-files and storage of context switch transfer vectors in addition to storage of data and program instructions. The full parallel memory bus of the SBP 9900A facilitates interface to standard types of semiconductor memory devices. For nonvolatile program/data storage, Texas Instruments offers a wide selection of factory-masked ROMs, field-programmable PROMs, and erasable EPROMs.

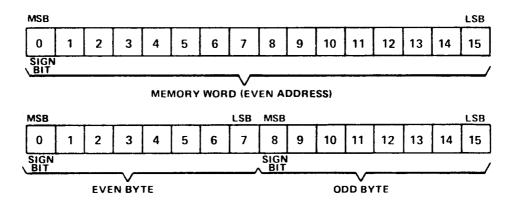

# 3.1 MEMORY ORGANIZATION

The SBP 9900A forms a 16-bit address word, internally, which describes a  $64K \times 8$ -bit address space. The 15 most-significant bits of the address word are passed to external memory to describe a  $32K \times 16$ -bit address space. Consequently, all parallel data transfers between the SBP 9900A and memory are formatted as 16-bit words. The least-significant bit of the 16-bit address word is retained internal to the SBP 9900A to distinguish between the even and odd 8-bit halves (bytes) of the 16-bit memory word.

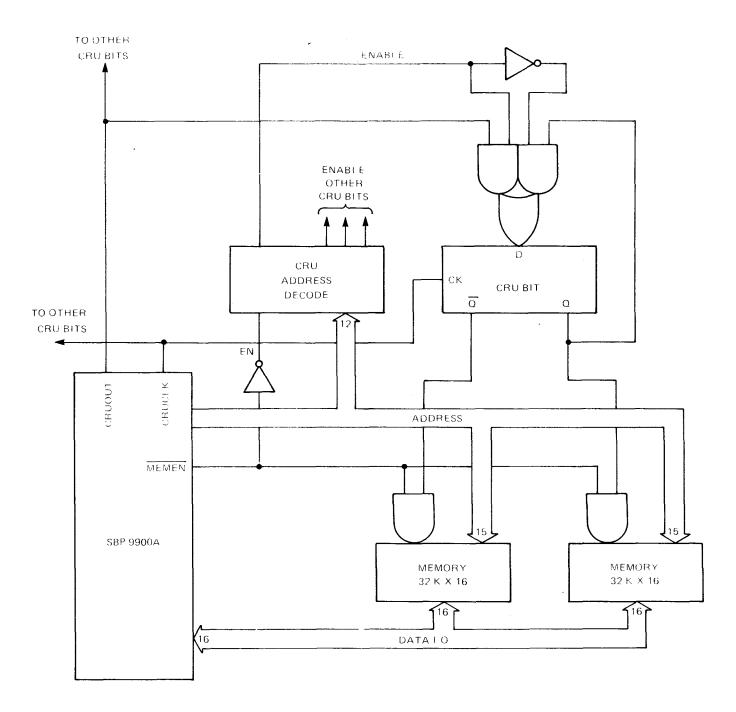

Although the above partitioning of address space allows the SBP 9900A to process with equal effectiveness both 16-bit words and 8-bit bytes, the total number of directly addressable 16-bit words is bounded by an address reach of 32K. This address reach may be indirectly expanded through utilization of address bank-mapping techniques. For example, two 32K word memory banks, shown in Figure 3-1, can be activated exclusive from one another through program control of a CRU bit. In other words the SBP 9900A, under program control, executes either a Set Bit To One (SBO) or Set Bit To Zero (SBZ) CRU instruction to activate the desired memory bank. As a result, memory depth is indirectly expanded, for purpose of this example, from 32K x 16-bits to 64K x 16 bits.

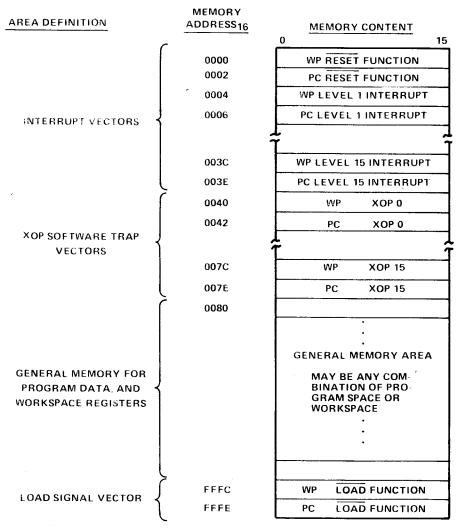

In addition to standard storage of data and program object code, the memory space of an SBP 9900A system is also used for implementation of multiple workspace-register-files plus storage of context switch transfer vectors (new WP and PC values). Although workspace-register-files can be located anywhere in the available memory space, the context switch transfer vectors are restricted to dedicated memory locations as shown in the general SBP 9900A memory map of Figure 3-2.

**3.1.1 RESET TRANSFER VECTORS.** Activation of the RESET signal command causes the SBP 9900A to initiate a level-zero interrupt sequence. As a result, the SBP 9900A traps to memory locations  $0000_{16}$  and  $0002_{16}$  to fetch the stored transfer vectors (new WP and PC values respectively) which define the program environment for the associated RESET service routine.

**3.1.2** HARDWARE INTERRUPT TRANSFER VECTORS. Memory locations  $0004_{16}$  through  $003E_{16}$  contain the hardware interrupt vectors (new WP and PC values) which define the program environment for the corresponding service routine associated with each hardware interrupt level (1 through 15). If a particular hardware service interrupt level is not used in a given system, then the corresponding memory words (2) which normally contain the associated transfer vectors can be used for general program/data storage.

Figure 3-1. Memory Bank Mapping Via CRU Bit

Figure 3-2. SBP 9900A General Memory Map

**3.1.3 XOP INSTRUCTION: SOFTWARE INTERRUPT TRANSFER VECTORS.** Memory locations  $0040_{16}$  through  $007E_{16}$  contain the XOP instruction software interrupt transfer vectors (new WP and PC values) which define the program environment for the corresponding subroutine associated with each XOP instruction (0 through 15). If a particular XOP instruction is not used in a given system, then the corresponding memory words (2) which normally contain the associated transfer vectors can be used for general program/data storage.

**3.1.4 LOAD TRANSFER VECTORS.** Activation of the LOAD signal command causes the SBP 9900A to fetch the stored transfer vectors (new WP and PC values respectively) from memory locations  $FFFC_{16}$  and  $FFFE_{16}$  which define the program environment for the associated LOAD service routine.

**3.1.5 TRANSFER VECTOR STORAGE REQUIREMENTS.** The transfer vectors can be stored in either ROM or RAM. ROM-based vectors are fixed and therefore may not be altered under program control. The **RESET** transfer vectors should reside in non-volatile memory to ensure proper system start-up. The **RESET** service routine should initialize any transfer vector which is stored in RAM. The program can then manipulate the RAM-based vectors to alter workspace assignments or service routine entry points as necessary.

# 3.2 MEMORY CONTROL

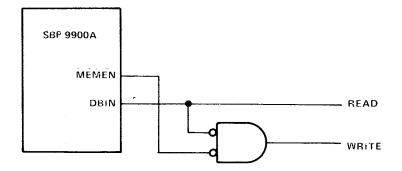

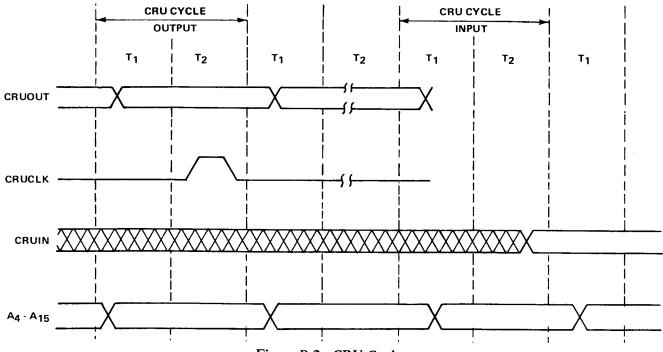

During read or write memory cycles, the activity of the address bus and data bus is specified by three control signals: memory enable ( $\overline{\text{MEMEN}}$ ), data bus in (DBIN), and write enable ( $\overline{\text{WE}}$ ).  $\overline{\text{MEMEN}}$  becomes active (low) with the beginning of any memory cycle and remains active for the duration of that memory cycle. In the case of back-to-back memory read cycles,  $\overline{\text{MEMEN}}$  becomes active with the beginning of the first read cycle and remains active until the completion of the last read cycle. DBIN becomes active (high) with the beginning of a memory read cycles, DBIN becomes active for the duration of that read cycle. In the case of back-to-back memory read cycles, DBIN becomes active with the beginning of the first read cycle and remains active until the completion of the last read cycle. An active DBIN indicates that the SBP 9900A has disabled its data bus output buffers so memory read data can be received.  $\overline{\text{WE}}$  becomes active (low) with the negative-going edge of the first clock of a memory write cycle;  $\overline{\text{WE}}$  is deactivated with the negative-going edge of the last clock of a memory write cycle. The timing of  $\overline{\text{WE}}$  is compatible with the read/write (R/ $\overline{\text{W}}$ ) control signal associated with many standard RAMs.

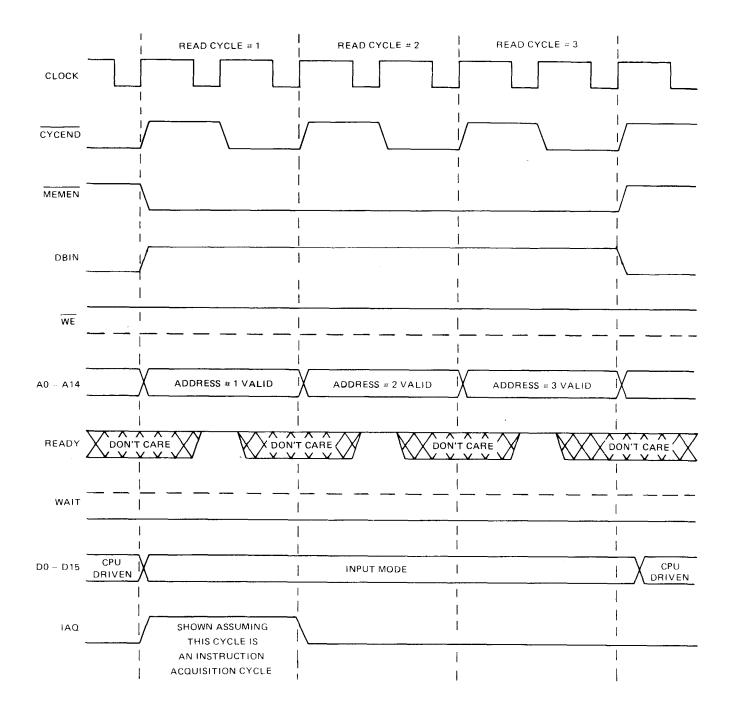

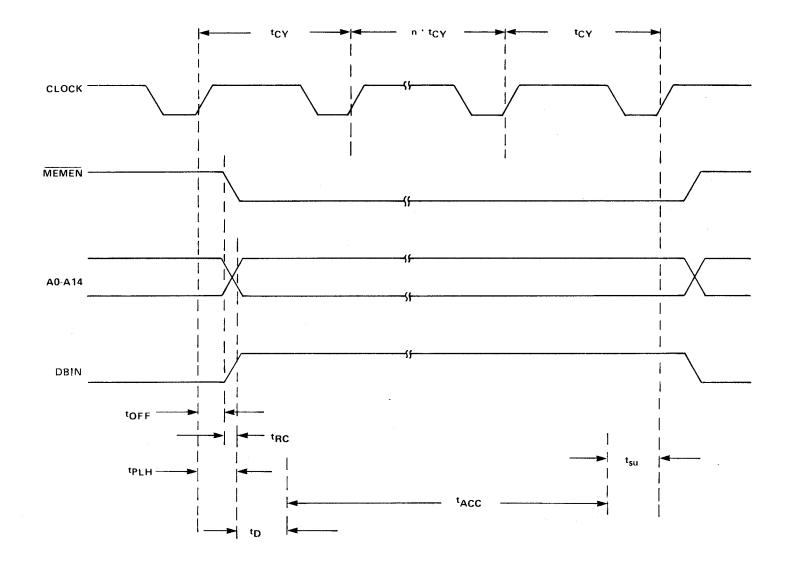

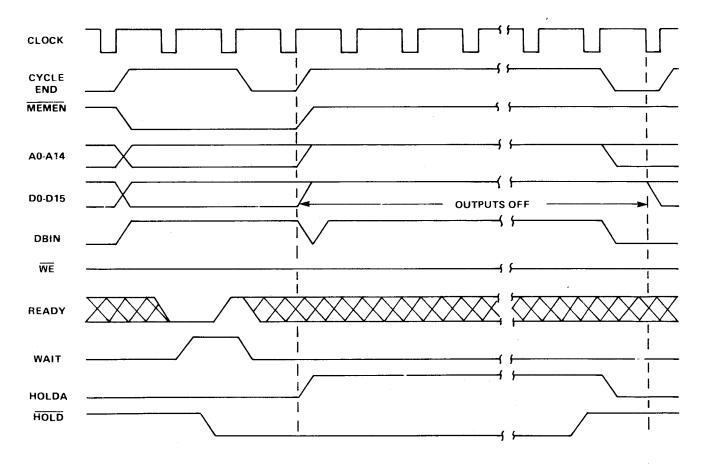

**3.2.1 MEMORY READ CYCLE.** Figure 3-3 shows the timing for three back-to-back memory read machine cycles with no wait states. At the beginning of the first read cycle, <u>MEMEN</u> and DBIN become active with a valid address applied on the address lines. WE remains inactive (high) during all memory read operations. If no wait states are required, the READY line must be high prior to the second-going clock of each individual read cycle. At the end of the last memory read cycle, <u>MEMEN</u> and DBIN become inactive. At that time, though the address may change, the data bus remains in the input mode until terminated by the next negative-going clock. Note that <u>CYCEND</u> may be used during back-to-back read cycles, to distinguish the beginning of each individual read cycle.

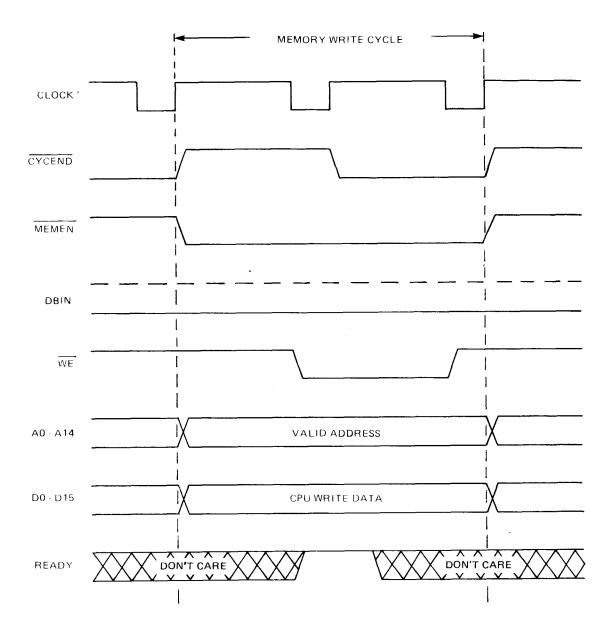

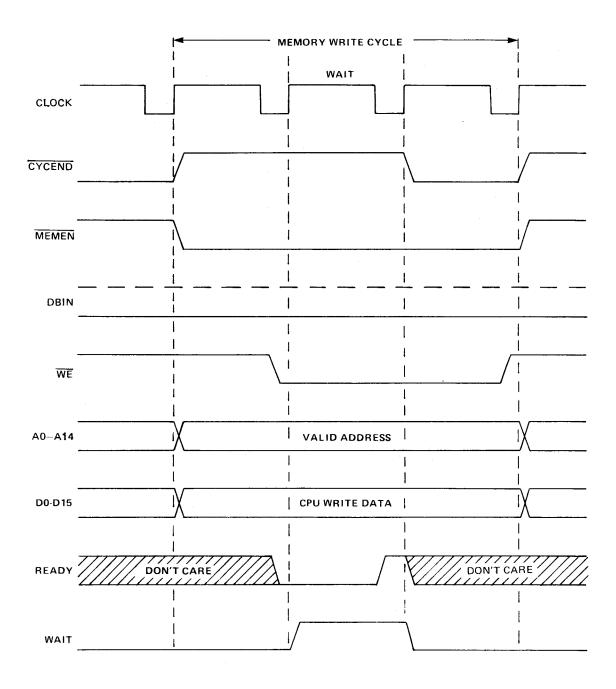

**3.2.2 MEMORY WRITE CYCLE.** Figure 3-4 shows the timing for a memory write machine cycle with no wait states. At the start of a memory write cycle,  $\overline{\text{MEMEN}}$  becomes active with a valid address applied to the address bus.  $\overline{\text{WE}}$  becomes active (low) with the first negative-going clock after  $\overline{\text{MEMEN}}$  becomes active;  $\overline{\text{WE}}$  becomes inactive with the negative-going clock preceding the end of the memory cycle. DBIN remains inactive throughout the memory write cycle. At the end of the memory cycle,  $\overline{\text{MEMEN}}$  becomes inactive. As in the memory read cycle, if no wait states are required, READY must be high before the second positive-going clock of the write cycle. CYCEND may be used by an external device to indicate that the CPU has completed the current memory cycle.

**3.2.3 READ/WRITE CONTROL WITH DBIN.** In some memory systems, it may be desirable to have READ and WRITE control signals active during the full memory cycle. Figure 3-5 shows how the READ and WRITE signals can be generated. Any cycle in which  $\overline{\text{MEMEN}} = 0$  "AND" DBIN = 0 is a memory write cycle.

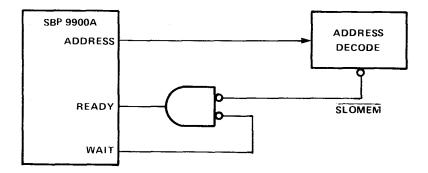

**3.2.4 SLOW MEMORY.** Timing compatibility between slow memories and the SBP 9900A can be achieved through invocation of SBP 9900A wait states. If both minimized system power dissipation and maximized system throughput are coexistent designal goals, a compromise system solution can be achieved by selecting slow memories for their general low power dissipation characteristics, and by invoking SBP 9900A wait states to match SBP 9900A memory reference timing to the requirements of the memory. This allows the SBP 9900A to maximize system throughput by operating at a higher speed when performing non-memory operations. To support invocation of SBP 9900A wait states, both READY and WAIT signals (similar in function to other microprocessors) are used to synchronize the speed of the SBP 9900A with that of slow memories.

Figure 3-3. Timing for Three Back-to-Back Memory Read Cycles

Figure 3-4. Memory Write Cycle Timing

Figure 3-5. READ/WRITE Generation

The wait state timing for memory read and memory write cycles is shown in Figures 3-6 and 3-7 respectively. During both memory read and memory write cycles, READY is sampled on the second positive-going clock of each memory cycle. If READY is not active when sampled, the SBP 9900A enters the wait state, holds the address and data buses at their present values, and activates ( $\uparrow$  high) the WAIT status signal. When an activated (high) READY signal is sampled by a positive-going clock, the SBP 9900A exits the wait state, deactivates ( $\downarrow$  low) the WAIT status signal, and resumes normal completion of the memory cycle. Note that  $\overrightarrow{CYCEND}$  comprehends wait states and remains a valid indication of when the present machine cycle terminates with the simultaneous initialization of the next machine cycle.

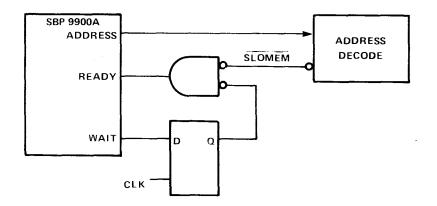

If one wait state is required to synchronize the speed of the SBP 9900A with all segments of a given memory system, then the WAIT output may be connected directly to the READY input. Note that for invocation of a single wait state, the WAIT output satisfies all of the timing requirements for the READY input. Figure 3-8 shows the connection of the WAIT output to the READY input for invocation of one wait state whenever a slow speed memory segment is addressed. For example, if memory addresses  $8000_{16}$  through FFFE<sub>16</sub> select a memory segment implemented with slow speed devices, the external address decode logic may generate a slow memory identification signal (SLOMEM = A0) to enable the external wait-state-request logic. Figure 3-9 shows how two consecutive wait states may be invoked to synchronize the speed of the SBP 9900A with a slow speed memory segment. In this case, the propagation of the active WAIT output to the READY input is delayed through a D-type flip-flop by one clock period.

**3.2.5 MEMORY ACCESS-TIME CALCULATION.** The maximum allowable memory device access time  $(t_{ACC})$  for an SBP 9900A compatible memory system can be calculated through the formula:

$$t_{ACC} = (2 + n) t_{CY} - t_{PLH} - t_D - t_{su}$$

where n equals the number of invoked wait states and  $t_{CY}$  equals the clock period of the SBP 9900A. For maximum design flexibility,  $t_{CY}$  may range anywhere from its rated guaranteed minimum (333 ns) to infinity (clock completely stopped at either logic-level high or low). The memory control signals and address bus, in reference to the memory-read cycle timing shown in Figure 3-6, become stable  $t_{PLH}$  nanoseconds after the positive-going clock which initiates the cycle. The propagation delay ( $t_D$ ) effects of address decoding, memory buffering, and control signal gating, is system dependent and can range anywhere from zero nanoseconds to whatever value is indicated. Memory-read data must be stable at the SBP 9900A's data bus inputs  $t_{SU}$  nanoseconds prior to the positive-going clock which terminates the memory cycle.

Figure 3-6. Memory-Read Cycle Timing

Figure 3-7. Write Memory Cycle Timing with One Wait State

Figure 3-8. Single Wait State for Slow Memory

,

Figure 3-9. Double Wait States for Slow Memory

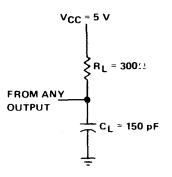

Time  $t_{PLH}$ , as defined above, is composed of two worst case additive components: the turn-off time  $t_{OFF}$  associated with a particular SBP 9900A open-collector output transistor, plus the associated bus turn-on time  $t_{RC}$ . Time,  $t_{RC}$ , is a function of the open-collector pull-up resistor ( $R_L$ ) charging the bus load capacitance ( $C_L$ ) to achieve a switching threshold of 1.5 volts. Time,  $t_{RC}$ , can be calculated from the formula:

$$f(R_{L} C_{L}) = 1.5 \text{ volts} = V_{\text{final}} [1 - e^{-(t_{R_{L}C_{L}}/R_{L}C_{L})}]$$

$$1.5 = 5 [1 - e^{-(t_{R_{L}C_{L}}/R_{L}C_{L})}]$$

$$\frac{1.5 - 5}{5} = (-0.7) = -e^{-(t_{R_{L}C_{L}}/R_{L}C_{L})}$$

$$(0.7) = e^{-(t_{R_{L}C_{L}}/R_{L}C_{L})}$$

$$0.7 = \frac{1}{e^{+(t_{R_{L}C_{L}}/R_{L}C_{L})}}$$

$$0.7 e^{t_{R_{L}C_{L}}/R_{L}C_{L}} = 1$$

$$e^{t_{R_{L}C_{L}}/R_{L}C_{L}} = 1$$

$$e^{t_{R_{L}C_{L}}/R_{L}C_{L}} = 1 = \text{In} (1.429) = 0.357$$

$$\frac{t_{R_{L}C_{L}}}{R_{L}C_{L}} = 0.357$$

$$t_{R_{I}}C_{L} = 0.357 R_{L}C_{L}$$

Since time  $t_{PLH}$  for each SBP 9900A output has been characterized under circuit load conditions where  $R_L = 300 \Omega$  and  $C_L = 150 \text{ pF}$ , the relationship where  $t_{R_LC_L} = 0.357 \text{ R}_LC_L$  can be used to recalculate  $t_{PLH}$  where actual, in system, SBP 9900A load circuit parameters depart from the characterization model. For example, the maximum time  $t_{PLH}$  for the SBP 9900A output DBIN is 160 ns with the load circuit parameters  $R_L = 300 \Omega$  and  $C_L = 150 \text{ pF}$ . If, however, actual in system circumstances show  $R_L = 300 \Omega$  and  $C_L = 25 \text{ pF}$ , then time  $t_{PLH}$  for DBIN can be recalculated as follows:

$$t_{PLH} = t_{OFF} + t_{RL}C_{L}$$

$$t_{PLH} = 160 \text{ ns when } R_{L} = 300 \Omega \text{ and } C_{L} = 150 \text{ pF}$$

$$t_{OFF} = 160 \text{ ns} - t_{RL}C_{L}$$

$$t_{RL}C_{L} \times 0.357 \text{ R}_{L}C_{L}$$

$$= 0.357 (300) (150 \cdot 10^{-12})$$

$$= 16065 \cdot 10^{-12}$$

$t_{R_LC_L} = 16.065 \text{ ns}$

therefore:

$t_{OFF} = 160 - 16.065$

$t_{OFF} = 143.935$

With  $R_L = 300 \Omega$  and  $C_L = 25 \text{ pf}$ ,

$$t_{\text{PLH}} = 143.935 + 0.357 \,(300) \,(25 \cdot 10^{-12})$$

$$= 143.935 + 2.678$$

and t<sub>PLH</sub> becomes 147 ns.

Therefore by adjusting the load capacitance (CL) from 150 pf to 25 pf, time  $t_{PLH}$  for DBIN improves from 160 ns to 147 ns.

Table 3-1 and Figure 3-10 show how memory device access time  $t_{ACC}$  varies as a function of RL and CL for an unbuffered SBP 9900A memory system.

#### **TABLE 3-1. MAXIMUM AVAILABLE MEMORY ACCESS TIME**

when:

n = 0 wait states $t_{CY} = 333 \text{ ns}$  $t_{SY} = 65 \text{ ns}$  $t_{PLH} (Address Bus) = 130 \text{ ns}$  $t_D = 41 \text{ ns}$

| $\mathbf{R}_{\mathbf{L}}(\Omega)$ | С <sub>L</sub> (рf) | t <sub>RLCL</sub> (ns) | Address Bus<br>tpLH (ns) | Max. t <sub>ACC</sub> (ns) |

|-----------------------------------|---------------------|------------------------|--------------------------|----------------------------|

| 300                               | 25                  | 2.7                    | 116.5                    | 444                        |

| 300                               | 50                  | 5.4                    | 119.2                    | 441                        |

| 300                               | 100                 | 10.8                   | 124.6                    | 436                        |

| 300                               | 150                 | 16.2                   | 130                      | 431                        |

| IK                                | 150                 | 54.0                   | 167.8                    | 393                        |

| 3K                                | 150                 | 162.0                  | 275.8                    | 285                        |

| 5K                                | 150                 | 270.0                  | 383.8                    | 177                        |

| 7K                                | 150                 | 378.0                  | 491.8                    | 69                         |

| 8K                                | 150                 | 432.0                  | 545.8                    | 15                         |

| 10 <b>K</b>                       | 150                 | 540.0                  | 653.8                    | (-93)                      |

| 10 <b>K</b>                       | 100                 | 360.0                  | 473.8                    | 87                         |

| 10 <b>K</b>                       | 50                  | 180.0                  | 293.8                    | 267                        |

| 10 <b>K</b>                       | 25                  | 90                     | 203.8                    | 357                        |

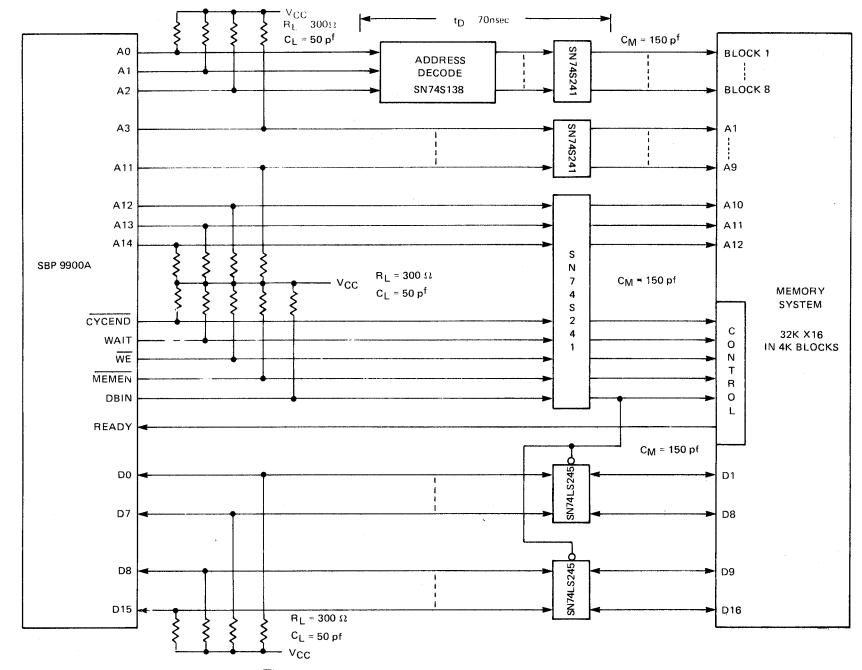

A more complex, buffered memory system is shown in Figure 3-11. Memory device access time  $t_{ACC}$  for that system can be calculated as follows:

#### Assumptions

- a. The worstcase path for calculating t<sub>ACC</sub> is through the address decoder (SN74S138) and associated buffer (SN74S241),

- b. SN74S138 and SN74S241 combined  $t_D = 70 \text{ ns}$ ,

- c.  $R_L = 300 \Omega$ ;  $C_L = 50 \text{ pf}$ ;  $C_M = 150 \text{ pf}$ ,

- d.  $t_{su} = 65 \text{ ns},$

- e.  $t_{CY} = 333$  ns, and

- f. N = 0 wait states.

#### Calculations

- (a.)  $t_{PLH}$  for A0 $\rightarrow$ A2 is 130 ns for RL = 300  $\Omega$  and CL = 150 pF.

- (b.) Recalculating  $t_{PLH}$  for  $R_L = 300 \Omega$  and  $C_L = 50 \text{ pF}$ :

$$t_{PLH} = t_{OFF} + t_{R_LC_L},$$

$$t_{OFF} = 130 - 0.357 (300) (150 \cdot 10^{-12}),$$

$$t_{OFF} = 113.9,$$

recalculated  $t_{PLH} = 113.9 + 0.357 (300) (50 \cdot 10^{-12})$ , and

recalculated  $t_{PLH} = 119$  ns.

c.

$$t_{ACC} = 2 t_{CY} - t_{PLH} - t_D - t_{SU}$$

$$= 2 (333.3) - 119 - 70 - 65$$

$$= 667 - 254$$

$t_{ACC} = 413 \text{ ns.}$

Figure 3-10. Maximum Memory Access Time vs R<sub>L</sub>, C<sub>L</sub>

Figure 3-11. SBP 9900A Buffered Memory System

Note that, in Figure 3-11, the buffered form of DBIN is used to select the direction control on the SN74LS245 bidirectional data bus buffers. This is because the SBP 9900A's output transistors sink current from two sources: 1) RL, and 2) the device(s) being asserted. With a total sink current capability of 20 mA associated with each SBP 9900A output, and  $R_L = 300 \Omega$  accounting for 17 mA, only 3 mA remain which can be supplied by the asserted device(s) without violating the 9900A's output current-sink specification.

$$I_{OL} = 20 \text{ mA} = I_{RL} + I_{device}$$

$I_{RL} = \frac{V_{CC} - V_{OL}}{R_L} = \frac{5.5 - 0.4}{300} = 17 \text{ mA}$

$I_{device} = 20 - 17 = 3 \text{ mA}$

Therefore, using DBIN directly to drive the SN74S241 plus both SN74LS245s would require the SBP 9900A's output DBIN transistor to sink 23 mA [( $I_R = 17$ ) plus (3  $I_{device} = 3(2) = 6$ )] in violation of its specified capability. Further note that the buffered SBP 9900A memory system of Figure 3-11 offers a convenient, 3-state means through which the SBP 9900A can be isolated from the memory system for purposes of effecting either block, clock-stopped, or transparent DMA as described in Section 3.6.

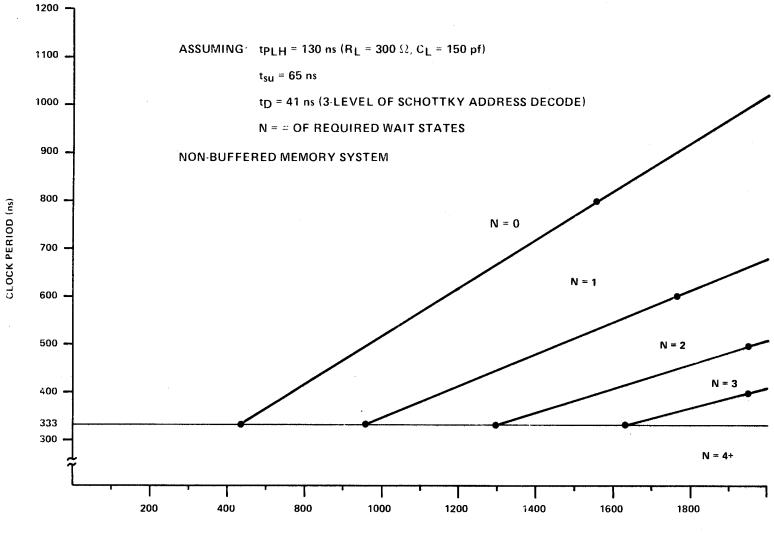

**3.2.6** WAIT STATE CALCULATION. For a memory system with given t<sub>ACC</sub> characteristics, synchronization to the SBP 9900A may be accomplished by invoking SBP 9900A wait states. The number of invoked wait states (n) can be calculated through the formula:

$$n = \frac{t_{ACC} + t_{PLH} + t_D + t_{SU} - 2 t_{CY}}{t_{CY}}$$

where  $t_{PLH}$ ,  $t_D$ ,  $t_{SU}$ , and  $t_{CY}$  are as defined in Section 3.2.5 and shown in Figure 3-6. This approach can result in a non-integer value for "n". In that case, "n" must either be rounded to the next higher integer (i.e.,  $n = 1.337 \rightarrow n = 2$ ) or the parameters  $t_{PLH}$ ,  $t_D$ , and  $t_{CY}$  must be adjusted such that the calculated value of "n" becomes an integer. Time  $t_{CY}$  can be adjusted by varying the clock frequency of the SBP 9900A. Figure 3-12 shows memory access time ( $t_{ACC}$ ) for n = 0, 1, 2, 3 memory wait states.

#### 3.3 STATIC MEMORY

Static RAMs, PROMs, and ROMs are easily interfaced to the SBP 9900A.

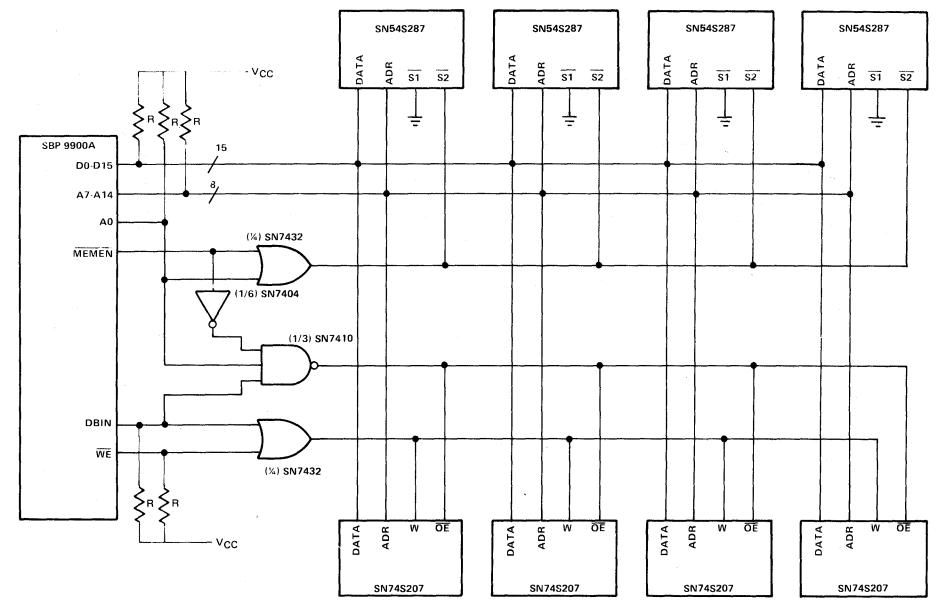

**3.3.1 STATIC MIXED MEMORY.** The static 512-word by 16-bit memory system shown in Figure 3-13 is composed of one 256-word bank of SN54S287 PROMs and one 256-word bank of SN74S207 RAMs. When MEMEN is active (low), A0 is used to enable either the PROM memory bank or the RAM memory bank. If A0 is low, the PROMs are selected; if A0 is high the RAMs are selected. A7 through A14 select 1 of 256 words within the enabled PROM or RAM memory bank. Since the full addressing reach of the SBP 9900A is not required to support this particular memory system, A1 through A6 are not used.

When the RAM memory bank is enabled, DBIN is used to select the I/O mode of the SN74S207s. If DBIN is high, the RAMs bidirectional I/O is selected to the output (read) mode; if DBIN is low, the RAMs I/O is selected to the input (write) mode. When DBIN is low, WE is allowed to access the SN74S207s write control.

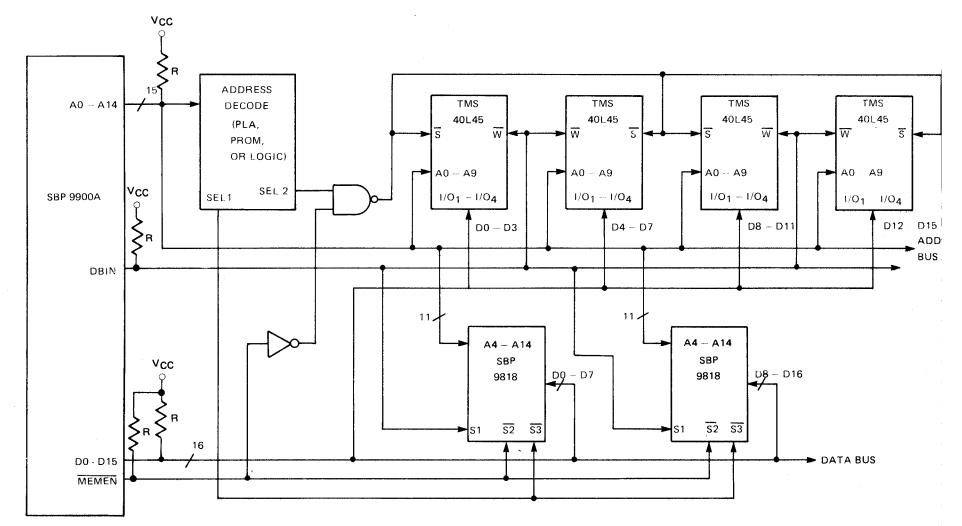

The I<sup>2</sup>L SBP 9818 ROM and TMS 40L45 memory system of Figure 3-14 also uses DBIN to distinguish between READ/WRITE RAM operations.

ACCESS TIME (nsec)

Figure 3-12. Memory Wait Time for Slow Memory

Figure 3-13. Static Mixed Memory

Figure 3-14. Memory System Using SBP 9818 I<sup>2</sup>L ROM and TMS 40L45 RAM

**3.3.2 STATIC MEMORY TIMING AND LOADING.** The memory timing of the SBP 9900A is compatible with the requirements of most standard static memory devices. Most bipolar static memory devices are fast enough to completely eliminate the need to invoke wait states. In that case, the READY input of the SBP 9900A may be permanently forced to the logic-level high polarity.

To minimize bus loading, the outputs of most memory devices can be placed, when not enabled, in the high impedance state. Each output of the SBP 9900A is capable of sinking a cumulative current of 20 mA. For logic-level low, this cumulative sink current is composed of that current sourced by the enabled memory device plus that current sourced by the open-collector pull-up resistor ( $R_L$ ) that is user-wired to each SBP 9900A output. Through proper choice of the open-collector pull-up resistors value ( $R_L$ ), the SBP 9900A can be tailored to the input-voltage/current requirements of most 5-volt memory devices. There is a tradeoff however, between pull-up resistance ( $R_L$ ) versus memory bus rise time, power dissipation, and sourcing ability. As a general rule, the smaller the value of  $R_L$ , the shorter the memory bus rise time, the higher the power dissipation, and the fewer memory inputs that can be sourced. The larger the value of  $R_L$ , the longer the memory bus rise time, the less power dissipation, and the more memory inputs that can be sourced. Consideration must also be given to minimum and maximum input voltages for the high or low level inputs to a particular memory device. A guide to selection of appropriate pull-up resistor values is given in Section 8.2. Due to the large capacitances and increased sourcing demands imposed by some memory systems, it may become desirable to use buffers external to the SBP 9900A to decrease propagation delays and provide the sourcing capability needed. Texas Instruments manufactures a variety of buffer circuits compatible with the SBP 9900A. The SN54LS245 noninverting, bidirectional octal buffer with 3-state outputs is an example.

# 3.4 OTHER MEMORIES

Because of its static I<sup>2</sup>L implementation, the SBP 9900A is recommended for use with static memory systems. However, the SBP 9900A is also completely capable of use with dynamic memory systems. A complete discussion of the use of dynamic memories with the SBP 9900A is contained in Appendix G.

## 3.5 MEMORY PARITY

Parity or other error detection/correction schemes are often used to minimize the effects of memory errors. Error detection schemes such as parity are used to indicate the presence of bad data, while error correction schemes correct single or multiple errors.

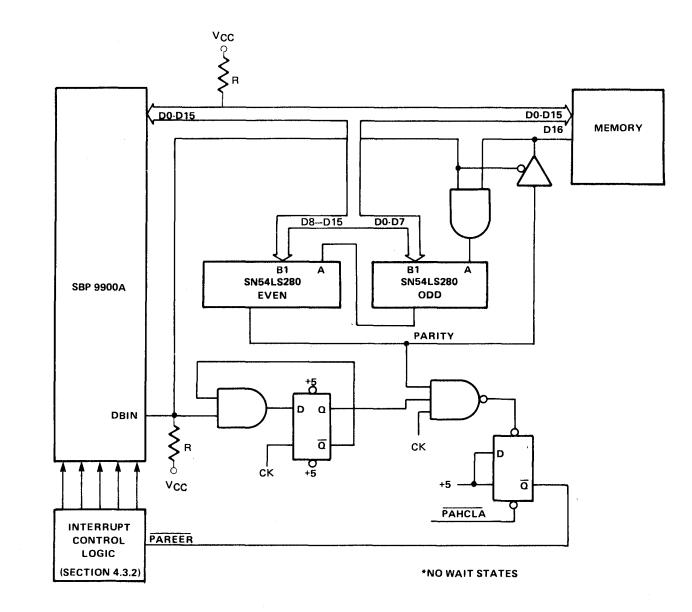

The SN54LS280 parity generator/checker can be used to implement memory parity in an SBP 9900A system. The system in Figure 3-15 uses two SN54LS280 circuits to generate and check odd memory parity. During memory write cycles, the generated parity bit is output to bit D16 of the memory. During memory read cycles, the parity is checked and an interrupt (PARERR) is generated if the parity is even.

It should be noted that a faulty memory word will already have been used by the SBP 9900A as an op code, address, or data before the interrupt is generated. For example, an error in bit 8 of the CLR op code will cause the SBP 9900A to branch unconditionally. Consequently when the interrupt is serviced, there will be no linkage to the portion of the program at which the error occurs. A diagnostic routine can often isolate such errors by scanning the memory and checking parity under program control. An error in the diagnostic itself can be extremely difficult to isolate. However an external address register, such as the SN54S299, clocked by IAQ can be used to retain program linkage under the above circumstances. When a parity error is detected, the SN54S299 is frozen, thereby retaining the address of the instruction during which the parity error occurred.

Figure 3-15. Memory Parity Generator Checker

# **3.6 DIRECT MEMORY ACCESS**

The SBP 9900A controls CRU-based I/O transfers between the memory and peripheral devices. Data must pass through the SBP 9900A during these program driven I/O transfers; the SBP 9900A may need to be synchronized with the I/O device by interrupts or status bit polling.

Some I/O devices, such as disk units, transfer large amounts of data to or from memory. Program driven CRU-based I/O can require relatively long response times, high program overhead, or complex programming techniques. Consequently, direct memory access (DMA) is used to permit the I/O device to transfer data to or from memory without CPU intervention. DMA can result in improved I/O response time and system throughput, especially for block data transfers. The DMA control circuitry is somewhat more expensive and complex than the economical CRU I/O circuitry and should be used only when required.

SBP 9900A based DMA can take place in several operational modes: the block mode utilizing the HOLD/HOLDA facilities of the SBP 9900A, the block mode utilizing the SBP 9900A's static clock-stopping capability, and the transparent mode utilizing those conditions under which the SBP 9900A will not require communication with the memory system. So called "cycle stealing" DMA modes are discussed herein as a subset of the block DMA modes.

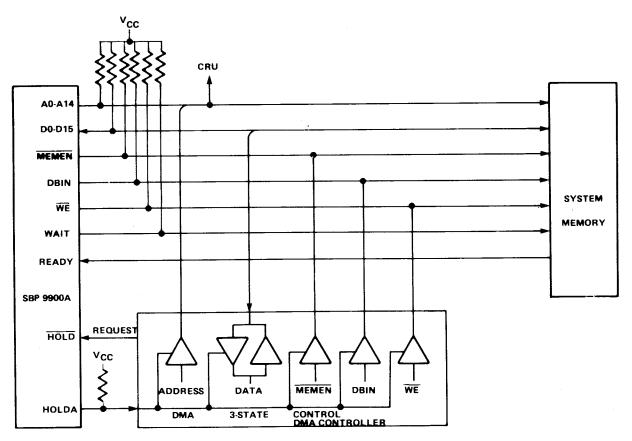

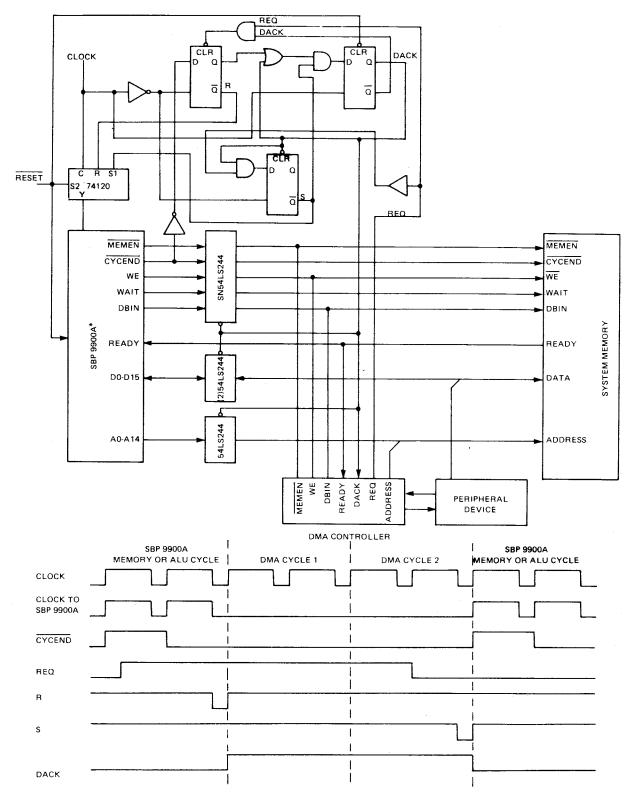

**3.6.1 HOLD**/**HOLDA BLOCK DMA.** SBP 9900A based block DMA may utilize the HOLD and HOLDA facilities. An external DMA controller, as shown in Figure 3-16, activates (low) the HOLD input of the SBP 9900A whenever an I/O device requires direct communication with the memory system. At the beginning of the next

Figure 3-16. HOLD/HOLDA Block DMA

non-memory cycle, the SBP 9900A enters the hold state and acknowledges the HOLD directive (request) by activating ( $\uparrow$  high) HOLDA. The maximum latency time from the assertion of HOLD to the activation of HOLDA is the sum of one clock cycle plus three back-to-back memory cycles. Therefore a system with no invoked wait states has a maximum HOLD to HOLDA latency of seven clock periods. Activation of HOLDA indicates that the address bus, data bus, DBIN signal, CYCEND signal, WE signal, and MEMEN signal have been pulled to the logic-level high polarity. Consequently, the DMA controller has the "go-ahead" to generate the proper memory address and appropriately timed control signal so that the I/O device may communicate directly with the memory system free from possible SBP 9900A interference. The I/O device can use the memory system for one data transfer (cycle stealing DMA) or multiple data transfers (block DMA). When the memory communication requirements of the I/O device have been satisfied, the DMA controller releases HOLD and normal SBP 9900A operations resume. The SBP 9900A's HOLD and HOLDA timing is shown in Figure 3-17.

**3.6.2 CLOCK-STOPPED BLOCK DMA.** SBP 9900A based block DMA can use the static clock-stopping capability of the SBP 9900A. An external DMA controller, as in the buffered SBP 9900A DMA system shown in Figure 3-18, can gain access to the memory system by 1) isolating the SBP 9900A from the memory bus via the 3-state buffers and 2) stopping the SBP 9900A's clock at the logic-level low polarity.\* The REQ signal from the DMA controller is synchronized with the SBP 9900A to halt the SBP 9900A's clock after the completion of the current machine cycle (ALU or Memory Cycle). Concurrently with halting the SBP 9900A's clock, DACK is

Figure 3-17. SBP 9900A Hold Timing

<sup>\*</sup>The SBP 9900A's static clock may be indefinitely stopped at either the logic-level high or low polarity. It is a function of this example only which requires the SBP 9900A's clock to be stopped while at the logic-level low polarity.

\*All outputs must be supplied with an open-collector pull-up resistor,

Figure 3-18. Clock-Stopped Block DMA

asserted and the memory bus is 3-stated allowing the DMA Controller to assert the memory bus. When the DMA Controller is in the final clock cycle of the last transfer, REQ is released to indicate to auxillary devices that DMA is completed and that the SBP 9900A may regain memory bus control. The clock control logic then reinitiates the SBP 9900A's clock. The maximum latency between REQ and DACK occurs when REQ just misses the high-to-low transition of the system clock to trigger the R signal which stops the SBP 9900A's clock. Assuming no memory wait states, this maximum latency amounts to two clock periods plus the low time of the clock. In a 3 MHz system this latency equals 777 ns, a 3X improvement over the HOLD/HOLDA handshake method of obtaining DMA as described in Section 3.5.1.

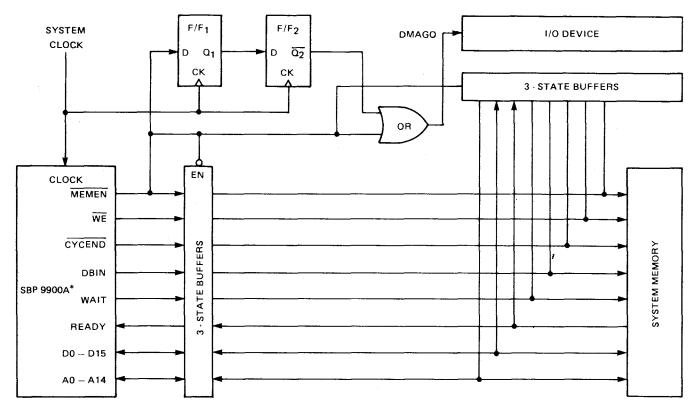

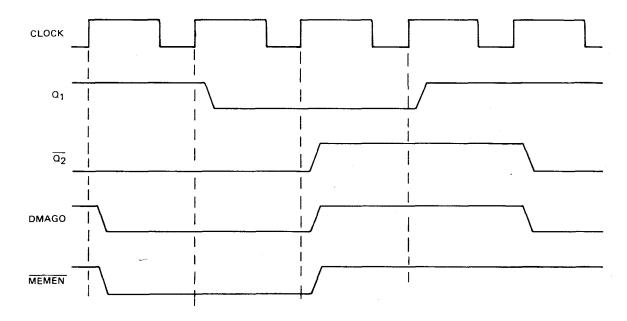

**3.6.3 TRANSPARENT DMA.** Since a minimium of one ALU cycle always directly follows deactivation ( $\uparrow$  high) of MEMEN, MEMEN may be used to define the two clock-period time window DMAGO (as shown in Figure 3-19) through which an external I/O device may communicate with the memory system free from SBP 9900A intervention. When DMAGO becomes active ( $\uparrow$  high), the device has two SBP 9900A clock periods to generate the proper memory address, with appropriately timed signals, and complete the memory transaction. *Note* that since the SBP 9900A's I/O lines are active during ALU cycles, the SBP 9900A must be isolated from the memory system via a 3-state buffer.

**3.7 MEMORY LAYOUT.** It is generally advantageous to layout memory devices as two dimensional arrays. First, positioning the devices in an orderly fashion simplifies identification of a particular memory element when troubleshooting. Second, and most important, positioning of memory arrays simplifies board layout, shortens interconnections, and generally allows a more compact and efficient utilization of board space. Crosstalk between adjacent lines in memory arrays is minimized by running address and data lines parallel to each other, and by running chip enable signals perpendicular to the address lines.

Memory devices generally require substantially greater supply currents when addressed than other times. Therefore it is important that all power and ground paths be as wide as possible. Furthermore, in order to suppress spikes in supply voltages, it is advisable to decouple supply voltages with capacitors as close as possible to the pins of the memory devices.

\*All outputs must be supplied with an open-collector pull-up resistor.

Figure 3-19. Transparent DMA

## SECTION IV INTERRUPTS

The SBP 9900A provides 15 maskable interrupt levels in addition to the  $\overrightarrow{RESET}$  and  $\overrightarrow{LOAD}$  signal-commands. The SBP 9900A has a priority ranking system to resolve conflicts between simultaneous interrupts, and a level mask to disable lower priority interrupts. Once an interrupt is recognized, the SBP 9900A performs a vectored context switch to the interrupt service routine.  $\overrightarrow{RESET}$  and  $\overrightarrow{LOAD}$  are initialized by external input signals and should not be confused with the RSET and LREX instructions which are described in Section 5.

## 4.1 **RESET**.

The RESET signal-command is normally used to initialize the SBP 9900A following power-up. When active (low), the RESET command inhibits WE and CRUCLK, allows the memory bus and control signals to be pulled to the logic-level high state, and clears both the interrupt mask and the status bit field of the status register. When the RESET command is released, the SBP 9900A fetches the restart vector from memory locations 0000 (WP) and 0002 (PC), stores the old WP, PC, and ST into the new workspace, resets all status bits to zero and starts execution at the new PC. The RESET command must be held active for a minimum of three clock periods. The RESET machine cycle sequence is shown in Figure 4-1.

| CYCLE | ТҮРЕ   | FUNCTION                                         |  |  |

|-------|--------|--------------------------------------------------|--|--|

| *     | *      | Loop While Reset is active                       |  |  |

| 1     | ALU    | Set Up                                           |  |  |

| 2     | ALU    | Set Up                                           |  |  |

| 3     | Memory | Fetch New WP, Move Status to T Reg, Clear Status |  |  |

| 4     | ALU    | Set Up                                           |  |  |

| 5     | Memory | Store Status                                     |  |  |

| 6     | ALU    | Set Up                                           |  |  |

| 7     | Memory | Store PC                                         |  |  |

| 8     | ALU    | Set Up                                           |  |  |

| 9     | Memory | Store WP                                         |  |  |

| 10    | ALU    | Set Up                                           |  |  |

| 11    | Memory | Fetch New PC                                     |  |  |

| 12    | ALU    | Set Up MAR for Next Instruction                  |  |  |

| Figure 4-1. | <b>RESET Machine Cycles</b> |

|-------------|-----------------------------|

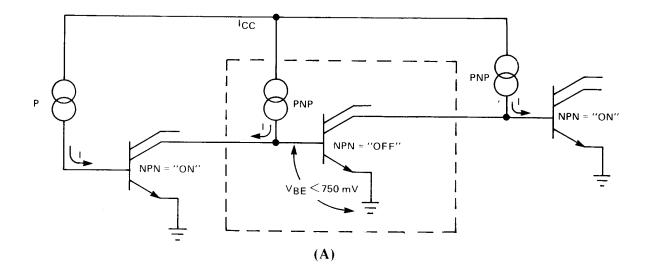

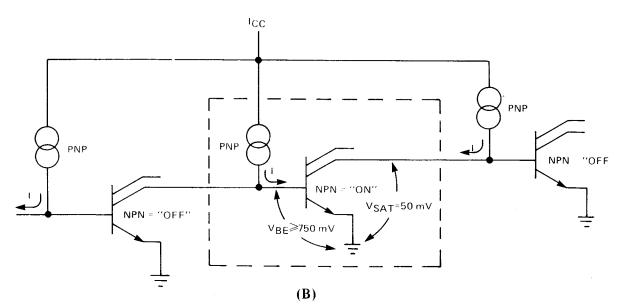

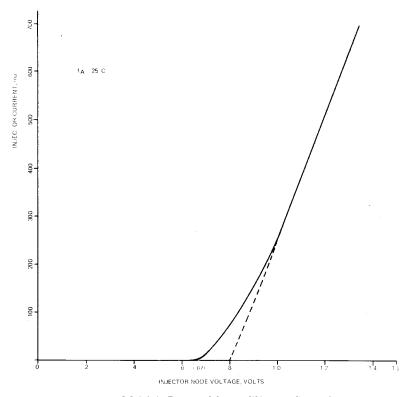

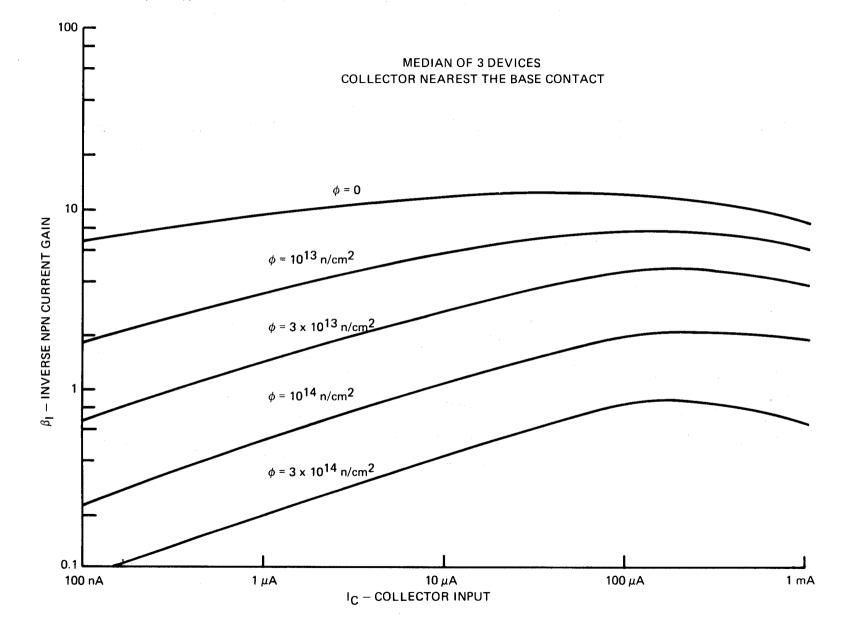

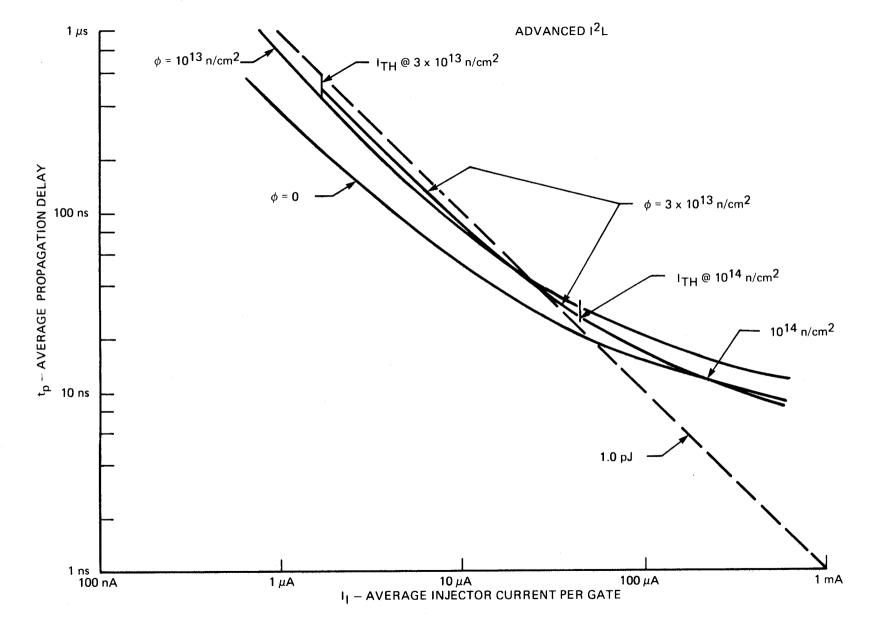

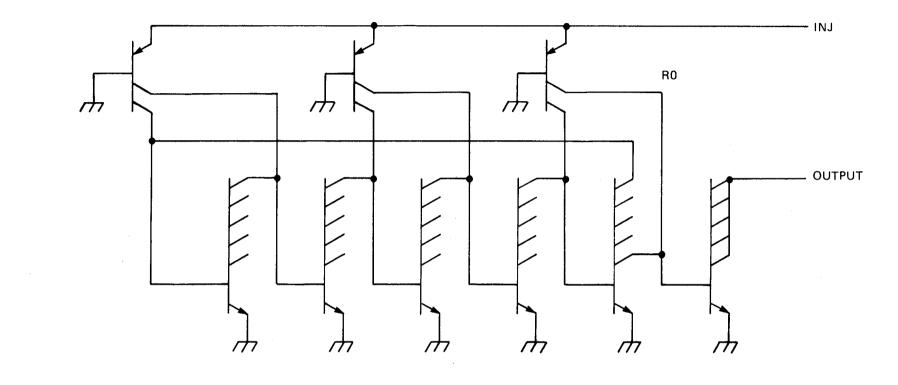

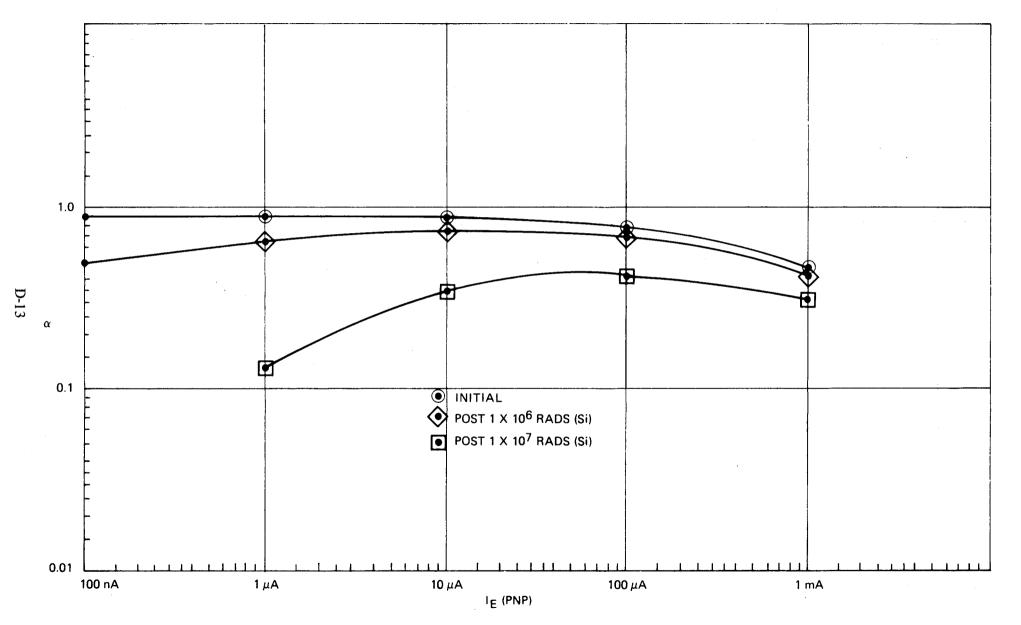

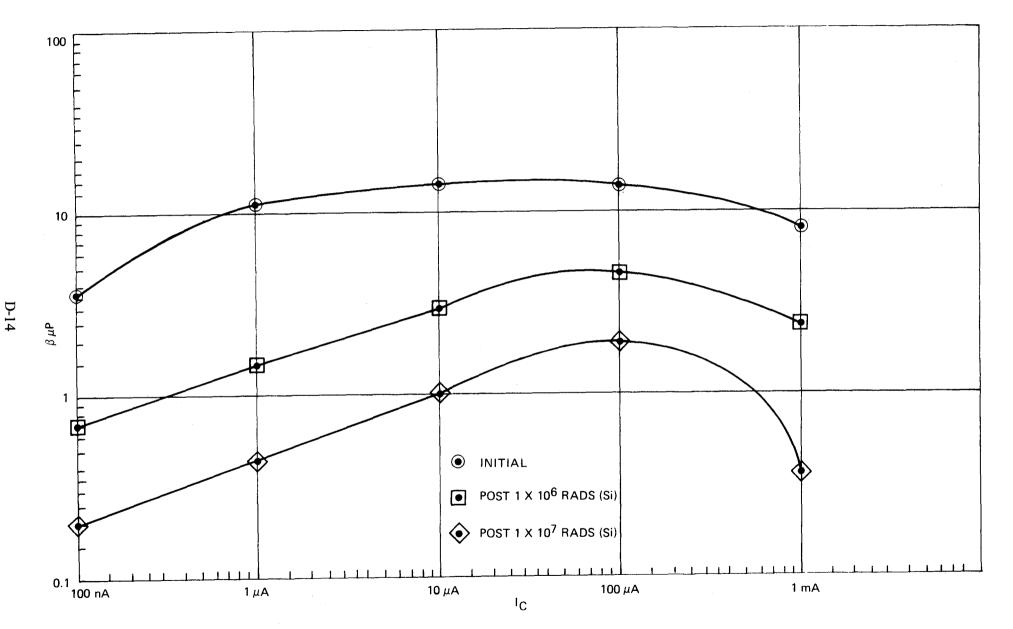

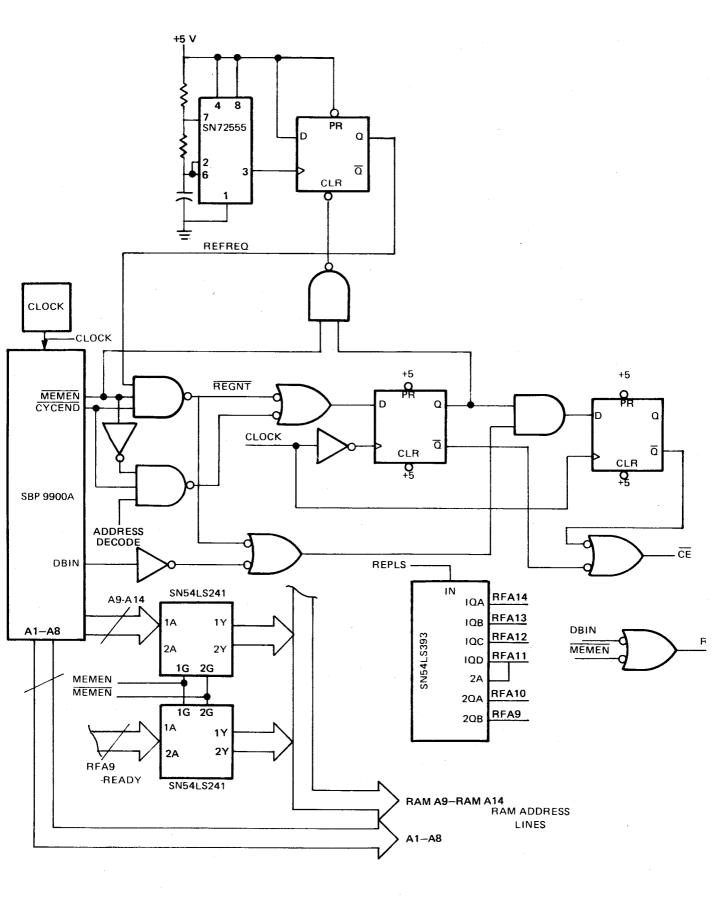

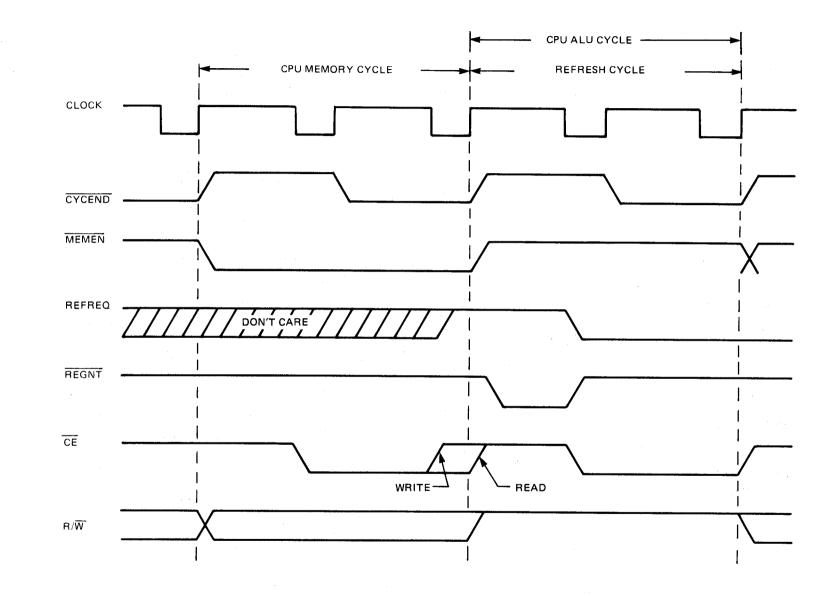

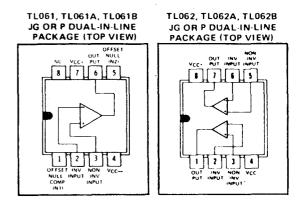

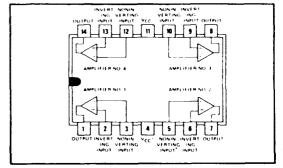

|-------------|-----------------------------|