As you are now the owner of this document which should have come to you for free, please consider making a donation of £1 or more for the upkeep of the (Radar) website which holds this document. I give my time for free, but it costs me money to bring this document to you. You can donate here <u>https://blunham.com/Misc/Texas</u>

Many thanks.

Please do not upload this copyright pdf document to any other website. Breach of copyright may result in a criminal conviction.

This Acrobat document was generated by me, Colin Hinson, from a document held by me. I requested permission to publish this from Texas Instruments (twice) but received no reply. It is presented here (for free) and this pdf version of the document is my copyright in much the same way as a photograph would be. If you believe the document to be under other copyright, please contact me.

The document should have been downloaded from my website <u>https://blunham.com/</u>, or any mirror site named on that site. If you downloaded it from elsewhere, please let me know (particularly if you were charged for it). You can contact me via my Genuki email page: <u>https://www.genuki.org.uk/big/eng/YKS/various?recipient=colin</u>

You may not copy the file for onward transmission of the data nor attempt to make monetary gain by the use of these files. If you want someone else to have a copy of the file, point them at the website. (<u>https://blunham.com/Misc/Texas</u>). Please do not point them at the file itself as it may move or the site may be updated.

It should be noted that most of the pages are identifiable as having been processed by me.

If you find missing pages, pages in the wrong order, anything else wrong with the file or simply want to make a comment, please drop me a line (see above).

It is my hope that you find the file of use to you.

Colin Hinson In the village of Blunham, Bedfordshire.

I put a lot of time into producing these files which is why you are met with this page when you open the file.

TEXAS INSTRUMENTS

# TM 990

# TM 990/1481 High—Performance CPU Modules

Volume I

# **MICROPROCESSOR SERIES<sup>™</sup>**

October 1980

# SECTION

| 1. | τνιτρ       | ODUCTION                                                     | 1 1  |

|----|-------------|--------------------------------------------------------------|------|

| 1. |             |                                                              |      |

|    | 1.1         | General1                                                     |      |

|    | 1.2         | Manual Organization 1                                        |      |

|    | 1.3         | General Specifications 1                                     |      |

|    | 1.4         | Applicable Documents 1                                       | 1-4  |

|    |             |                                                              |      |

| 2. | INST        | ALLATION AND OPERATION 2                                     |      |

|    | 2.1         | General 2                                                    | 2-1  |

|    | 2.2         | Unpacking and Inspection 2                                   | 2-1  |

|    | 2.3         | Processor Module Options 2                                   | 2-1  |

|    | -           | 2.3.1 External Interrupt Line (INT6.B-) Select (E1-E2) 2     |      |

|    |             | 2.3.2 TMS 9902 INT4- Interrupt Option (E4-E6) 2              |      |

|    | 2.4         | Controller Module Options                                    |      |

|    |             | 2.4.1 Controller Module Jumpers                              |      |

|    |             | 2.4.2 ROM Wiring Platform at U49                             |      |

|    |             | 2.4.3 Controller Module Wiring Platform for Memory Devices 2 |      |

|    |             |                                                              |      |

|    | 2.5         |                                                              |      |

|    | -           | Required Equipment                                           |      |

|    | 2.6         | Power Supply and Card Cage Connections 2                     | :-7  |

|    | 2.7         | TM 990/1481 Processor/Controller Placement and               |      |

|    | - 0         | Interconnections                                             |      |

|    | 2.8         | Typical Installation and Initialization Sequence 2           |      |

|    |             | 2.8.1 Example of TM 990/201 Board Setup 2                    |      |

|    |             | 2.8.2 Board Installation 2                                   | !-11 |

| 2  | <b>MTD1</b> |                                                              |      |

| 3. |             | G INTERACTIVE DEBUG MONITOR                                  |      |

|    | 3.1         | General                                                      | -    |

|    | 3.2         | TIBUG Commands                                               |      |

|    |             | 3.2.1 Execute Under Breakpoint (B) 3                         |      |

|    |             | 3.2.2 CRU Inspect/Change (C) 3                               |      |

|    |             | 3.2.3 Dump Memory to Cassette/Paper Tape (D) 3               |      |

|    |             | 3.2.4 Execute Command (E)                                    | 5-8  |

|    |             | 3.2.5 Find Command (F) 3                                     | 8-1  |

|    |             | 3.2.6 Hexadecimal Arithmetic (H)                             | -9   |

|    |             | 3.2.7 Load Memory from Cassette or Paper Tape (L)            | -9   |

|    |             | 3.2.8 Memory Inspect/Change, Memory Dump                     |      |

|    |             | 3.2.9 Inspect/Change User WP, PC, and ST Registers (R) 3     |      |

|    |             | 3.2.10 Execute In Single Step Mode (S)                       | 12   |

|    |             | 3.2.11 TI 733 ASR Baud Rate (T)                              |      |

|    |             | 3.2.12 Inspect/Change User Workspace (W)                     |      |

|    |             | 3.2.13 Move ALU Test to RAM and Execute (X)                  | -    |

|    |             |                                                              |      |

|    | 2 2         | 3.2.14 Start Execution at Address 1000 <sub>16</sub> (G)     |      |

|    | 3.3         | User Accessible Utilities                                    |      |

|    |             | 3.3.1 Time Delay Via TMS 9901 Clock                          |      |

|    |             | 3.3.2 Write One Hexadecimal Character to Terminal (XOP 8) 3  |      |

|    |             | 3.3.3 Read Hexadecimal Word from Terminal (XOP 9)            | -16  |

| •  | 3.4 | 3.3.4<br>3.3.5<br>3.3.6<br>3.3.7<br>3.3.8<br>TIBUG H | Write Four Hexadecimal Characters to Terminal (XOP 10)<br>Echo Character (XOP 11)<br>Write One Character to Terminal (XOP 12)<br>Read One Character from Terminal (XOP 13)<br>Write Message to Terminal (XOP 14)<br>Error Messages | 3–18<br>3–18<br>3–18<br>3–18 |

|----|-----|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 4. |     |                                                      | INSTRUCTION SET                                                                                                                                                                                                                    |                              |

|    | 4.1 |                                                      | 1                                                                                                                                                                                                                                  |                              |

|    | 4.2 |                                                      | emory                                                                                                                                                                                                                              |                              |

|    | 4.3 |                                                      | ace Concept                                                                                                                                                                                                                        |                              |

|    | 4.4 |                                                      | Register                                                                                                                                                                                                                           |                              |

|    |     | 4.4.1                                                | Logical Greater Than                                                                                                                                                                                                               |                              |

|    |     | 4.4.2                                                | Arithmetic Greater Than                                                                                                                                                                                                            |                              |

|    |     | 4.4.3                                                | Equal                                                                                                                                                                                                                              |                              |

|    |     | 4.4.4                                                | Carry                                                                                                                                                                                                                              |                              |

|    |     | 4.4.5                                                | Overflow                                                                                                                                                                                                                           |                              |

|    |     | 4.4.6<br>4.4.7                                       | Odd Parity                                                                                                                                                                                                                         |                              |

|    |     | 4.4.8                                                | Extended Operation<br>Status Bit Summary                                                                                                                                                                                           |                              |

|    | 4.5 |                                                      | ction Formats and Addressing Modes                                                                                                                                                                                                 |                              |

|    | 4.5 | 4.5.1                                                | Direct Register Addressing                                                                                                                                                                                                         |                              |

|    |     | 4.5.2                                                | Indirect Register Addressing                                                                                                                                                                                                       |                              |

|    |     | 4.5.3                                                | Indirect Register Autoincrement Addressing                                                                                                                                                                                         |                              |

|    |     | 4.5.4                                                | Symbolic Memory Addressing, Not Indexed                                                                                                                                                                                            |                              |

|    |     | 4.5.5                                                | Symbolic Memory Addressing, Indexed                                                                                                                                                                                                |                              |

|    |     | 4.5.6                                                | Immediate Addressing                                                                                                                                                                                                               |                              |

|    |     | 4.5.7                                                | Program Counter Relative Addressing                                                                                                                                                                                                |                              |

|    |     | 4.5.8                                                | CRU Bit Addressing                                                                                                                                                                                                                 |                              |

|    | 4.6 | Instruc                                              | ctions                                                                                                                                                                                                                             |                              |

|    |     | 4.6.1                                                | Format 1 Instructions                                                                                                                                                                                                              | 4-24                         |

|    |     | 4.6.2                                                | Format 2 Instructions                                                                                                                                                                                                              | 4-25                         |

|    |     | 4.6.3                                                | Format 3/9 Instructions                                                                                                                                                                                                            | 4-28                         |

|    |     | 4.6.4                                                | Format 4 (CRU Multibit) Instructions                                                                                                                                                                                               | 4-30                         |

|    |     | 4.6.5                                                | Format 5 (Shift) Instructions                                                                                                                                                                                                      |                              |

|    |     | 4.6.6                                                | Format 6 Instructions                                                                                                                                                                                                              |                              |

|    |     | 4.6.7                                                | Format 7 RTWP/Control and Floating-Point Instructions.                                                                                                                                                                             |                              |

|    |     | 4.6.8                                                | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                              |                              |

|    |     | 4.6.9                                                |                                                                                                                                                                                                                                    |                              |

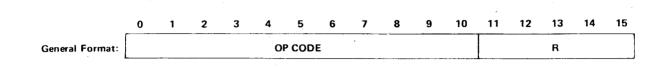

|    |     |                                                      | Formats 10 Through 17 Instructions                                                                                                                                                                                                 |                              |

|    | 1   |                                                      | Format 18 Single Register Operand Instructions                                                                                                                                                                                     |                              |

|    | 4.7 |                                                      | ction Execution Times                                                                                                                                                                                                              |                              |

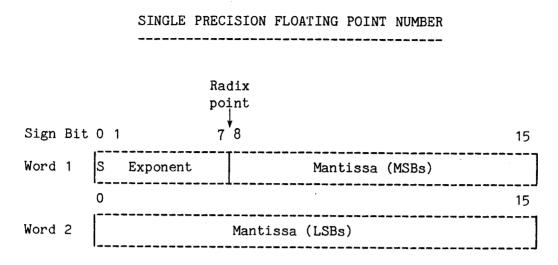

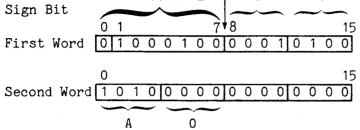

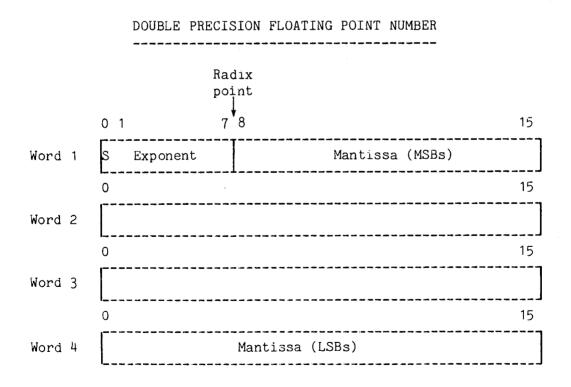

|    | 4.8 |                                                      | /1481 Floating-Point Arithmetic                                                                                                                                                                                                    |                              |

|    |     |                                                      | Floating-Point Representation                                                                                                                                                                                                      |                              |

|    |     |                                                      | Floating-Point Operations                                                                                                                                                                                                          | <del>4-</del> うう             |

|    |     |                                                      | Internal Representation of TM 990/1481 Floating-Point<br>Numbers                                                                                                                                                                   | 4-57                         |

|    |     |                                                      | <pre>FM 990/1481 Floating-Point Instruction Overview</pre>                                                                                                                                                                         |                              |

|    |     |                                                      | Sample Programs                                                                                                                                                                                                                    |                              |

|    |     | 1+0+) L                                              | 2                                                                                                                                                                                                                                  | 1-02                         |

# SECTION

|    | <ul> <li>4.9 Programming Aids</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-63<br>4-65                                                                                            |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| 5. | <pre>SOFTWARE APPLICATIONS.<br/>5.1 General<br/>5.2 Developement of Software for the TM 990/1481<br/>5.2.1 Using Floating Point Instruction Assemblers.<br/>5.2.2 Floating Point Support with Other Assemblers.<br/>5.3 Installing Software Into the TM 990/1481 System.<br/>5.4 Debugging Software on the TM 990/1481.<br/>5.5 Characteristics of Floating Point Arithmetic.<br/>5.5.1 Accuracy Considerations.<br/>5.5.2 Significant Decimal Digits.<br/>5.5.3 Range of Value.<br/>5.5.4 Interrupt Considerations.<br/>5.6 Radix Conversion.<br/>5.7 TM 990/433 Floating Point Demonstration Software.<br/>5.7.1 Accessing Demo Routines From Applications Programs.<br/>5.7.2 Machine to ASCII Conversion Routines.<br/>5.7.3 Transcendentan Functions.<br/>5.7.4 Solution of Simultaneous Equations.</pre> | 5-1<br>5-1<br>5-3<br>5-3<br>5-4<br>5-5<br>5-4<br>5-5<br>5-6<br>5-6<br>5-7<br>5-9<br>5-13                |

| 6. | <pre>I/O PROGRAMMING.<br/>6.1 General.<br/>6.2 System Description.<br/>6.3 Communications Register Unit (CRU).<br/>6.4 Loading the CRU Hardware Base Address.<br/>6.5 User Workspace.<br/>6.6 Sample Program.</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6-1<br>6-1<br>6-2<br>6-5                                                                                |

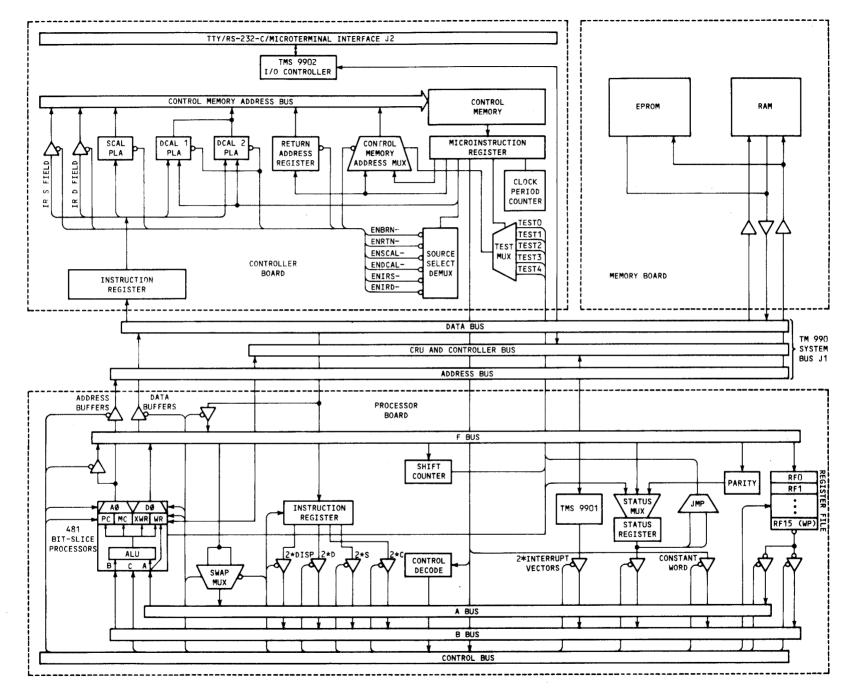

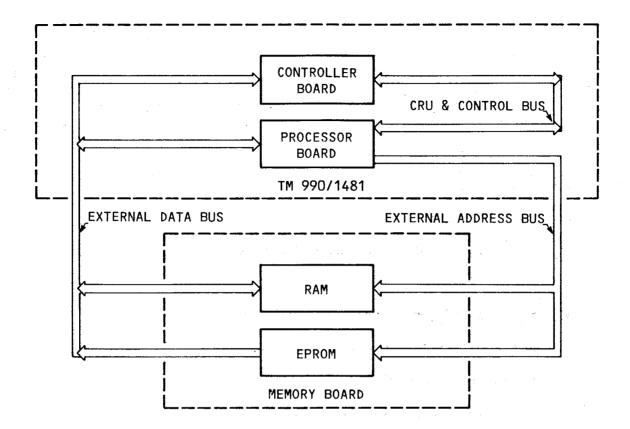

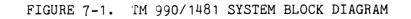

| 7. | THEORY OF OPERATION.<br>7.1 General.<br>7.2 System Block Diagram.<br>7.3 The Processor Board.<br>7.3.1 The 481 Bit-Slice Processor.<br>7.3.2 Shift Counter.<br>7.3.3 The Swap Multiplexer.<br>7.3.4 Instruction Register (IR).<br>7.3.5 Status Register and Status Logic.<br>7.3.6 Register File.<br>7.3.7 Constant Word.<br>7.3.8 A-Bus, B-Bus, and F-Bus.<br>7.3.9 Address and Data Out.<br>7.3.10 Interrupt Logic and Jump Control.<br>7.3.11 Special Control Decode Logic.                                                                                                                                                                                                                                                                                                                                 | 7-1<br>7-1<br>7-1<br>7-3<br>7-4<br>7-5<br>7-5<br>7-5<br>7-5<br>7-8<br>7-8<br>7-8<br>7-8<br>7-10<br>7-10 |

# SECTION

|    | 7.4                               | Controller Board                                                                                                                                                                                                                                                                                                                                                                                                                 | 12<br>13<br>13<br>14<br>17<br>18<br>18<br>19<br>19<br>22<br>22 |

|----|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

|    |                                   | 7.4.17 Debug Clock Options 7-2                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                |

|    |                                   | 7.4.18 Upper Memory Page Bits 7-2                                                                                                                                                                                                                                                                                                                                                                                                |                                                                |

| 8. | MICR(<br>8.1<br>8.2<br>8.3<br>8.4 | PROGRAMMING. 8-<br>General. 8-<br>Microinstruction Word. 8-<br>Clock and Sequence Control. 8-<br>3.3.1 Clock Control. 8-<br>3.3.2 Source Select. 8-<br>3.3.3 Test Select. 8-<br>Data Routing and Selection. 8-<br>3.4.1 Register File Address. 8-<br>3.4.2 A-Bus Select A. 8-<br>3.4.3 B-Bus Select B. 8-<br>3.4.4 Address output Select P. 8-<br>3.4.5 F-Bus Select F. 8-<br>8-<br>8-<br>8-<br>8-<br>8-<br>8-<br>8-<br>8-<br>8- | 1<br>1<br>2<br>2<br>3<br>4<br>5<br>5<br>6<br>7<br>7            |

|    | 8.5<br>8.6<br>8.7                 | 8.4.6Memory Control MC.8-48.4.7Constant Word.8-4Deperation Control.8-48.5.1ALU Operation Control.8-48.5.2Processor Register Control.8-48.5.3Instruction Acquisition.8-58.5.4Counter Control.8-5Status Control.8-5Special Control Field.8-6                                                                                                                                                                                       | 8<br>9<br>13<br>13<br>14                                       |

| 9. | INTE<br>9.1<br>9.2<br>9.3<br>9.4  | FACE DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                | 1<br>1<br>1                                                    |

# LIST OF ILLUSTRATIONS

# FIGURE

| <ul> <li>1-1 Typical System Configuration With TM 990/1481</li> <li>1-2 TM 990/1481 Principal Processor Components</li> <li>1-3 TM 990/1481 Principal Controller Components</li> <li>1-4 TM 990/1481 Dimensions (in inches)</li> <li>1-5 TM 990/1481 System Diagram</li> </ul>                                                                                                                                                                                        | 1–6<br>1–7<br>1–8                                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>2-1 Rom Adapter Plug Wiring.</li> <li>2-2 Memory Device Wiring Platforms at U49 and U99.</li> <li>2-3 Power Supply Connections.</li> <li>2-4 TM 990/1481 Connector/Processor Interconnections.</li> <li>2-5 TM 990/1481 and RS-232-C Terminal Connections.</li> <li>2-6 TM 990/1481 and TI 743 or 745 Terminal Connections.</li> <li>2-7 TM 990/1481 and TI 733 ASR Data Terminal.</li> </ul>                                                                | 2-4<br>2-8<br>2-8<br>2-9<br>2-10                                                                                          |

| <ul> <li>3-1 Memory Requirements for TIBUG.</li> <li>3-2 CRU Bits Inspected By C Command.</li> <li>3-3 733 ASR Module Assembly (Upper Unit) Switch Panel.</li> <li>3-4 Tape Tabs.</li> </ul>                                                                                                                                                                                                                                                                          | 3-4<br>3-7                                                                                                                |

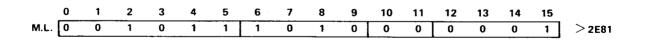

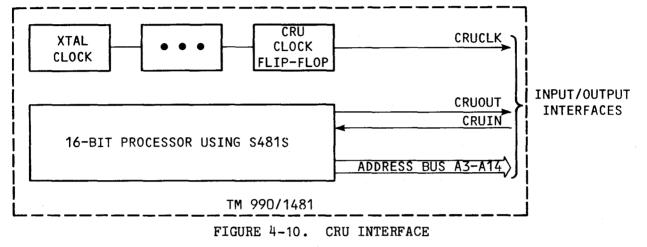

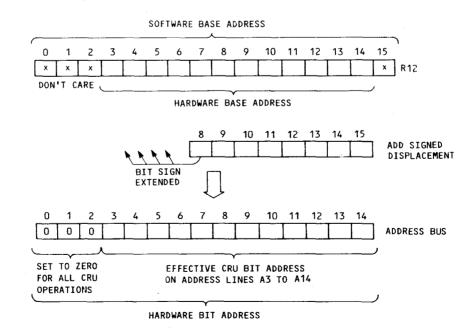

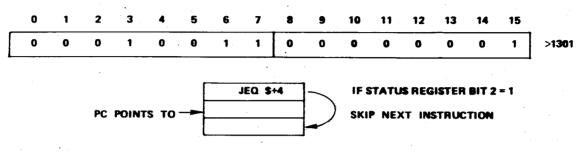

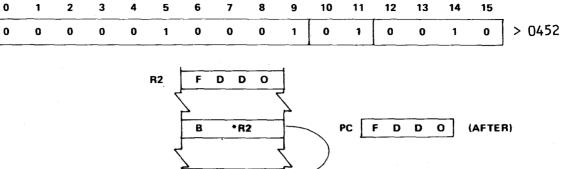

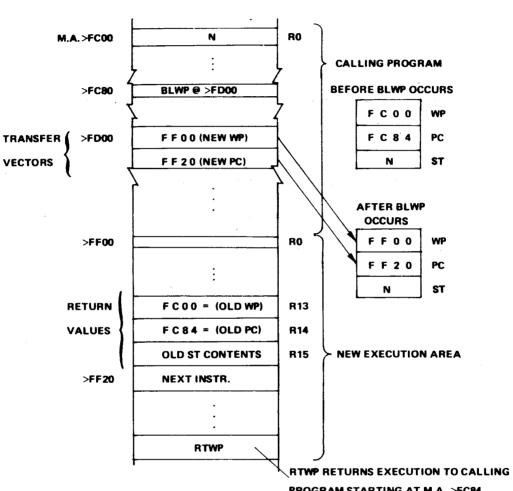

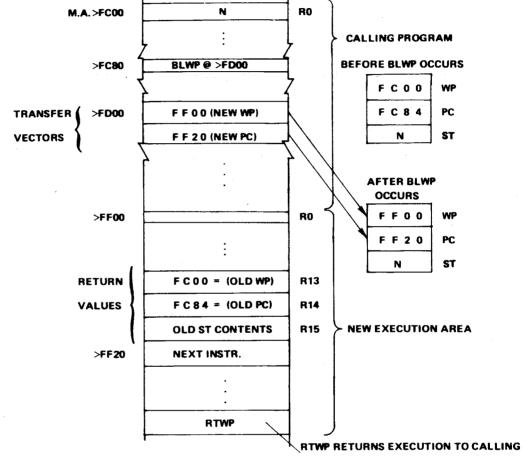

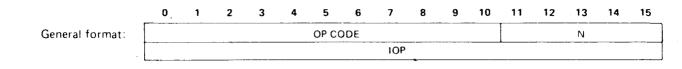

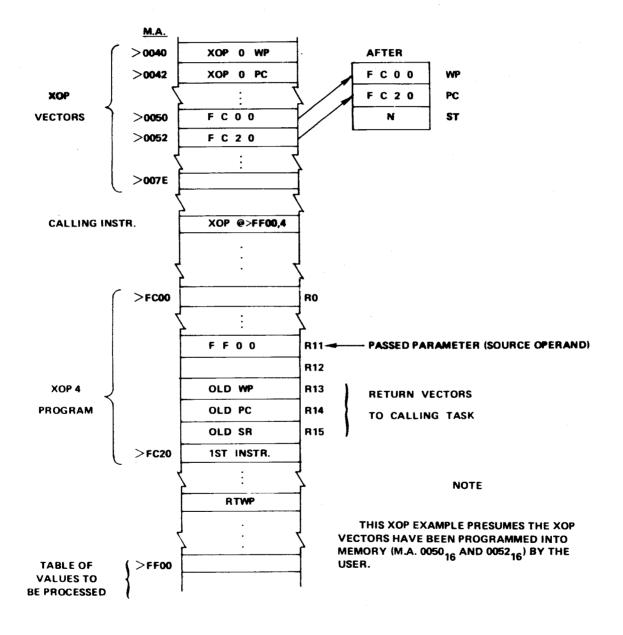

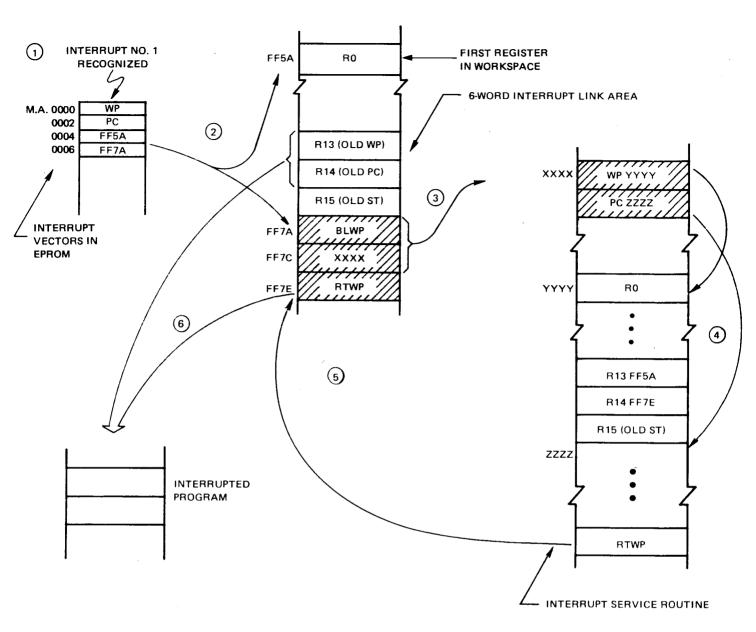

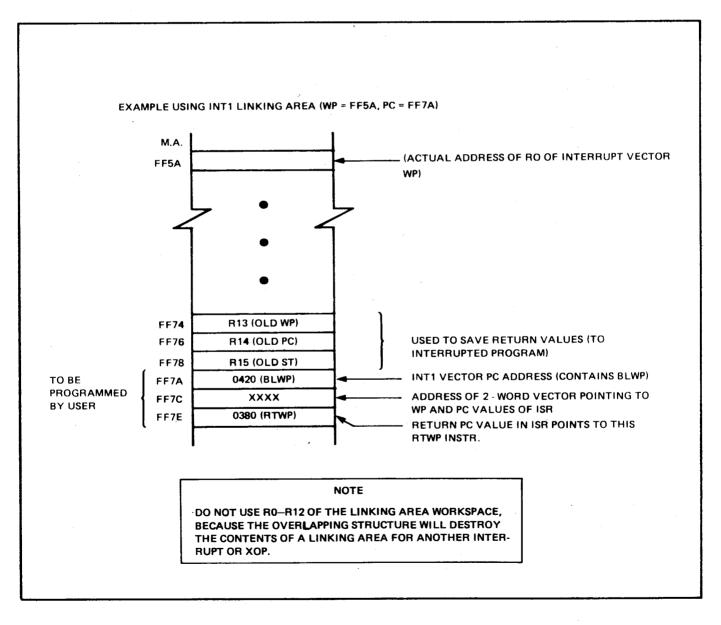

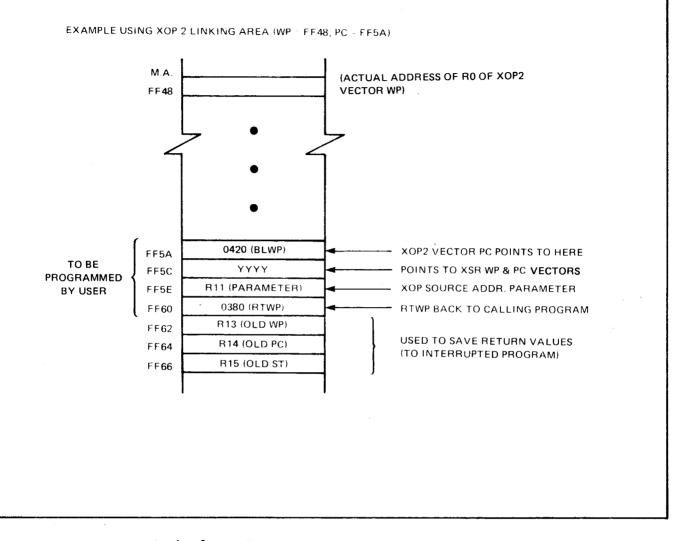

| <ul> <li>4-8 Immediate Addressing Example 1.</li> <li>4-9 Immediate Addressing Example 2.</li> <li>4-10 CRU Interface.</li> <li>4-11 CRU Bit Addressing Developement.</li> <li>4-12 Cru Bit Addressing Example 1.</li> <li>4-13 CRU Bit Addressing Example 2.</li> <li>4-14 BLWP Example.</li> <li>4-15 XOP Example.</li> <li>4-16 Interrupt Sequence.</li> <li>4-17 Six-Word Interrupt Linking Area.</li> <li>4-18 Seven-Word XOP Interrupt Linking Area.</li> </ul> | 4-3<br>4-8<br>4-10<br>4-11<br>4-12<br>4-13<br>4-14<br>4-15<br>4-16<br>4-16<br>4-16<br>4-17<br>4-8<br>4-69<br>4-70<br>4-72 |

| 5-1 Source Listing of Assembler Using Floating Point Source<br>5-2 Source Listing of Assembler Using Data Statements                                                                                                                                                                                                                                                                                                                                                  | 5–2<br>5–2                                                                                                                |

# LIST OF ILLUSTRATIONS

# FIGURE

# TITLE

# PAGE

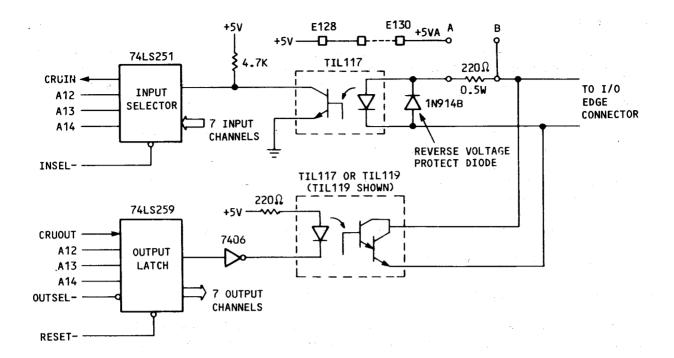

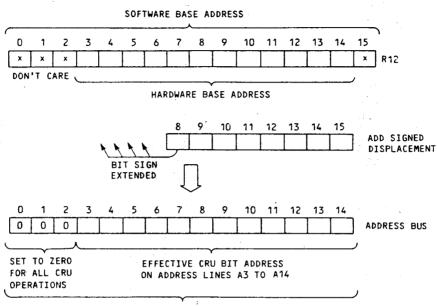

| 6-2 | TM 990/305 Port O I/O Channel<br>CRU Bit Address Development<br>Monitor Control Program                            | 6-4 |

|-----|--------------------------------------------------------------------------------------------------------------------|-----|

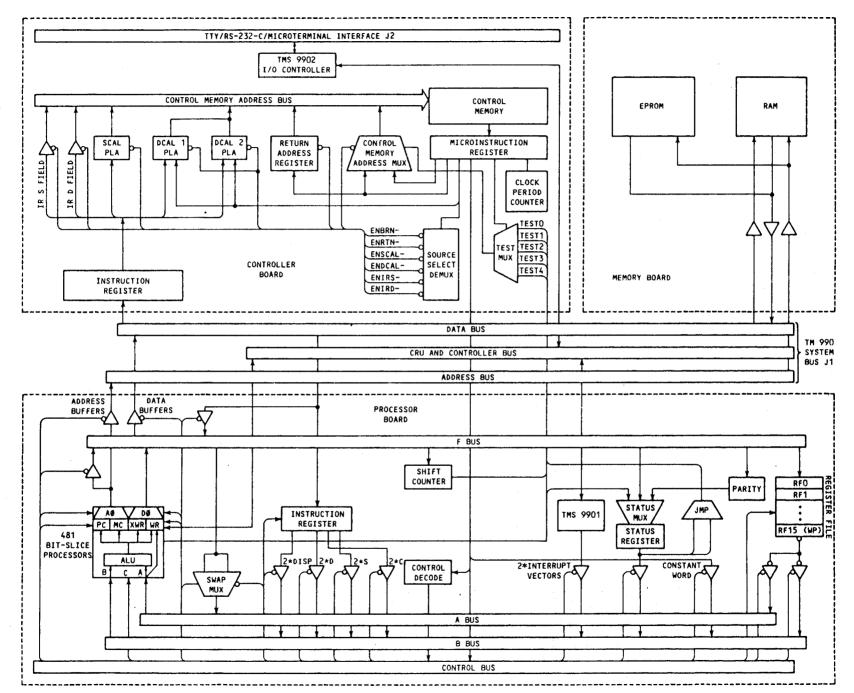

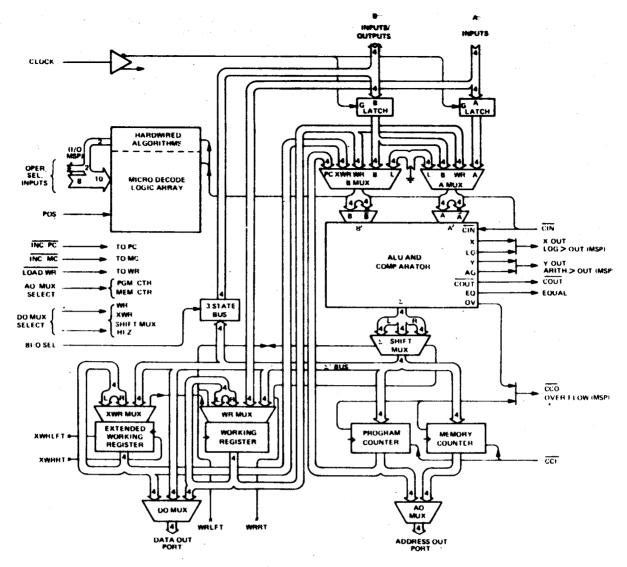

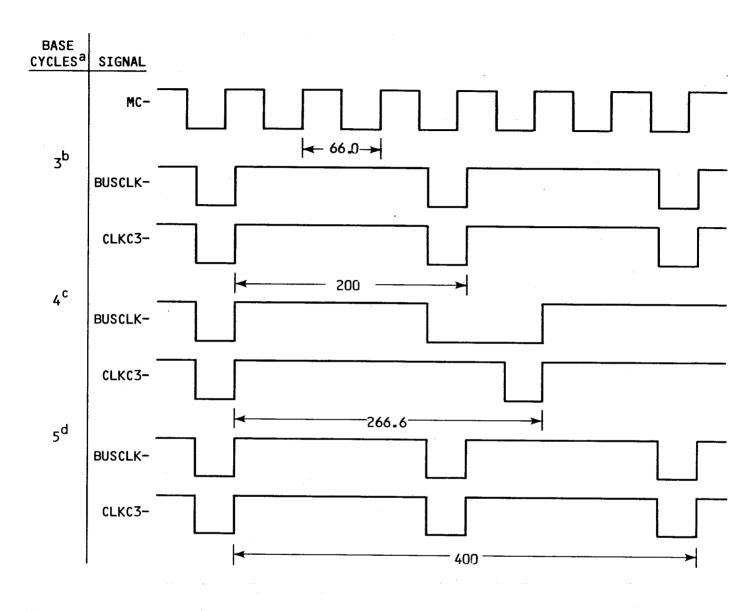

| 7-2 | TM 990/1481 System Block Diagram<br>SN74S481 Functional Block Diagram<br>Bus Clock and System Clock Timing (in ns) | 7-3 |

# LIST OF TABLES

# TABLE

| 2-1<br>2 <b>-</b> 2             | Memory Plug Wiring<br>Cable Assemblies                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                    |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| 3-1<br>3-2<br>3-3               | TIBUG Commands<br>Command Syntax Conventions<br>User Accessible Utilities                                                                                                                                                                                                                                                                                                                                                                                  | 3-3                                                                                |

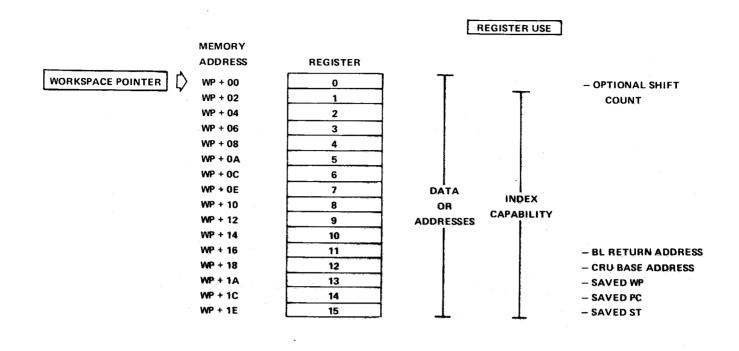

|                                 | Workspace Registers.<br>Status Register Bit Definitions.<br>Instruction Description Terms.<br>Instruction Set, Alphabetical Index.<br>Instruction Set, Numerical Index.<br>Comparison of Jumps, Branches, XOP's.<br>Data to Determine TM 990/1481 Execution Times.<br>Address Modification Factors for Instruction Execution Times.<br>Memory Access Times.<br>Preprogrammed Interrupt and User XOP Trap Vectors.<br>Interrupt and User XOP Linking Areas. | 4-6<br>4-19<br>4-20<br>4-22<br>4-35<br>4-48<br>4-52<br>4-52<br>4-52<br>4-67        |

| 5–1<br>5–2                      | Demo Routines<br>Routine Entry Points and Arguments                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                    |

| 6-1                             | TM 990/305 CRU Map                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6-3                                                                                |

| 7-1<br>7-2<br>7-3<br>7-4<br>7-5 | Status Control ROMS.<br>Decode Control ROMS (Processor and Controller).<br>SCAL PLA Entry Points.<br>PLA 2A Entry Points: DCAL', DCAL, OPCAL.<br>PLA 2B Entry Points: DCAL', DCAL, OPCAL.                                                                                                                                                                                                                                                                  | 7-11<br>7-20<br>7-22                                                               |

| 8–11<br>8–12                    | Clock ControlCMDO(1-3).<br>Source SelectCMDO(4-6).<br>TestCMDO(7-11).<br>Register File AddressCMDO(38-41).<br>A-Bus SelectCMDO(42).<br>B-Bus SelectCMDO(42).<br>Address Output SelectCMDO(46).<br>F-Bus SelectCMDO(47-49).<br>Memory ControlCMDO(50-51).<br>ALU Op CodeCMDO(52-62).<br>Counter CountrolCMDO(69-70).<br>Status ControlCMDO(71-75).<br>Special (Decode) ControlCMDO(76-80).                                                                  | 8-3<br>8-4<br>8-6<br>8-7<br>8-7<br>8-7<br>8-7<br>8-8<br>8-8<br>8-9<br>8-14<br>8-15 |

| 9-1<br>9-2<br>9-3<br>9-4        | Processor and Controller TM990 Bus Connector (P1)<br>Processor/Controller Interface Connector (P3)<br>Processor/Controller Interface Connector (P4)<br>Controller RS-232 Connector (P2)                                                                                                                                                                                                                                                                    | 9 <b>-</b> 2<br>9 <b>-</b> 3                                                       |

#### SECTION 1

#### INTRODUCTION

#### 1.1 GENERAL

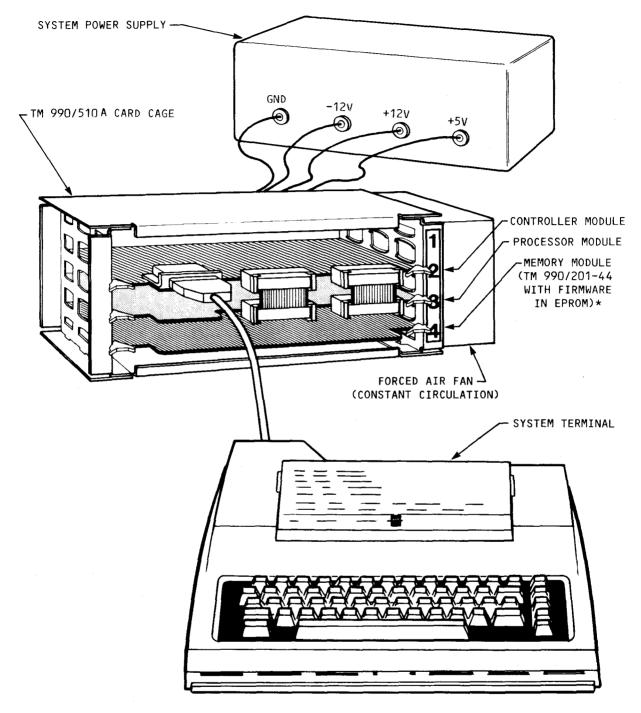

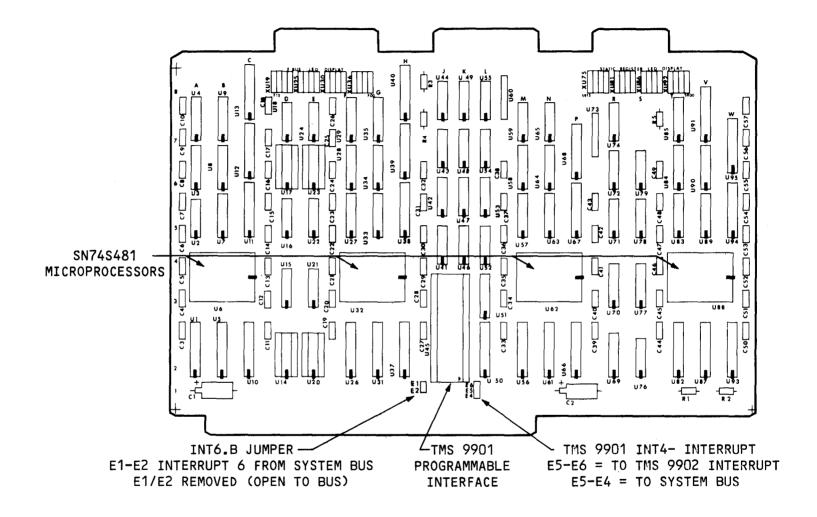

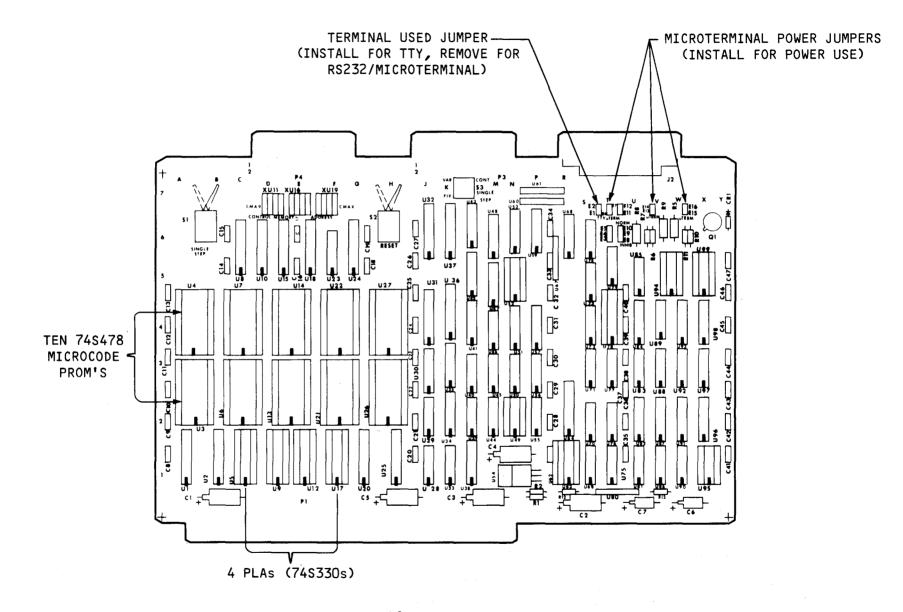

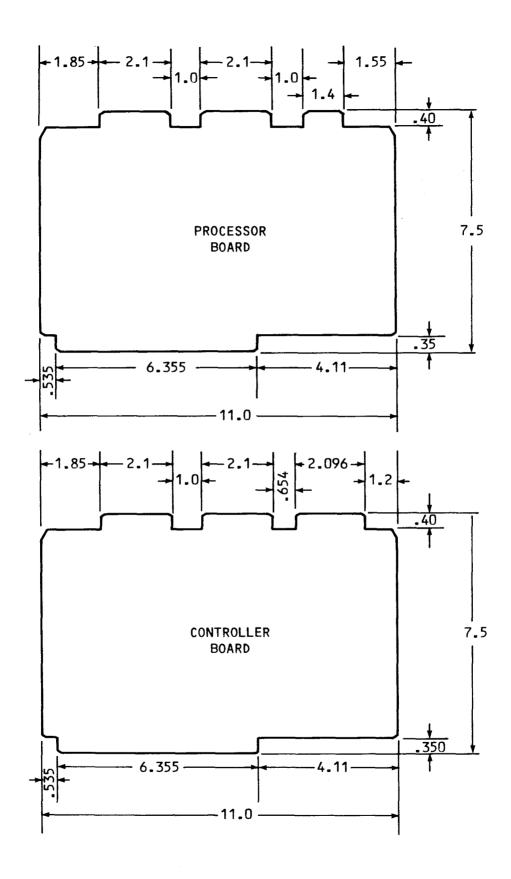

The TM 990/1481 is a high speed general purpose central processing unit implemented on two multilayer printed circuit boards. Utilizing Schottky and low-power Schottky TTL logic, including the 54/74S481 LSI Processor Bit-Slice, it offers a performance improvement of up to 39 X over the TM 990/101MA single board microcomputer. Appendix I contains benchmark data. Because the TM 990/1481 processor generates a bus clock of up to 5 MHz, it will interface only to TM 990 modules designed for 5 MHz or higher operation. A typical system configuration is shown in Figure 1-1. Figures 1-2 and 1-3 show the principal components of the TM 990/1481 processor and controller boards, respectively; Figure 1-4 gives the dimensions for the processor and controller boards; and Figure 1-5 is a block diagram of a TM 990/1481 system.

Some important features of the TM 990/1481 include:

- Software compatible with the 990 family of computers

- Incorporates floating point arithmetic instructions, signed multiply and divide, and single register LST and LWP instructions (floating point numbers are truncated rather than rounded to be compatable with other Texas Instruments computers)

- Meets TM 990 bus specification requirements for 5 MHz bus clock operation

- Provides 15 levels of prioritized and maskable interrupts

- Provides 2 programmable interval timers

- Interfaces to RS-232 terminals such as the TI Microterminal or Silent 700 terminals

- Provides special ARITHMETIC OVERFLOW interrupt

- Use of instruction "look ahead," a variable clock period, and a high degree of parallelism in the architecture produces up to 39 X speed improvement over the TM 990/101MA (See benchmarks in Appendix I).

#### 1.2 MANUAL ORGANIZATION

This manual is organized as follows:

- Section 1 covers TM 990/1481 characteristics and specifications.

- Section 2 shows how to install, powerup, and operate the TM 990/1481.

- Section 3 explains the TM 990/403 TIBUG monitor. TIBUG commands, XOPs, and error indicators are topics that are included.

\* Note, if a TM 990/203 dynamic RAM module is used, software could be loaded from cassette using an ASR terminal such as the TI 733 ASR.

FIGURE 1-1. TYPICAL SYSTEM CONFUGURATION WITH TM 990/1481

- Section 4 covers the TM 990/1481 instruction set. Instruction formats, addressing modes, instruction execution times, user-defined instructions, use of floating point instructions, programming aids, and interrupts are described in this section.

- Section 5 covers the software applications support for the TM 990/1481.

- Section 6 covers I/O programming using the communication register unit (CRU).

- Section 7 covers the theory of operation with circuit descriptions keyed to schematic diagrams.

- Section 8 describes the microinstruction word format used in the TM 990/1481

- Section 9 provides a description of the TM 990/1481's three interfaces including: (1) TM 990 bus interface, (2) processor/controller interface, and (3) terminal interface.

#### 1.3 GENERAL SPECIFICATIONS

System Power Requirements:

|         |                         | Current | : (Amps) |

|---------|-------------------------|---------|----------|

| Voltage | Regulation              | Тур     | Max      |

|         |                         |         |          |

| +5V     | +3%                     | 9.00    | 12.00    |

| +12V    | <u>+</u> 3%             | .02     | .03      |

| -12V    | <del>+</del> 3 <b>%</b> | .02     | .03      |

- Operating Temperature: 0°C to 70°C ambient at the board

- Module Dimensions: The processor and controller dimensions are given in Figure 1-4.

#### 1.4 APPLICABLE DOCUMENTS

The following is a list of documents that provide supplementary information for the TM 990/1481 user.

- SN74S481, SN54LS/74LS481 4-Bit-Slice Schottky Processor Elements Data Manual

- TMS 9901 Programmable Systems Interface Data Manual

- TMS 9902 Asynchronous Communication Controller Data Manual

- Model 990 Computer, TMS 9900 Microprocessor Assembly Language Programmer's Guide (P/N 943441-9701)

- Model 990/12 Computer Assembly Language Programmer's Guide (P/N 2250077-9701 \*A)

- TM 990/201 and TM 990/206 Expansion Memory Boards Data Manual (includes TM 990/201-44)

- TM 990/203 Dynamic RAM Memory Expansion Module.

FIGURE 1-2. TM 990/1481 PRINCIPAL PROCESSOR COMPONENTS

1-5

FIGURE 1-3. TM 990/1481 PRINCIPAL CONTROLLER COMPONENTS

1-6

FIGURE 1-4. TM 990/1481 DIMENSIONS (IN INCHES)

.

FIGURE 1-5. TM 9 1481 SYSTEM DIAGRAM

#### SECTION 2

#### INSTALLATION AND OPERATION

#### 2.1 GENERAL

The procedures for unpacking and setting up the TM 990/1481 for operation are given in this section along with a test routine that can be used to check out the system.

#### 2.2 UNPACKING AND INSPECTION

Remove the TM 990/1481 processor and controller boards and cables from their cartons and discard any protective wrapping.

Inspect both boards for any damage that could have occurred in shipping. Report any damage to your TI supplier.

#### 2.3 PROCESSOR MODULE OPTIONS

The TM 990/1481 processor module provides jumper selection for the following functions:

- External interrupt line (INT6.B-)

- TMS 9901 INT4- interrupt input option

2.3.1 External Interrupt Line (INT6.B-) Select (E1-E2). This option is for factory use. Installing a jumper at E1-E2 connects INT6- at the TMS 9901 to the system bus, signal INT6.B- at P1-20. Removing this jumper opens this line.

2.3.2 TMS 9901 INT4- Interrupt Option (E4-E6). A jumper allows the user to connect the INT4- input to the TMS 9901 from either the interrupt output (TINT-) of the TMS 9902 on the Controller Module or from INT4.B- of the system bus at pin P1-18.

- E5-E4: TMS 9901 INT4- input connects to system bus at P1-18.

- E5-E6: TMS 9901 INT4- input connects to TINT- from TMS 9902.

- Unjumpered: No input to TMS 9901 INT4-

#### NOTE

The TMS 9901 and TMS 9902, both of which contain programmable clocks, are addressable through the CRU. The TMS 9902 is located at software base address  $0080_{16}$  and the TMS 9901 is located at software base address  $0100_{16}$ . A CRU map is shown in Appendix B.

#### 2.4 CONTROLLER MODULE OPTIONS

The TM 990/1481 controller module provides options via:

- Three jumper settings

TTY or RS232C terminal select

Microterminal voltages

Map mode memory timing

- Memory configuration using wiring platform

#### 2.4.1 Controller Module Jumpers

There are three jumper selectable options on the controller module: the terminal select option, the TM 990/301 microterminal supply voltage option, and the map mode memory timing option.

2.4.1.1 Terminal Select Option (E1-E2). The terminal select option allows the user to configure the TM 990/1481 so that either a TTY or RS-232-C/TM 990/301 terminal can be used. This jumper should be connected between E1 and E2 for operation with a TTY terminal; it should be removed for operation with either an RS-232-C terminal or a TM 990/301 microterminal.

2.4.1.2 TM 990/301 Microterminal Supply Voltage Option (E6-E7, E13-E16). Jumpers can be used to provide +12V, +5V, and -5V for the TM 990/301 microterminal. Install jumpers between:

- E6 and E7

- E13 and E14

- E15 and E16

Installing these jumpers will couple the necessary supply voltage to the microterminal. These jumpers should be removed if a terminal other than the microterminal is used.

2.4.1.3 Map Mode Memory Timing Option (E11-E12). The normal position for this jumper is from E12 to E11. Removal of this jumper is currently reserved for future use.

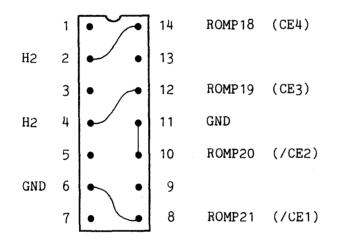

2.4.2 ROM Wiring Platform at U49

The ROM wiring platform is wired for operation with the SN74S478N Schottky Bipolar PROM that is supplied with the TM 990/1481 controller board. Figure 2-1 shows the wiring of this platform as shipped from the factory.

| GND         | 1 | • • | 14 | ROMP18 |

|-------------|---|-----|----|--------|

| H2          | 2 | • • | 13 | CMAX   |

| +12V        | 3 | • • | 12 | ROMP19 |

| H2          | 4 | • • | 11 | GND    |

| CMAP        | 5 | • • | 10 | ROMP20 |

| GND         | 6 | • • | 9  | +5₹    |

| -5 <b>V</b> | 7 | • • | 8  | ROMP21 |

(a) Pin nomenclature for ROM wiring platform at U49

(b) Wiring of U49 for ROM SN74S478N 1K x 8 Schottky bipolar PROM

FIGURE 2-1. ROM ADAPTER PLUG WIRING

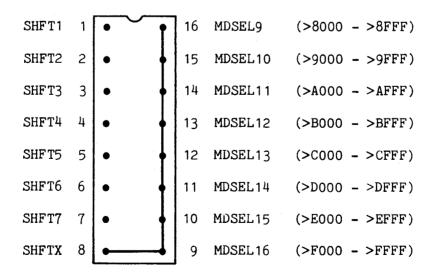

#### 2.4.3 Controller Module Wiring Platforms for Memory Devices

There are two memory plugs located on the controller board which selects the proper waits states required for different memories and memory modules. These plugs are configured (wired) depending on the type of memory device and memory module used. Figure 2-2 identifies the various pin definitions of the plugs as well as how the plugs are wired at the factory. Plug 1 at U94 is used to program the first eight blocks of memory and plug 2 at U99 is used to program the second eight blocks of memory. MDSEL1 (pin 16 of plug 1) identifies the first 1K block of memory and MDSEL16 (pin 9 of plug 2) identifies the block of memory from FOOO<sub>16</sub> through FFFF<sub>16</sub>. SHFTN (N = 1 to 7 or X) selects the number

| SHFT1 | 1              | • • | 16 | MDSEL1 | (>0000 - >0FFF)        |

|-------|----------------|-----|----|--------|------------------------|

| SHFT2 | 2              | •   | 15 | MDSEL2 | (>1000 - >1FFF)        |

| SHFT3 | 3 <sup>:</sup> | •   | 14 | MDSEL3 | (>2000 - >2FFF)        |

| SHFT4 | 4              | •   | 13 | MDSEL4 | (>3000 <b>-</b> >3FFF) |

| SHFT5 | 5              | •   | 12 | MDSEL5 | (>4000 - >4FFF)        |

| SHFT6 | 6              | •   | 11 | MDSEL6 | (>5000 - >5FFF)        |

| SHFT7 | 7              | •   | 10 | MDSEL7 | (>6000 - >6FFF)        |

| SHFTX | 8              | •   | 9  | MDSEL8 | (>7000 - >7FFF)        |

(a) Plug 1 (U94/W5A) Top View

(b) Plug 2 (U99/X5A) Top View

NOTE: Wiring is as shipped from the factory FIGURE 2-2. MEMORY DEVICE WIRING PLATFORMS AT U49 AND U99

2-4

of delays per access required for a particular board and memory device as shown in Table 2-1. A jumper wire is connected from the proper SHFTN pin to the applicable memory pin(s). Memory speed delay logic is further explained in detail in section 7.4.6.

| MEMORY         | MEMORY                                                               | MEMORY                            | PLUG WIRING                               |                                                          |  |

|----------------|----------------------------------------------------------------------|-----------------------------------|-------------------------------------------|----------------------------------------------------------|--|

| BOARD          | DEVICE                                                               | TYPE                              | FROM                                      | TO                                                       |  |

| TM 990/H201-44 | TMS 2716<br>TMS 4045-15<br>TMS 4045-20<br>TMS 4045-30<br>TMS 4045-45 | EPROM<br>RAM<br>RAM<br>RAM<br>RAM | SHFT7<br>SHFT3<br>SHFT4<br>SHFT5<br>SHFT7 | See Note<br>See Note<br>See Note<br>See Note<br>See Note |  |

| TM 990/H203-13 | TMS 4115                                                             | RAM                               | SHFTX                                     | See Note                                                 |  |

#### TABLE 2-1. MEMORY PLUG WIRING

NOTE: As shown in Figure 2-2, connect the SHFTN pin of platforms U94 and U99 to to MDSELN pins on the opposite side of the platform that reflect the memory configuration. Note in the figure that as shipped from the factory, SHFTX is wired to all sixteen 4K byte memory combinations that make up the entire 32 K word addressing.

#### 2.4.4 Controller Module DIP and Toggle Switches

2.4.4.1 RESET Toggle Switch. The RESET switch can be toggled by the user from the front edge of the controller module. When toggled, the RESET switch produces the RESET- signal which forces the TM 990/1481 to perform a context switch to the WP and PC vectors at interrupt trap zero (vectors at 0000<sub>16</sub> and  $0002_{16}$ ). This action also causes IORST- on the system bus (via pin J1-88) to be active a minimum of two REFLCK periods.

2.4.4.2 Fixed Period (Slow Clock) Mode DIP Switch (S3, VAR/FIX). One half of switch S3 is the fixed period mode switch. In the FIX position, the user selects a fixed period of 666.6 nanoseconds for the microinstruction clock cycle that is independent of the clock control field. In the VAR position, the user selects a variable period (200 ns - 666.6 ns) high-speed clock with period controlled by the clock control field of the microinstruction. The normal position of the VAR/FIX DIP switch is the VAR position.

2.4.4.3 SINGLE STEP Mode DIP Switch (S3, CONT/SINGLE STEP). The single step mode switch is the second half of switch S3. In the SINGLE STEP position, the microinstruction clock is turned off allowing single-step through microcode using the SINGLE STEP toggle switch. For normal operation, the CONT/SINGLE STEP switch should be in the CONT position.

2.4.4.4 SINGLE STEP Toggle Switch. The SINGLE STEP toggle switch is accessible at the front edge of the Controller Module; however, it is used for factory test purposes only. When used for test, LEDs (e.g., Dialight 547-2007) are populated in sockets XU11, XU16, and XU19 on the controller module and in sockets XU19, XU25, XU36, XU75, XU81, XU86, and XU92 on the processor module. These lights show test status.

#### NOTE

The SINGLE STEP toggle switch is for factory test purposes only. When toggled, the TM 990/1481 executes one microinstruction step, if in the single step mode.

#### 2.5 REQUIRED EQUIPMENT

The following items are required for a system using the TM 990/1481:

- 1) TM 990/510A, TM 990/520A, or TM 990/530 card cage

- 2) DC power supply capable of meeting the power requirements given in section 1.3

- 3) Suitable terminal (and cable assembly) such as either a TI Silent 700 Terminal or a TM 990/301 Microterminal.

- 4) Memory module such as the TM 990/201-44 or TM 990/203

- 5) Adequate fan forced cooling (NOTE: The TM 990/1481 dissipates 45 watts, typical. Appendix E of the TM 990/530 manual covers criteria to determine cooling requirements.)

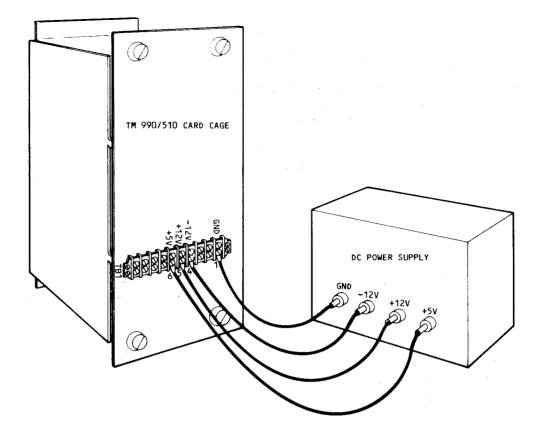

#### 2.6 POWER SUPPLY AND CARD CAGE CONNECTIONS

Figure 2-3 shows the necessary connections between a suitable dc power supply and a TM 990/510A card cage. Either a TM 990/520A or a TM 990/530 card cage could be used in lieu of the TM 990/510A. Power requirements are listed in section 1.3.

#### 2.7 TM 990/1481 PROCESSOR/CONTROLLER PLACEMENT AND INTERCONNECTIONS

Adequate ventilation is a necessity for the TM 990/1481. If possible, the card cage should be placed in the vertical plane. Fan forced cooling will probably be mandatory to maintain the ambient air temperature at less than or equal to 70 degrees centigrade at the hottest point above the boards.

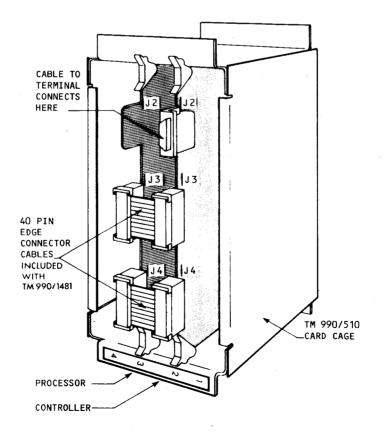

The 40-pin edge connector cables are provided for interconnections between the processor and controller modules. Figure 2-4 shows the proper positions for these connectors (processor J3 to controller J3 and processor J4 to controller J4).

The J2 connector on the controller allows connection to a TTY or any RS-232-C device such as the TI Silent 700 Terminal or the TM 990/301 Microterminal.

FIGURE 2-3. POWER SUPPLY CONNECTIONS

FIGURE 2-4. TM 990/1481 CONTROLLER/PROCESSOR INTERCONNECTIONS

There are several cable assemblies that can be used to provide the necessary interface between various terminals and the TM 990/1481. Table 2-2 provides a listing of these cables.

| TABLE | 2-2. | CABLE | ASSEMBLIES |

|-------|------|-------|------------|

|-------|------|-------|------------|

| MODEL NUMBER | DESCRIPTION                                                                                  |  |  |

|--------------|----------------------------------------------------------------------------------------------|--|--|

| TM 990/502   | Connects TM 990/1481 to an RS-232-C terminal except<br>for those mentioned below             |  |  |

| TM 990/503A  | Connects TM 990/1481 to a TI 743 or 745                                                      |  |  |

| TM 990/504A  | Connects TM 990/1481 to a Model ASR 33 teletype<br>modified for 20 mA current loop operation |  |  |

| TM 990/505   | Connects TM 990/1481 to a TI 733 ASR data terminal                                           |  |  |

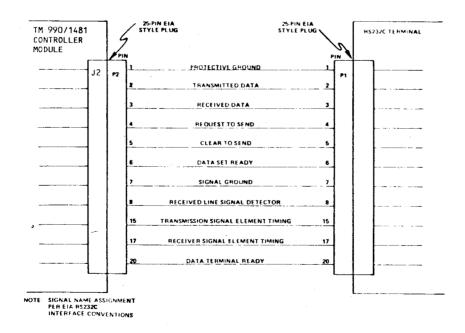

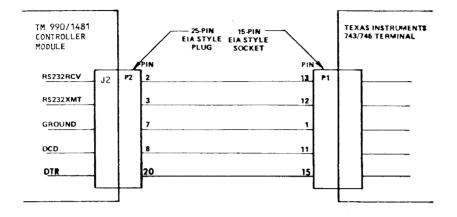

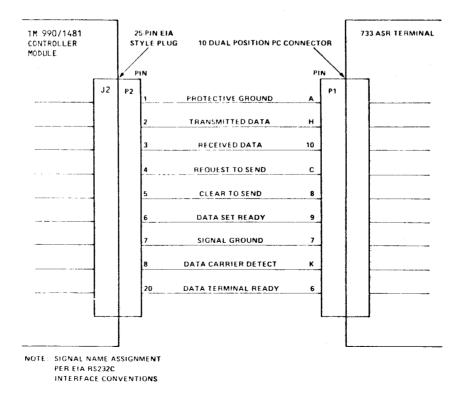

A cable can be fabricated using a 25-pin RS-232-C plug, type DB25P, and a suitable plug for the terminal. Figure 2-5 shows the necessary connections between the TM 990/1481 and a RS-232-C terminal. Figure 2-6 shows the connections between a TM 990/1481 and a TI 743 or 745. Figure 2-7 shows the connections between a TM 990/1481 and a TI 733 ASR data terminal.

FIGURE 2-5. TM 990/1481 AND RS-232-C TERMINAL CONNECTIONS

FIGURE 2-6. TM 990/1481 AND TI 743 OR 745 TERMINAL CONNECTIONS

.

FIGURE 2-7. TM 990/1481 AND TI 733 ASR DATA TERMINAL

#### 2.8.1 Example of TM 990/201 Board Setup

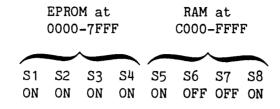

Install the TM 990/403 TIBUG monitor on a TM 990/201-44 memory board in sockets U56 and U64. Set the switches on the TM 990/201 as follows:

Set the jumpers on the TM990/201 board according to the TM990/201 manual.

Install EPROMs containing user firmware on the board. If available, the TM 990/433 Floating Point Demonstration Software could be installed in sockets U57 and U65 on the TM 990/201 board. Switch settings are explained in your memory board user's manual for EPROM and in 403 TIBUG for the new RAM maps.

2.8.2 Board Installation

#### CAUTION

Always disconnect power before inserting or removing a board from the card cage.

Install the TM 990/1481 Processor and Controller cards in the chassis with connectors J3 and J4 cabled to the corresponding connectors on each card (using the supplied cables). Connect a terminal to J2 of the controller. Check that the TM 990/201 card (or other memory board) is correctly populated and installed.

Verify that adaquate cooling is provided, optimally by forced air means.

Apply power to the boards and press the RESET toggle switch on the controller board. Now press the RETURN key on your terminal; the TIBUG banner should be printed, along with a prompt.

The TIBUG monitor is now executing, and all of the monitor commands may be executed. Commands for the TM 990/403 TIBUG are explained in the next section, Section 3.

#### SECTION 3

#### TM 990/403 TIBUG INTERACTIVE DEBUG MONITOR

3.1 GENERAL

The TM 990/403 TIBUG is debug monitor which provides an interactive interface between the user and the TM 990/1481. It is available as an option, supplied on two TMS 2716 EPROMs.

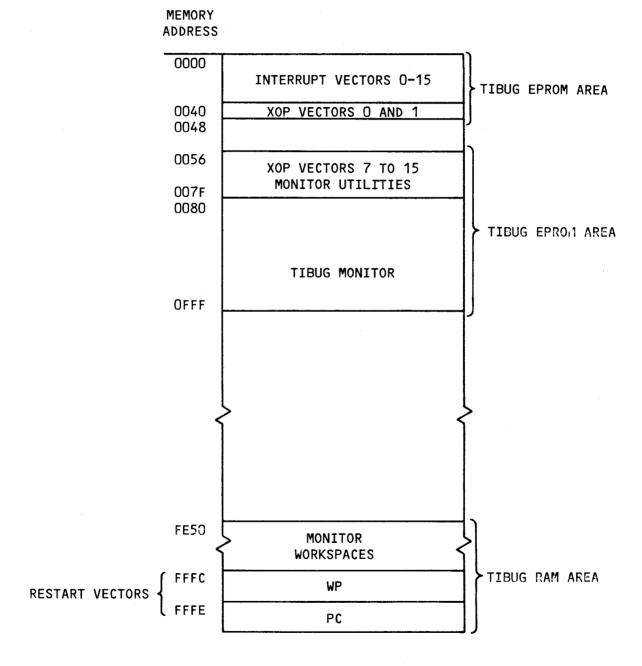

TIBUG occupies EPROM memory space from memory address (M.A.)  $0000_{16}$  to  $0FFF_{16}$  as shown in Figure 3-1. TIBUG uses four workspaces in 40 words of RAM memory. Also in this reserved RAM area are the restart vectors which initialize the monitor following single step execution of instructions.

The TIBUG monitor provides eight software routines that accomplish special tasks. These routines, called in user programs by the XOP machine instruction, perform tasks such as writing characters to a terminal. XOP utility instructions are discussed in detail in paragraph 4.6.9.

All communications with TIBUG is through a 20 mA current loop or RS-232-C device. TIBUG is initialized as follows:

- Press the RESET pushbutton (Figure 1-2). The monitor is called up through interrupt trap 0.

- Press carriage return on the terminal keyboard. TIBUG uses this input to measure the width of the start bit and set the TMS 9902 Asynchronous Communication Controller (ACC) to the correct baud rate.

- TIBUG prints an initialization message on the terminal. On the next line it prints a question mark indicating that the command scanner is available to interpret terminal inputs.

- Enter one of the commands as explained in paragraph 3.2.

3.2 TIBUG COMMANDS

TIBUG commands are listed in Table 3-1.

| INPUT | RESULTS                                      | PARAGRAPH |

|-------|----------------------------------------------|-----------|

| В     | Execute under Breakpoint                     | 3.2.1     |

| С     | CRU Inspect/Change                           | 3.2.2     |

| D     | Dump Memory to Cassett/Paper Tape            | 3.2.3     |

| E     | Execute                                      | 3.2.4     |

| F     | Find Word/Byte in Memory                     | 3.2.5     |

| Н     | Hex Arithmetic                               | 3.2.6     |

| L     | Load Memory from Cassette/Paper Tape         | 3.2.7     |

| М     | Memory Inspect/Change                        | 3.2.8     |

| R     | Inspect/Change User WP, PC, and ST Registers | 3.2.9     |

| S     | Execute in Step Mode                         | 3.2.10    |

| Т     | 1200 Baud Terminal                           | 3.2.11    |

| W     | Inspect/Change Current User Workspaces       | 3.2.12    |

| Х     | Move ALU test to RAM and Execute             | 3.2.13    |

| G     | Start Execution At Location >1000            | 3.2.14    |

#### TABLE 3-1. TIBUG COMMANDS

FIGURE 3-1. MEMORY REQUIREMENTS FOR TIBUG

Conventions used to define command syntax in this paragraph are listed in Table 3-2.

| CONVENTION<br>SYMBOL | EXPLANATION                                                                                                       |  |  |

|----------------------|-------------------------------------------------------------------------------------------------------------------|--|--|

| <>                   | Items to be supplied by the user. The term within the angle brackets is a generic term.                           |  |  |

| []                   | Optional Item – May be included or omitted at the user's discretion. Items not included in brackets are required. |  |  |

| Ęj                   | One of several optional items must be chosen.                                                                     |  |  |

| (CR)                 | Carriage Return                                                                                                   |  |  |

| . 4                  | Space Bar                                                                                                         |  |  |

| LF                   | Line Feed                                                                                                         |  |  |

| R or Rn              | Register (n = 0 to 15)                                                                                            |  |  |

| WP                   | Current User Workspace Pointer contents                                                                           |  |  |

| PC                   | Current User Program Counter contents                                                                             |  |  |

| ST                   | Current User Status Register contents                                                                             |  |  |

TABLE 3-2. COMMAND SYNTAX CONVENTIONS

#### NOTE

Except where otherwise indicated, no space is necessary between the parts of these commands. All numeric input is assumed to be hexadecimal; the last four digits input will be the value used. Thus a mistaken numerical input can be corrected by merely making the last four digits the correct value. If fewer than four digits are input they are right justified.

3.2.1 Execute Under Breakpoint (B)

#### 3.2.1.1 Syntax

B < address > <(CR)>

3.2.1.2 Description. This command is used to execute instructions from one memory address to another (the stopping address is the breakpoint). When execution is complete, WP, PC, and ST register contents are displayed and control is returned back to the monitor command scanner. Program execution begins at the address in the PC (set by using the R command). Execution terminates at the address specified in the B command, and a banner is output showing the contents of the hardware WP, PC, and ST registers in that order.

The address specified must be in RAM and must be the address of the instruction. The breakpoint is controlled by a software interrupt, XOP 15.

If no address is specified, the B command defaults to an E command, where execution continues with no halting point specified.

EXAMPLE:

| 7 B<br>RP | 3E06          |      |      |

|-----------|---------------|------|------|

| E F       | 3 <b>9</b> 00 | 3E06 | 1400 |

| 7         |               |      |      |

3.2.2 CRU Inspect/Change (C)

3.2.2.1 Syntax

# C < CRU Software Base Address $\begin{pmatrix} \\ 1 \\ \end{pmatrix}$ < Count > < (CR) >

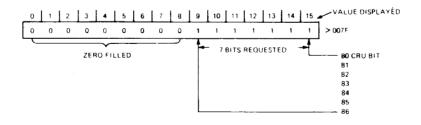

3.2.2.2 Description. The Communication Register Unit (CRU) input bits from "CRU software base address" to ("CRU software base address" + 2("count") -2) are displayed right justified in a 16-bit hexadecimal representation. "CRU software base address" is a 16-bit value in R12 bits 0 to 15; this is the same as the contents of register 12 as used by CRU instructions (Section 5). Up to 16 CRU bits may be displayed. The corresponding CRU output bits may be altered following input bit display by keying in desired hexadecimal data, right justified. A carriage return following data output forces a return to the command scanner. A minus sign (-) or a space causes the same CRU input bits to be displayed again. Defaults for "base address" and "count" are 0 (M.A. 0000) and 0 (count of 16) respectively. "Count" is a hexadecimal value of 0 to F<sub>16</sub> with 0 indicating 16<sub>10</sub>.

The CRU inspect/change monitor command displays from 1 to 16 CRU bits, right justified. The command syntax includes the CRU address and the number of CRU bits to be displayed. The CRU address is the 16-bit contents of R12 as explained in Section 5 (vs. the CRU bit address ("base address") in bits 4 to 14 of R12); thus the user must use 2 X CRU bit address. This is shown in Figure 3-2 where  $100_{16}$  is specified in the command to display values beginning with CRU bit  $80_{16}$ .

? C 100,7 0100=007F

FIGURE 3-2. CRU BITS INSPECTED BY C COMMAND

#### EXAMPLES:

(1) Examine eight CRU input bits. CRU address is 20<sub>16</sub>.

```

?C 20+8

0020=00FF ← CARRIAGE RETURN ENTERED

?

```

(2) Set value of eight CRU output bits at CRU address  $20_{16}$ ; new value is  $02_{16}$ .

```

70 20,8 CHANGE 00FF TO 0002

0020=00FF 2 ← 2 FOLLOWED BY CARRIAGE RETURN

```

(3) Check changes in CRU input bit 0.

(4) Check to see if the TMS 9901 is in the interrupt mode (zero) or clock mode (one).

7℃ 100 0100=FFFE ------ ZERO INDICATES INTERRUPT MODE

(5) Check the contents of the clock register on the TMS 9901 (bits 1 to 14)

?C 102 € 0102⊃000E %

3.2.3 Dump Memory To Cassette/Paper Tape (D)

3.2.3.1 Syntax

-MONITOR PROMPT  $\mathsf{D} < \mathsf{start} \; \mathsf{address} > \{ \begin{array}{c} 1 \\ 1 \\ \end{array} \} < \mathsf{stop} \; \mathsf{address} > \{ \begin{array}{c} 1 \\ 1 \\ \end{array} \} < \mathsf{entry} \; \mathsf{address} > \{ \begin{array}{c} 1 \\ 1 \\ \end{array} \} \\ \mathsf{DT} = < \mathsf{name} > < 1 \\ \end{array} >$

3.2.3.2 Description. Memory is dumped from "start address" to "stop address." "Entry address" is the address in memory where it is desired to begin program execution. After entering a space or comma following the entry address, the monitor responds with an "IDT=" prompt asking for an input of up to eight characters that will identify the program. This program ID will be output when the program is loaded into memory using the TIBUG loader, code will be dumped as non-relocatable data in 990 object record format with absolute load ("start address") and entry addresses specified. Object record format is explained in Appendix G.

After entering the D command, the monitor will respond with "READY Y/N" and wait for a Y keyboard entry indicating that the receiving device is ready. This allows the user to verify switch settings, etc., before proceeding with the dump.

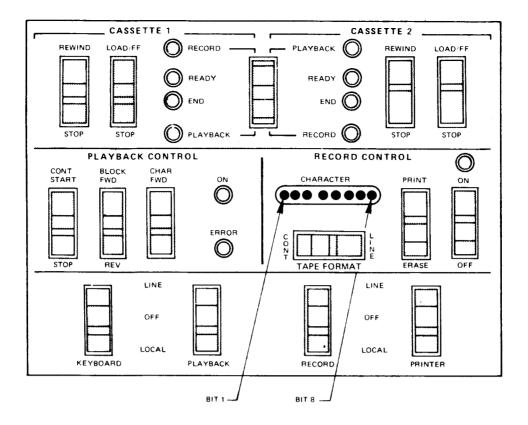

3.2.3.3 Dump To Cassette Example. The terminal is assumed to be a Texas Instruments 733 ASR or equivalent. The terminal must have automatic device control (ADC). This means that the terminal recognizes the four tape control characters DC1, DC2, DC3, and DC4.

The following procedure is carried out prior to answering the "READY Y/N" query (Figure 3-3):

- (1) Load a cassette in the left (No. 1) transport on the 733 ASR.

- (2) Place the transport in the "RECORD" mode.

- (3) Rewind the cassette.

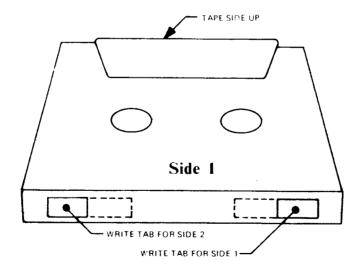

- (4) Load the cassette. If the cassette does not load it may be write protected. The write protect hole is on the bottom right side of the cassette (Figure 3-4). Cover it with the tab provided with the cassette. Now repeat steps 1 through 4.

- (5) The KEYBOARD, PLAYBACK, RECORD, and PRINTER LOCAL/OFF/LINE switches must be in the LINE position.

- (6) Place the TAPE FORMAT switch in the LINE position.

- (7) Answer the "READY Y/N" query with a "Y"; the "Y" will not be echoed.

FIGURE 3-3. 733 ASR MODULE ASSEMBLY (UPPER UNIT) SWITCH PANEL

FIGURE 3-4. TAPE TABS

The terminal is assumed to be an ASR 33 teletypwriter. The following steps should be completed carefully to avoid punching stray characters:

- (1) Enter the command as described in paragraph 3.2.3.1. Do not answer the "READY Y/N" query yet.

- (2) Change the teletype mode from ON LINE to LOCAL.

- (3) Turn on the paper tape punch and press the RUBOUT key several times, placing RUBOUTS at the beginning of the tape for correct-reading/program-loading.

- (4) Turn off the paper tape punch, and reset the teletype mode to LINE.(This is necessary to prevent punching stray characters.)

- (5) Turn on the punch and answer the "READY Y?N" query with "Y". The Y will not be echoed.

- (6) Punching will begin. Each file is followed by 60 rubout characters. When these characters appear (identified by the constant punching of all holes) the punch must be turned off.

- 3.2.4 Execute Command (E)

- 3.2.4.1 Syntax

- Ε

3.2.4.2 Description. The E command causes program execution to begin at current values in the Workspace Pointer and Program Counter.

#### EXAMPLE: E

3.2.5 Find Command (F)

3.2.5.1 Syntax

$F < start address > \{ - \} < stop address > \{ - \} < value > \{ (\overline{CB}) \}$

3.2.5.2 Description. The contents of memory locations from "start address" to "stop address" are compared to "value". The memory addresses whose contents equal "value" are printed out. Default value for start address is 0. The default for "stop address" is 0. The default for "value" is 0.

If the termination character of "value" is a minus sign, the search will be from "start address" to "stop address" for the right byte in "value". If the termination character is a carriage return, the search will be a word mode search.

#### EXAMPLE:

| 7F 0,20 | FFFF | - CARRIAGE RETURN ENTERED |

|---------|------|---------------------------|

| 0006    |      |                           |

| 000C    |      |                           |

| 0012    |      |                           |

| 0016    |      |                           |

| ?F 0 20 | FF   | - MINUS SIGN ENTERED      |

| 0006    |      |                           |

| 0007    |      |                           |

| 000C    |      |                           |

| 000D    |      |                           |

| 0012    |      |                           |

| 0013    |      |                           |

| 0016    |      |                           |

| 0017    |      |                           |

| Ť       |      |                           |

3.2.6 Hexadecimal Arithmetic (H)

3.2.6.1 Syntax

$H < number 1 > \{\hat{A}\} < number 2 > < (CR) >$

3.2.6.2 Description. The Sum and difference of two hexadecimal numbers are output.

EXAMPLE:

?H

200,100

←

CARRIAGE RETURN ENTERED

H1+H2=0300

H1-H2=0100

?

3.2.7 Load Memory From Cassette Or Paper Tape (L)

3.2.7.1 Syntax

L < bias > < (CR) >

3.2.7.2 Description. Data in 990 object record format (defined in Appendix G) is loaded from paper tape or cassette into memory. Bias is the relocation bias (starting address in RAM). Its default is  $0_{16}$ . Both relocatable and absolute data may be loaded into memory with the L command. After the data is loaded, the module identifier (see tage 0 in Appendix G) is printed on the next line.

3.2.7.3 Loading From Texas Instruments 733 ASR Terminal Cassette. The 733 ASR must be equipped with automatic device control (ADC). The following procedure is carried out prior to executing the L command:

- Insert the cassette in one of the two transports on the 733 ASR (cassette 1 in Figure 3-2).

- (2) Place the transport in the playback mode.

- (3) Rewind the cassette.

- (4) Load the cassette.

- (5) Set the KEYBOARD, PLAYBACK, RECORD, and PRINTER LOCAL/LINE switches to LINE.

- (6) Set the TAPE FORMAT switch to LINE.

- (7) Loading will be at 1200 baud.

Execute the L command.

3.2.7.4 Loading From Paper Tape (ASR33 Teletype). Prior to executing the L command, place the paper tape in the reader and position the tape so the reader mechanism is in the null field prior to the file to be loaded. Enter the load command. If the ASR33 has ADC (automatic device control), the reader will begin to read from the tape. If the ASR does not have ADC, turn on the reader and loading will begin.

Each file is terminated with 60 rubouts. When the reader reaches this area of the tape, turn it off. The loader will then pass control to the command scanner.

The user program counter (P) is loaded with the entry address if a 1 tag or 2 tag is found on the tape.

EXAMPLE:

?L

0000 ←

CARRIAGE RETURN ENTERED

PROGRAM ID FROM TAPE

PROGRAM ID FROM TAPE

3.2.8 Memory Inspect/Change, Memory Dump

3.2.8.1 Syntax

Memory Inspect/Change Syntax

M < address > < (CR) >

• Memory Dump Syntax

M < start address > {  $\Lambda$  }< stop address > < (CR) >

3.2.8.2 Description. Memory inspect/change "opens" a memory location, displays it, and gives the option of changing the data in the location. The termination character causes the following:

- If a carriage return, control is returned to the command scanner.

- If a space, the next memory location is opened and displayed.

- If a minus sign, the previous memory location is opened and displayed.

If a hexadecimal value is entered before the termination character, the displayed memory location is updated to the value entered.

Memory dump address directs a display of memory contents from "start address" to "stop address". Each line of output consists of the address of the first data word output followed by eight data words. Memory dump can be terminated at any time by typing any character on the keyboard.

#### EXAMPLES:

(1)

?M

3E00

CARRIAGE RETURN ENTERED

3E00=FF0F

SE02=0012

FFFF

3E04=0311

MINUS SIGN ENTERED

3E02=FFFF

NEW CONTENTS

3E04=0311

SE04=0311

3E06=0032

EEAA

7

NEW CONTENTS AND

(2)

?M 20 30 0020≖0020 0030 0000 0005 0030 0D00 0000 0024-0030≖0001 7

3.2.9 Inspect/Change User WP, PC, and ST Registers (R)

3.2.9.1 Syntax

R < (CR) >

3.2.9.2 Description. The user workspace pointer (WP), program counter (PC), and status register (ST) are inspected and changed with the R command. The output letters W, P, and S identify the values of the three principal hardware registers passed to the processor when a B, E, or S command is entered. WP points to the workspace register area, PC points to the next instruction to be executed (Program Counter), and ST is the Status Register contents.

The termination character causes the following:

- A carriage return causes control to return to the command scanner.

- A space causes the next register to be opened.

Order of display is W, P, S.

## EXAMPLES:

| (1)     |                                 |

|---------|---------------------------------|

| ?R      |                                 |

| W=0020  | 100 - SPACE ENTERED             |

| P=0000  | 200 🖛 — CARRIAGE RETURN ENTERED |

| 7       |                                 |

| (2)     |                                 |

| ?R      |                                 |

| W=0100★ |                                 |

| P=0200◄ | /                               |

| S=0000+ |                                 |

| ?       |                                 |

3.2.10 Execute In Single Step Mode (S)

3.2.10.1 Syntax

S

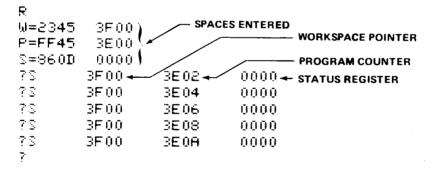

3.2.10.2 Description. Each time the S command is entered, a single instruction is executed at the address in the Program Counter, then the contents of the Program Counter, Workspace Pointer, and Status Register (after execution) are printed out. Successive instructions can be executed by repeated S commands. Essentially, this command executes one instruction then returns control to the monitor.

## EXAMPLE:

#### NOTE

Incorrect results are obtained when the S instruction causes execution of an XOP instruction (see paragraph 4.6.9) in a user program. To avoid these problems the B command should be used to execute any XOP's in a program (rather than the S command). 3.2.11 TI 733 ASR Baud Rate (T)

#### 3.2.11.1 Syntax

Т

3.2.11.2 Description. The T command is used to alert TIBUG that the terminal being used is a 1200 baud terminal which is not a Texas Instruments' 733 ASR (e.g., a 1200 baud CRT). To revoke the T command, enter it again.

3.2.11.3 Use. T is used only when operating with a true 1200 baud peripheral device. Note that T is never used when operating at other baud rates.

In TIBUG the baud rate is set by measuring the width of the character "A" input from a terminal. When an "A" of 1200 baud width is measured, TIBUG is set up to automatically insert three nulls for every character output to the terminal. These nulls are inserted to allow correct operation of the TM 990/1481 with Texas Instruments 733ASR data terminals.

3.2.12 Inspect/Change User Workspace (W)

3.2.12.1 Syntax

W [register number] < (CR) >

3.2.12.2 Description. The W command is used to display the contents of all workspace registers or display one register at a time while allowing the user to change the register contents. The workspace begins at the address given by the Workspace Pointer.

The W command, followed by a carriage return, causes the contents of the entire workspace to be printed. Control is then passed to the command scanner.

The W command followed by a register number in hexadecimal and a carriage return causes the display of the specified register's contents. The user may then enter a new value into the register by entering a hexadecimal value. The following are termination characters whether or not a new value is entered:

- A space causes display of the next register.

- A minus sign causes display of the previous register.

- A carriage return gives control to the command scanner.

EXAMPLES:

| ?⊎◄     |         | CARRIAGE RETU | JRN ENTERED |         |         |         |         |

|---------|---------|---------------|-------------|---------|---------|---------|---------|

| R0=F942 | R1=0084 | R2=FA2A       | R3=0020     | R4=FB5E | R5=0098 | R6=1300 | R7=0084 |