As you are now the owner of this document which should have come to you for free, please consider making a donation of £1 or more for the upkeep of the (Radar) website which holds this document. I give my time for free, but it costs me money to bring this document to you. You can donate here <u>https://blunham.com/Misc/Texas</u>

Many thanks.

Please do not upload this copyright pdf document to any other website. Breach of copyright may result in a criminal conviction.

This Acrobat document was generated by me, Colin Hinson, from a document held by me. I requested permission to publish this from Texas Instruments (twice) but received no reply. It is presented here (for free) and this pdf version of the document is my copyright in much the same way as a photograph would be. If you believe the document to be under other copyright, please contact me.

The document should have been downloaded from my website <u>https://blunham.com/</u>, or any mirror site named on that site. If you downloaded it from elsewhere, please let me know (particularly if you were charged for it). You can contact me via my Genuki email page: <u>https://www.genuki.org.uk/big/eng/YKS/various?recipient=colin</u>

You may not copy the file for onward transmission of the data nor attempt to make monetary gain by the use of these files. If you want someone else to have a copy of the file, point them at the website. (<u>https://blunham.com/Misc/Texas</u>). Please do not point them at the file itself as it may move or the site may be updated.

It should be noted that most of the pages are identifiable as having been processed by me.

If you find missing pages, pages in the wrong order, anything else wrong with the file or simply want to make a comment, please drop me a line (see above).

It is my hope that you find the file of use to you.

Colin Hinson In the village of Blunham, Bedfordshire.

I put a lot of time into producing these files which is why you are met with this page when you open the file.

TEXAS INSTRUMENTS

# TM 990/204 Memory Module With Battery Backup

# MICROPROCESSOR SERIES<sup>™</sup>

**User's Guide**

# SECTION

| 1. | INTRODUCTION |                                                        |               |  |  |  |  |

|----|--------------|--------------------------------------------------------|---------------|--|--|--|--|

|    | 1.1          | General                                                | 1-1           |  |  |  |  |

|    | 1.2          | Manual Organization                                    | 1-2           |  |  |  |  |

|    | 1.3          | Specifications                                         | 1-2           |  |  |  |  |

|    | 1.4          | Applicable Documents                                   | 1-3           |  |  |  |  |

|    |              |                                                        |               |  |  |  |  |

| 2. | •            | LLATION AND OPERATION                                  |               |  |  |  |  |

|    | 2.1          | General                                                | 2-1           |  |  |  |  |

|    | 2.2          | Required Equipment                                     | 2-1           |  |  |  |  |

|    | 2.3          | Unpacking                                              | 2-1           |  |  |  |  |

|    | 2.4          | Jumper Settings                                        | 2-1           |  |  |  |  |

|    |              | 2.4.1 Connect/Disconnect Battery from Memory Blocks    |               |  |  |  |  |

|    |              | (Jumpers J1 to J4)                                     | 2-3           |  |  |  |  |

|    |              | 2.4.2 Decode/No-Decode of Extended Address Lines       |               |  |  |  |  |

|    |              | Jumpers J5 and J6)                                     | 2-4           |  |  |  |  |

|    |              | 2.4.3 Allow or Prevent Software to Delete/Map Board    |               |  |  |  |  |

|    |              | in System (Jumper 7)                                   | 2-4           |  |  |  |  |

|    |              | 2.4.4 Select Logic Level to Enable/Disable Write       |               |  |  |  |  |

|    |              | Protect (Jumper 8)                                     | 2 <b>-</b> 5  |  |  |  |  |

|    |              | 2.4.5 Connect Battery into Battery-Backup Circuit      |               |  |  |  |  |

|    |              | (Jumper J9)                                            | 2-5           |  |  |  |  |

|    | 2.5          | Switch Settings                                        | 2-6           |  |  |  |  |

|    |              | 2.5.1 Select Memory Bounds (Platforms S1 and S2)       | 2-7           |  |  |  |  |

|    |              | 2.5.2 Select Start of CRU Address Space (Jumper        |               |  |  |  |  |

|    |              | Platform S3)                                           | 2-10          |  |  |  |  |

|    |              | 2.5.3 Wait State Selection for Different Memories      |               |  |  |  |  |

|    |              | (Switch S4)                                            | 2-13          |  |  |  |  |

|    |              | 2.5.4 Write Protect Entire Board (Switch S5)           | 2-14          |  |  |  |  |

|    |              | 2.5.5 Select Level of Interrupt to CPU (Platform S6)   | 2-14          |  |  |  |  |

|    | 2.6          | LED Indicators                                         | 2-15          |  |  |  |  |

|    | 2.7          | Installing a Minimum System                            | 2 <b>-</b> 15 |  |  |  |  |

|    | 2.8          | Considerations                                         | 2-16          |  |  |  |  |

|    | 2.9          | Example Program                                        | 2 <b>-</b> 16 |  |  |  |  |

|    | 2.10         | Demonstrating Write Protect Using TIBUG Commands       | 2-17          |  |  |  |  |

|    | 2.11         | Battery Backup                                         | 2-19          |  |  |  |  |

|    | _            |                                                        |               |  |  |  |  |

| 3. |              | AMMING THE TM 990/204                                  |               |  |  |  |  |

|    |              | General                                                | 3-1           |  |  |  |  |

|    | 3.2          | Select CRU Base Address                                | 3-1           |  |  |  |  |

|    | 3.3          | CRU Bits                                               | 3-1           |  |  |  |  |

|    | 3.4          | Write- and Execute- Protect Memory                     | 3-4           |  |  |  |  |

|    |              | 3.4.1 Software Write Protect of Memory (CRU Bits 0-3). | 3-4           |  |  |  |  |

|    |              | 3.4.2 Execute Protect Memory (CRU Bits 4 to 7)         | 3-5           |  |  |  |  |

|    | 3.5          | Interrupt Handling                                     | 3-6           |  |  |  |  |

|    |              | 3.5.1 Test for Write-Protect Violation (Read           | _             |  |  |  |  |

|    |              | CRU Bit 8)                                             | 3-6           |  |  |  |  |

|    |              | 3.5.2 Test for Execute-Protect Violation (Read         | <u> </u>      |  |  |  |  |

|    |              | CRU Bit 9)                                             | 3-7           |  |  |  |  |

|    |              | 3.5.3 Reset and Trigger Indicators                     | 3-7           |  |  |  |  |

# TABLE OF CONTENTS (CONTINUED)

# TITLE

|    | 3.6   | Delete All Board Memory From System (Write to<br>CRU Bit 9) | 3-8  |

|----|-------|-------------------------------------------------------------|------|

|    | 3.7   | Test Position of Write Protect Switch S5                    | -    |

|    |       | (Read CRU Bit 10)                                           | 3-8  |

|    | 3.8   | User LED DS3 (Write to CRU Bit 10)                          | 3-8  |

|    | 3.9   | Board-Addressed Indication Bit (Read/Write CRU Bit 11)      | 3–8  |

|    | 3.10  | Four Flag Bits                                              | 3-9  |

|    | 3.11  | Power-Fail Interrupt                                        | 3-10 |

| 4. | THEOR | Y OF OPERATION                                              |      |

|    | 4.1   | General                                                     | 4-1  |

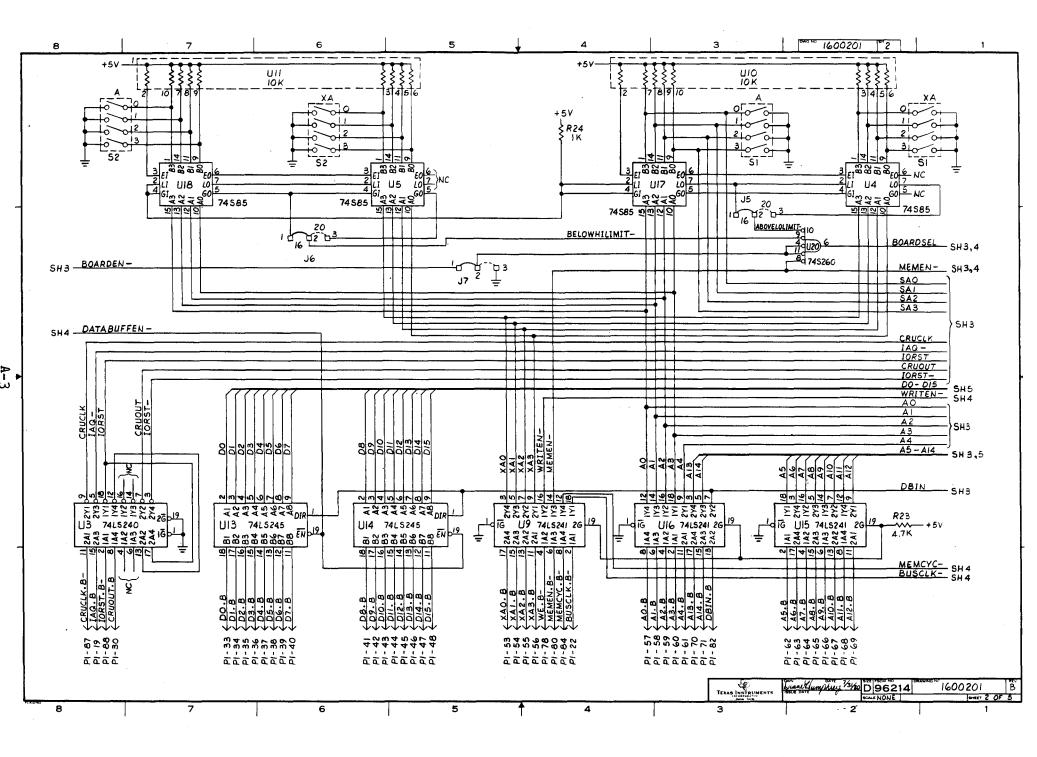

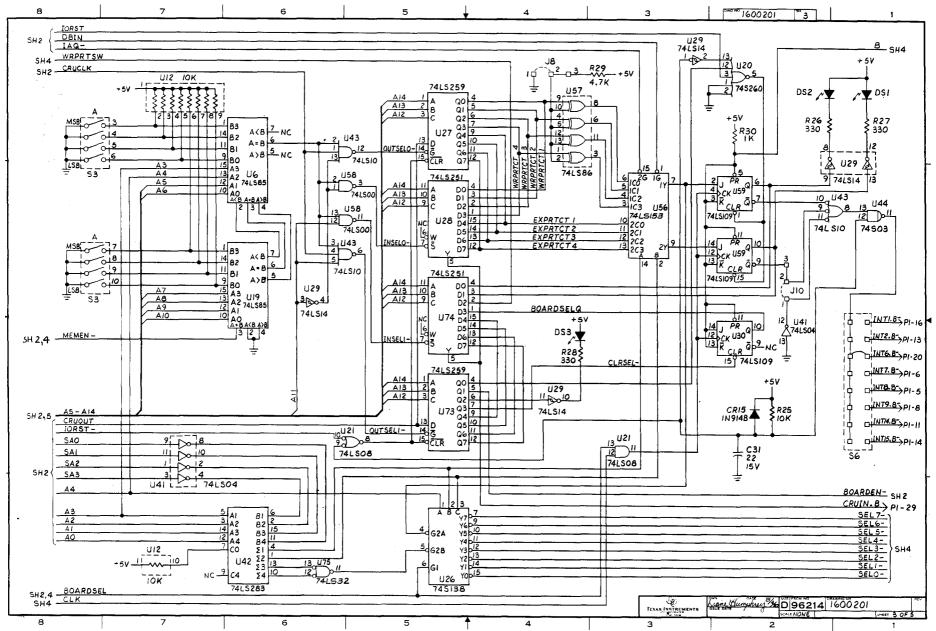

|    | 4.2   | Connector P1 and Buffering                                  | 4-2  |

|    | 4.3   | Board Memory Address Decoding                               | 4-2  |

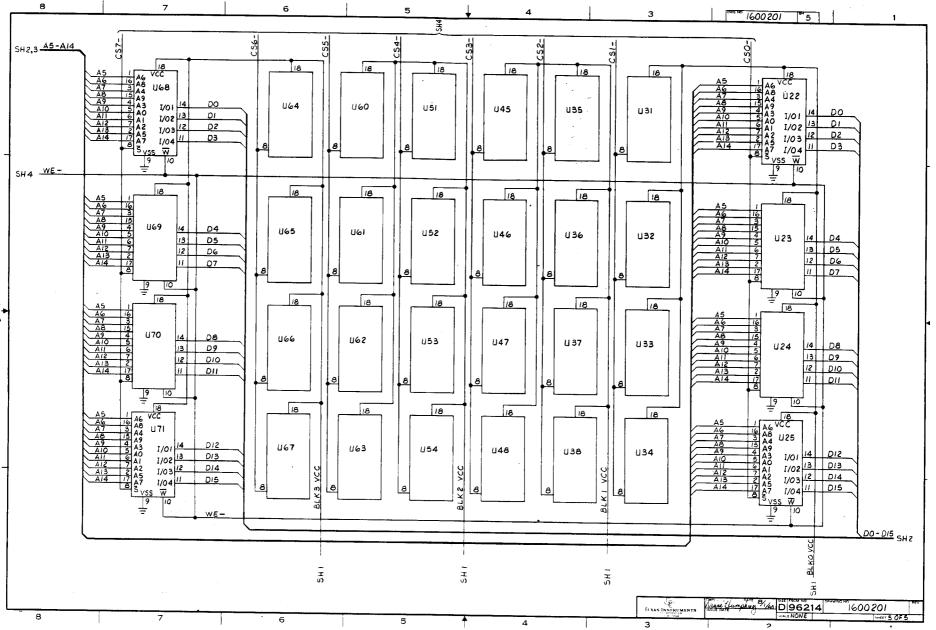

|    | 4.4   | Memory Organization and Enabling                            |      |

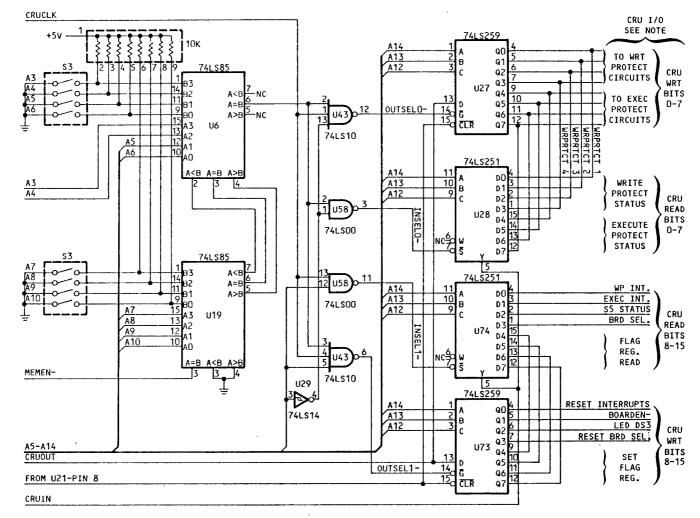

|    | 4.5   | CRU Programmable Devices                                    |      |

|    |       | 4.5.1 CRU Read Operations                                   | 4-6  |

|    |       | 4.5.2 CRU Write Operations                                  | 4-6  |

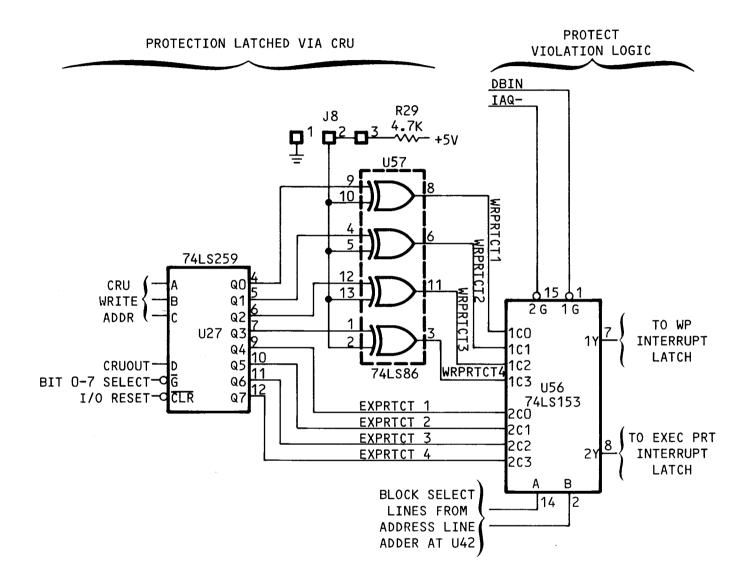

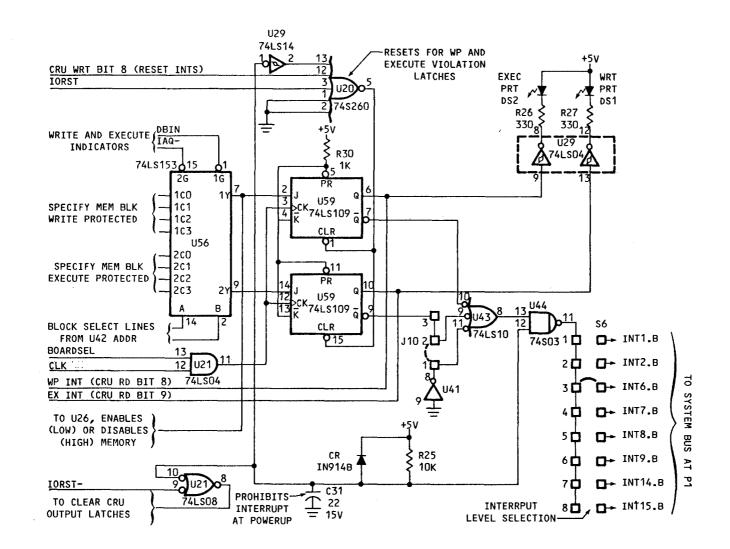

|    | 4.6   | Interrupts                                                  | 4-11 |

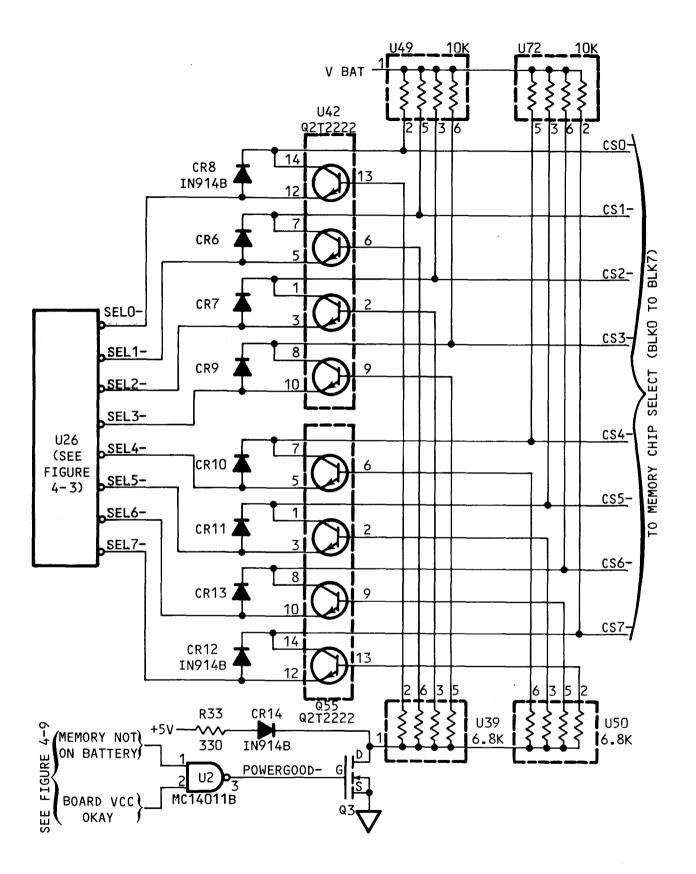

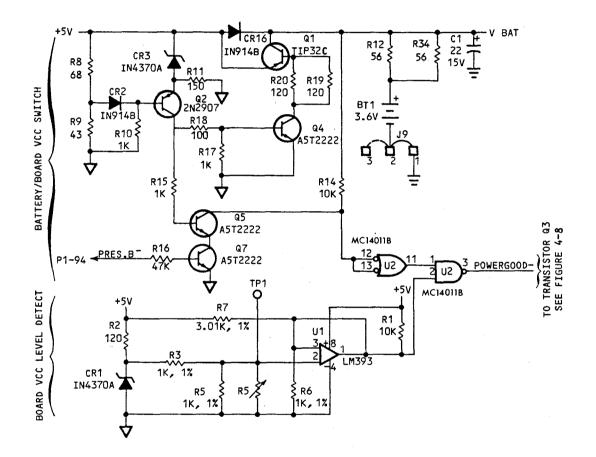

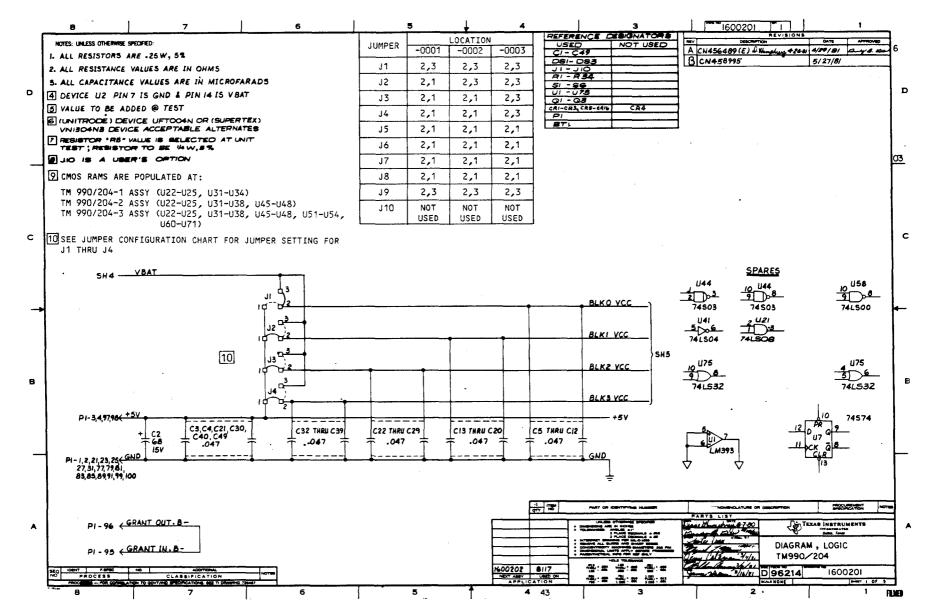

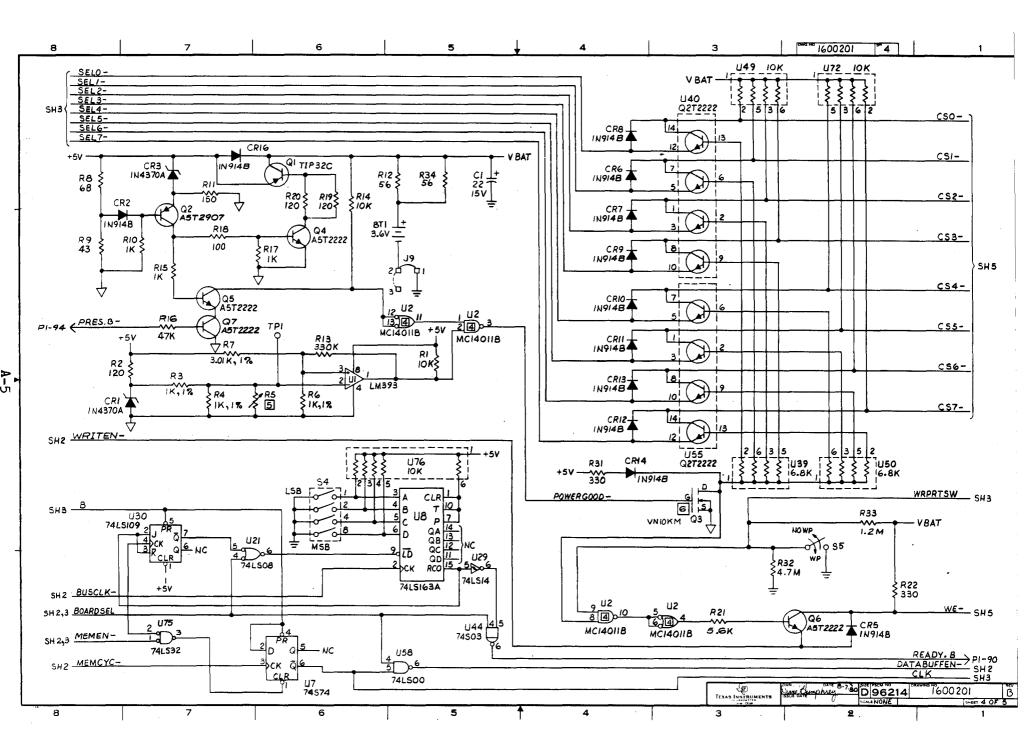

|    | 4.7   | Battery Backup                                              | 4-12 |

|    |       | 4.7.1 Memory Chip Select Circuitry                          | 4-12 |

|    |       | 4.7.2 Power Fail Circuitry                                  |      |

|    |       | 4.7.3 Battery/Board Vcc Voltage Select                      |      |

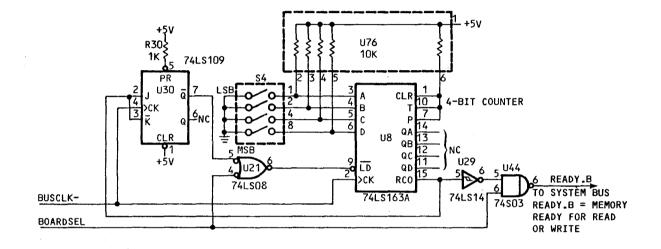

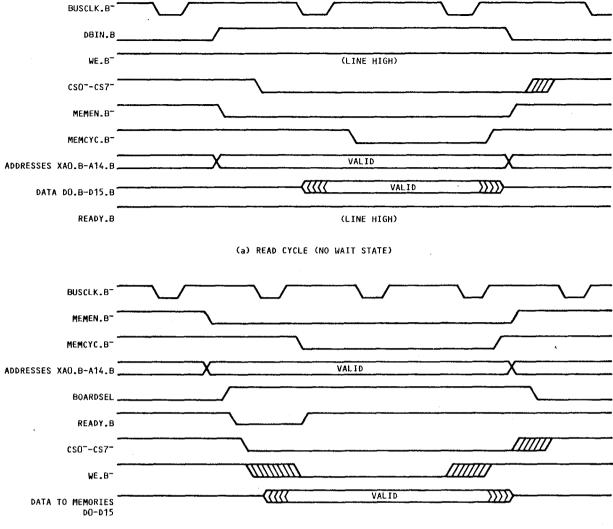

|    | 4.8   | Memory Timing Circuitry                                     |      |

|    |       |                                                             |      |

# APPENDICES

Appendix A Schematics

Appendix B Parts List

Appendix C Bus Signals to TM 990/204 Module at Connector P1

Index

# LIST OF ILLUSTRATIONS

# FIGURE

# TITLE

| n  | ٨ | ~ | 17 |

|----|---|---|----|

| Γ. | А | G | Ľ  |

| 1-1<br>1-2<br>1-3                                                   | TM 990/204 Block Diagram<br>TM 990/204 Module Principal Components<br>TM 990/204 Module Dimensions                                                                                                                                                                                                                                                                 | 1-4                                |

|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5                                     | Memory Block Organization<br>Switch S1 & S2 Address Selection (for examples)<br>CRU Address Nomenclature<br>CRU Switch Settings at S3 (for example)<br>LEDs and Write Protect Switch at Front of Board                                                                                                                                                             | 2-3<br>2-9<br>2-10<br>2-12<br>2-14 |

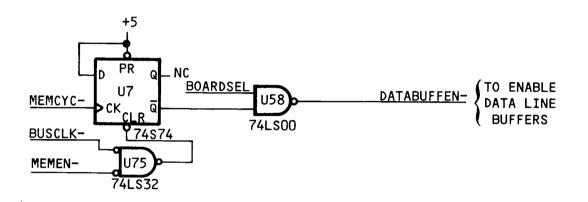

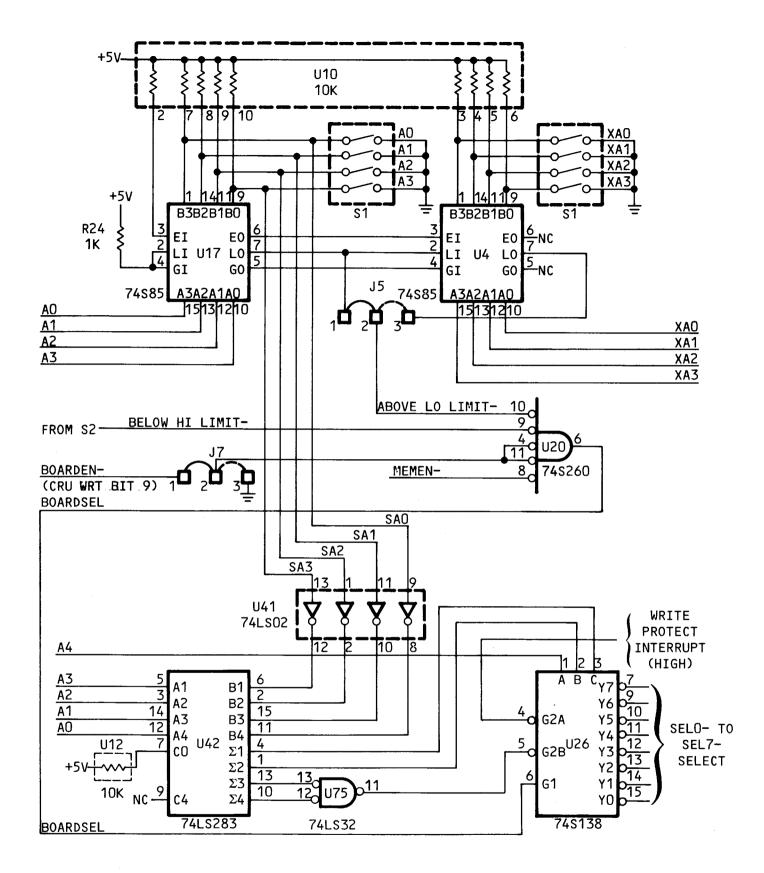

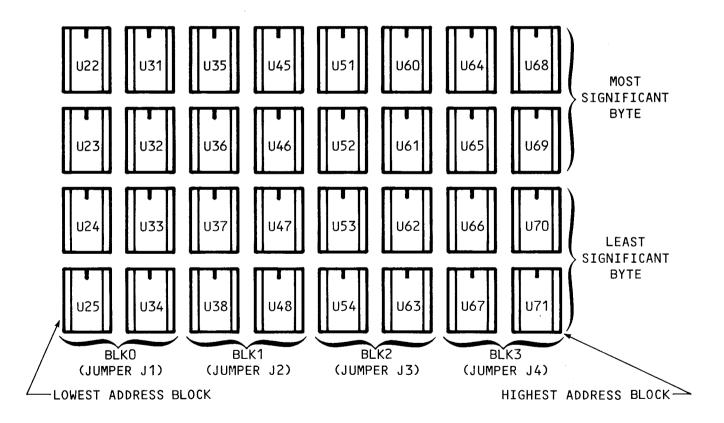

| 4-1<br>4-2<br>4-3<br>4-4<br>4-5<br>4-6<br>4-7<br>4-8<br>4-9<br>4-10 | TM 990/204 Memory Board Block Diagram.<br>Data Buffer Enable Circuitry.<br>Memory Address Selection Schematic.<br>Memory Placement by Block.<br>CRU Select Circuitry.<br>Write-Protect and Execute-Protect Enabling.<br>Interrupt Logic.<br>Memory Chip Enable/Disable Circuitry.<br>Switching Circuitry for Memory Vcc Source.<br>Wait State Insertion Circuitry. | 4-14                               |

| 4-11                                                                | TM 990/204 Memory Timing                                                                                                                                                                                                                                                                                                                                           | 4-17                               |

# LIST OF TABLES

# TABLE

# TITLE

# PAGE

| 2-1          | Jumper Settings                         | 2-2           |

|--------------|-----------------------------------------|---------------|

|              | Lower and Upper Address Bound Selection |               |

|              | CRU Base Address Selection              |               |

| 2-4          | Wait State Selection at Platform S4     | 2-13          |

| 2 <b>-</b> 5 | Wait States for Examle Memories         | 2 <b>-</b> 13 |

| 3-1          | TM 990/204 CRU Map                      | 3-2           |

#### SECTION 1

## INTRODUCTION

### 1.1 GENERAL

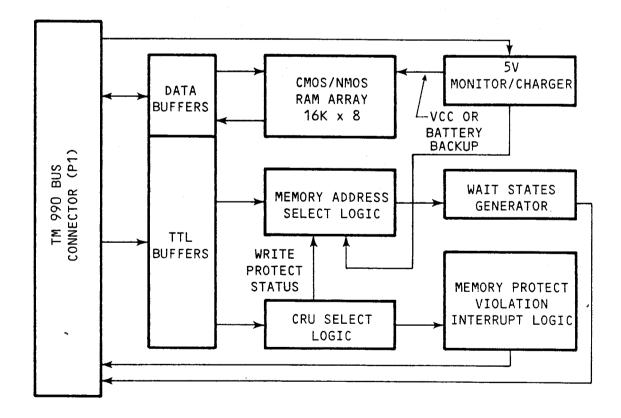

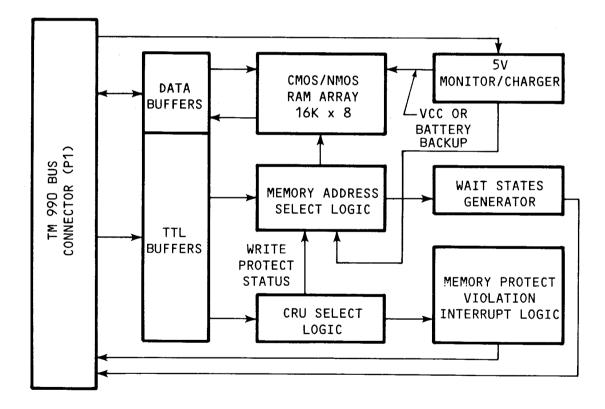

The TM 990/204 is a RAM memory expansion board compatible with the TM 990 bus and CPU modules such as the TM 990/100MA, TM 990/101MA, and the TM 990/1481. Figure 1-1 is a block diagram of the board. Its features include:

- Shipped with CMOS RAM. Memory is expandable in 4-K byte blocks to a maximum of 16 K bytes in four blocks. Dash-number configurations are shown in Table 1-1.

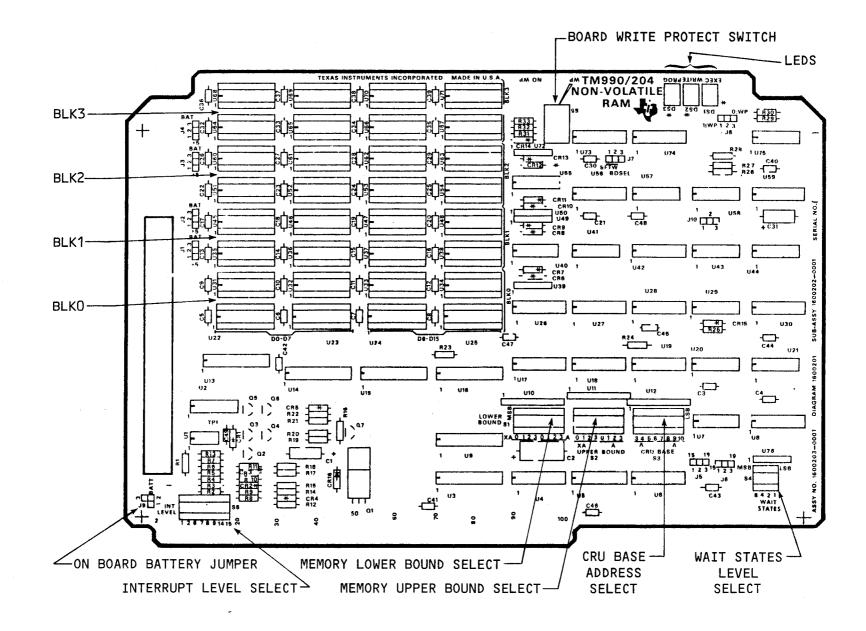

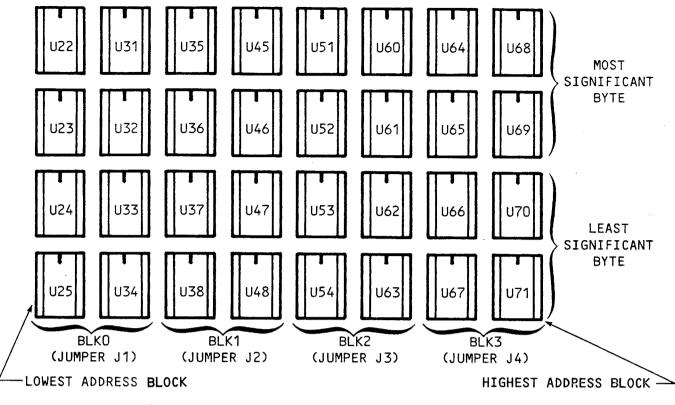

- CMOS or NMOS RAM compatible; can be mixed in individual 4 K by 8-bit blocks (blocks are shown in Figure 1-2).

- Memory organized into four 4-K-byte blocks; some features organized by blocks, a maximum of four blocks per board

- Built-in battery backup feature prevents loss of CMOS memory data in case of a power loss, as shown below for a new battery:

|    | Model     | Room Tempe | erature, Typ | Worst Cas | e, 0-70°C |

|----|-----------|------------|--------------|-----------|-----------|

| TM | 990/204-1 | 37         | days         | 480       | hours     |

| ТM | 990/204-2 | 34         | days         | 240       | hours     |

| ТΜ | 990/204-3 | 30         | days         | 120       | hours     |

NOTE

Because of the heavy current requirements for NMOS memory, this board's battery-backup feature is intended for CMOS only.

- CRU-controllable functions include:

- Write protect selected memory blocks (if protected, memory will be deselected, and an interrupt, at board interrupt level, can be specified by user)

- Execute protect selected memory blocks (memory is not deselected; but interrupt, at board interrupt level, can be specified by user)

- Set and read four flag bits

- Control functions such as delete board memory from system, writeprotect violation indicators, execute-protect violation indicators, board-was-addressed bit

|              | Shipped*    |      | Amperage | at 5V (+3%) | )    |

|--------------|-------------|------|----------|-------------|------|

|              | Memory Size | Cl   | 10S      | N           | IOS  |

| Model        | (Bytes)     | Тур  | Max      | Тур         | Max  |

| TM 990/204-1 | 4K CMOS     | 1.10 | 1.98     | 1.42        | 2.46 |

| TM 990/204-2 | 8K CMOS     | 1.16 | 2.30     | 1.78        | 3.26 |

| TM 990/204-3 | 16K CMOS    | 1.27 | 2.94     | 2.5         | 4.86 |

TABLE 1-1. PRODUCT INDEX AND POWER REQUIREMENTS

\*Shipped with CMOS only; NMOS power shown for information only.

- Designed to fit in TM 990 card cages (TM 990/510 or equivalent)

- DMA capability

- Board LEDs designate:

- Attempt to execute instruction from an execute-protected block of memory

- Attempt to write to write-protected block of memory

- User-designated purpose, software programmable

- All memory can be write protected by a switch accessable to the user while the board is installed.

- Memory can be memory mapped into system using jumper-selectable addresses; includes optional extended addressing (address 1 M bytes)

- Selectable memory wait states

- Selectable interrupt levels (interrupts, if enabled, are caused by attempts to violate write-protected or execute-protected memory)

# 1.2 MANUAL ORGANIZATION

- Section 1 gives general information on the TM 990/204 board including specifications, board outline, etc.

- Section 2 describes how to unpack the board, how the jumpers are used to configure the board to the user's system, and how to plug the board into the system and do an initial board checkout.

- Section 3 covers programming aspects of the board.

- Section 4 covers board theory of operation.

- Appendices contain auxiliary information such as schematics, parts list, etc.

# 1.3 SPECIFICATIONS

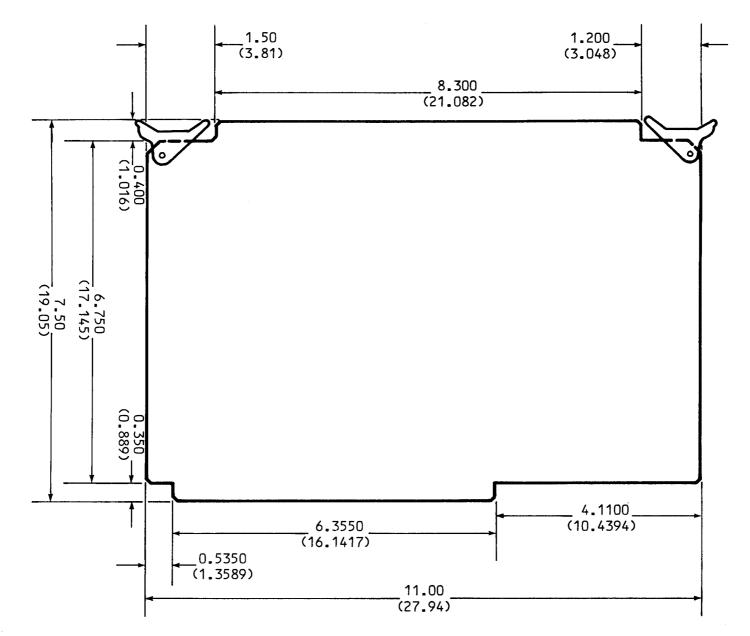

- Module dimensions: See Figure 1-3

- Operating temperature: 0 to 70 °C (32 to 158 °F)

- Memory device compatibility includes:

- CMOS: 6514 or equivalent

- NMOS: 2114 or equivalent

- Chip organization: 1024 x 4

- Frequency: 5 MHz maximum, memory wait states jumper selectable

- Typical power requirements at +5 V (+3%): see Table 1-1.

| • | Battery     | Gould MS2501       | Gould MS2503                   | GE 41B019AD00201                                     | Unit    |

|---|-------------|--------------------|--------------------------------|------------------------------------------------------|---------|

|   | Voltage     | 1.2 (3 needed)     | 3.6                            | 3.6                                                  | v       |

|   | Capacity    | 250                | 250                            | 250                                                  | mA-H    |

|   | Temp (Max)  | 70                 | 70                             | 70                                                   | °C      |

|   | Dimensions  | •                  | •                              | · · · · ·                                            | •       |

|   | Diameter    | 0.563              | 0.563                          | 0.62                                                 | inch    |

|   | Heighth     | 1.200              | 3.55                           | 3.87                                                 | inches  |

|   | Manufacturo | Portable<br>931 N. | e Battery Div.<br>Vandalia St. | General Electric<br>Battery Departme<br>P.O. Box 861 | nt      |

|   |             | St. Paul           | l, Minn. 55114                 | Gainesville, Fla                                     | • 32602 |

# 1.4 APPLICABLE DOCUMENTS

- TM 990/100MA Microcomputer User's Guide

- TM 990/101MA Microcomputer User's Guide

- TM 990/1481 High Performance CPU Module User's Guide

- TM 990 System Specification

# FIGURE 1-1. TM 990/204 BLOCK DIAGRAM

FIGURE 1-2. TM 990/204 MODULE PRINCIPAL COMPONENTS

1-4

FIGURE 1-3. TM 990/204 MODULE DIMENSIONS

5

#### SECTION 2

## INSTALLATION AND OPERATION

2.1 GENERAL

This section provides the procedure for unpacking and setting up the TM 990/204 module for operation with one of the TM 990 series of microcomputers compatible with the memory board's 16-bit data bus. A sample program is provided to demonstrate communication to a user-defined LED via the CRU (Communication Register Unit).

## 2.2 REQUIRED EQUIPMENT

The following equipment comprise the minimum system configuration required for the TM 990/204:

- Card cage such as TM 990/510 or equivalent

- Power supply such as the TM 990/518; selected supply must be large enough to provide required system voltages and current

- Compatible microcomputer board

- A suitable terminal is recommended to provide user communication to the system and also to perform the initial checkout routines in this section.

#### 2.3 UNPACKING

Remove the TM 990/204 module from its carton. Check the module for any abnormalities that could have occurred in shipping. Report any discrepancies to your distributor immediately. Note that the battery is shipped disconnected from the board and must be connected via jumper J9 (paragraph 2.4.5). Sections 2.4 and 2.5 cover jumper and switch settings; section 2.6 describes steps for a typical installation.

## 2.4 JUMPER SETTINGS

This section defines the jumper configurations on the TM 990/204. As-shipped settings are shown in Table 2-1.

It is presumed that the user has a configured system including card cage, power supply, CPU board, and terminal. See the respective user's guides for installing these pieces of equipment.

CAUTION

Do not remove or install the TM 990/204 while power is applied to the card cage. Remove power to the card cage before installing or removing a module. Apply power only after installation or removal. Table 2-1 is a summary of the board's jumpers which are further described in the following paragraphs. Note that the battery is shipped disconnected from the board and must be connected via jumper J9 (paragraph 2.4.5).

| JUMPER & POSITION |                              |       | PARA. MEANING                                                                                                                                                                                                  |     | AS SHIPPED<br>(For each version) |              |  |

|-------------------|------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------|--------------|--|

|                   |                              |       |                                                                                                                                                                                                                | -1  | -2                               | <b>-</b> 3   |  |

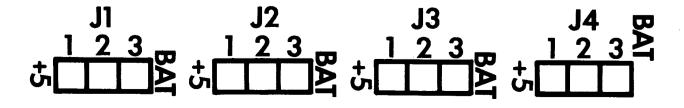

| <b>*</b> J1       | 2-1<br>2-3                   | 2.4.1 | BLKO not connected to battery backup<br>BLKO connected to battery backup                                                                                                                                       | 2-3 | 2-3                              | 2-3          |  |

| *J2               | 2 <b>-</b> 1<br>2 <b>-</b> 3 | 2.4.1 | BLK1 not connected to battery backup<br>BLK1 connected to battery backup                                                                                                                                       | 2-1 | 2-3                              | 2-3          |  |

| <b>*</b> J3       | 2-1<br>2-3                   | 2.4.1 | BLK2 not connected to battery backup<br>BLK2 connected to battery backup                                                                                                                                       | 2-1 | 2-1                              | 2-3          |  |

| <b>*</b> J4       | 2–1<br>2–3                   | 2.4.1 | BLK3 not connected to battery backup<br>BLK3 connected to battery backup                                                                                                                                       | 2-1 | 2-1                              | 2 <b>-</b> 3 |  |

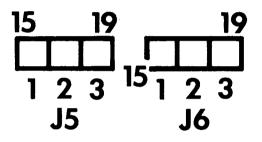

| J5                | 2-1<br>2-3                   |       | Address lines AO-A3 decoded for lower memory bound<br>**Address lines XAO-A3 decoded for lower memory bound                                                                                                    | 2-1 | 2-1                              | 2-1          |  |

| J6                | 2 <b>-</b> 1<br>2-3          |       | Address lines AO-A3 decoded for upper memory bound<br>**Address lines XAO-A3 decoded for upper memory bound                                                                                                    | 2-1 | 2-1                              | 2-1          |  |

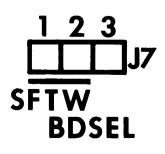

| J7                | 2–1<br>2–3                   |       | Software setting of CRU bit 9 can either delete<br>memory or allow memory access by the system<br>Setting of CRU bit 9 doesn't affect memory access                                                            | 2-1 | 2-1                              | 2-1          |  |

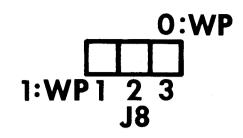

| J8                | 2-1<br>2-3                   | 2.4.4 | Selects bit logic level to write to CRU bits 0 to 3<br>to cause Write Protect at BLK0 to BLK3<br>***One written to bits 0-3 causes WP of BLK0 to BLK3<br>***Zero written to bits 0-3 causes WP of BLK0 to BLK3 | 2-1 | 2-1                              | 2-1          |  |

| J9                | 2-1<br>2-3                   | 2.4.5 | Battery placed in circuit (connected to ground).<br>User must install before battery can be used.<br>Battery disconnected (board is shipped this way)                                                          | 2-3 | 2-3                              | 2-3          |  |

## TABLE 2-1. JUMPER SETTINGS

#### NOTES

- \* Jumpers J1 to J4 select or deselect memory blocks BLK0 to BLK3 respectively from battery backup. These jumpers can be used to deselect NMOS memory, if used, because of NMOS memory's high current requirements.

- **\*\*** XAO to XA3 are extended address lines (20 address lines)

- \*\*\* Note that if J8 is set to the 2-3 position, then an I/O reset can cause a write protect of all memory blocks; if J8 is set to the 1-2 position, then an I/O reset will not cause memory write protect. (See WARNING in section 2.4.4.)

NOTE: Each block contains 4 K bytes as shown

FIGURE 2-1. MEMORY BLOCK ORGANIZATION

# 2.4.1 Connect/Disconnect Battery from Memory Blocks (Jumpers J1 to J4)

When a power failure occurs, the board's battery backup feature will provide power to battery blocks as selected at jumpers J1 to J4. These jumpers allow the user to connect or disconnect the battery backup from each of the four blocks of RAM (BLKO to BLK3), shown organized in Figure 2-1. Since CMOS and NMOS RAM can be mixed onboard by individual blocks, these jumpers allow the user to disconnect battery backup to high power RAMS (i.e., NMOS). Prolonged heavy discharge can accidently shorten the life of a battery. The jumpers connect/disconnect the battery backup feature as shown below:

|           |        |                  | <u>Setting</u>  |

|-----------|--------|------------------|-----------------|

|           |        | Battery Ba       | ackup Feature 🚊 |

| RAM Block | Jumper | <u>Connected</u> | Disconnected    |

| BLKO      | J1     | 2-3              | 2-1             |

| BLK1      | J2     | 2-3              | 2-1             |

| BLK2      | J3     | 2-3              | 2-1             |

| BLK3      | J4     | 2-3              | 2-1             |

NOTE

The TM 990/204 memory board is designed to be addressed by TM 990 CPU boards capable of addressing 64 K bytes (32 K words) or 1 M bytes (500 K words) depending upon the microprocessor used. Because the TM 990/204 board can be populated with memory and addressed as 16-bit words, the addressing scheme for jumpers J5 and J6 utilizes 15 address lines (for 32 K words) or 19 address lines (for 500 K words).

Jumpers J5 and J6 designate the use of either extended addressing (19 address lines) or 15 address lines, depending upon the address structure of the microcomputer used. If extended addressing is used, extended address lines XAO, XA1, XA2, and XA3 are monitored

along with lines A0 to A3; otherwise, only lines A0 to A3 are checked by the lower-bound comparator and upper-bound comparator as set at platforms S1 and S2 (see section 2.5.1). For TMS 9900 and S481 microprocessors, 15 address lines are decoded.

Two jumpers are provided, J5 and J6, one each for switches S1 and S2, which designate the lower bound and upper bound of memory respectively. Both jumpers should be set to decode the same address-line quantities. Jumper

J5 designates address-line quantity for the memory lower bound (as set at platform S1), and jumper J6 designates address line quantity for the memory upper bound (as set at platform S2). Set the jumpers as shown below:

| Jumpers J5/J6                              | Setting for 15 | Setting for 19 |

|--------------------------------------------|----------------|----------------|

| Setting                                    | Address Lines  | Address Lines  |

| J5 (Memory Lower Bo<br>J6 (Memory Upper Bo | ound) 2-1      | 2-3<br>2-3     |

2.4.3 Allow or Prevent Software to Delete/Map Board in System (Jumper J7)

The board's memory can be deleted from the system or mapped into the system according to the software setting of bit 9 on the CRU (Communication Register Unit). This feature is allowed only if jumper J7 is set 2-1. Setting jumper J7 2-3 prevents using

this software feature (setting of bit 9 will have no effect). Use of this CRU feature is further defined in section 3.6.

> Jumper J7 <u>Setting</u>

> > 2-1 Allows software control to delete/enable memory

> >  2-3 Disables software control to delete/enable memory

2.4.4 Select Logic Level to Enable/Disable Write Protect (Jumper J8)

Each of the four blocks of memory can be designated as write protected (cannot be written to, just read from) by software through CRU bits 0 to 3 as

described in section 3.4.1. Jumper J8 allows selection of the logic level (a one or a zero) used by software to select this write protect feature. This option is one of convenience (i.e., write a one or a zero to a CRU bit); however, this jumper will be more effective for I/O reset purposes. If a one logic level is chosen (J8 set 2-1), then memory will not be write protected by an I/O reset

(e.g., microcomputer RESET switch pressed); if a zero logic level is chosen, then memory will be write protected by an I/O reset. This latter position (2-3) will give optimum protection against the CPU altering RAM values should the CPU come up in an unknown state.

Note that a zero logic level (J8 set 2-3) is the default value when the jumper plug is totally removed, as this postion is in the etch of the board (default value if no jumper inserted). When using the J8 jumper in the 2-1 postion, the TM 990/204 requires a proper power-on reset (PRES.B-) to prevent erroneous data from being written into the board during powerup while the CPU is in an unknown state. In using the TM 990/204 with current CPU modules, including TM 990/100, TM 990/101, and TM 990/1481, the user must provide this reset capability offboard. Without such an offboard reset function, it is not recommended to use those CPU modules with the TM 990/204 with J8 in 2-1 position.

| Jumper J8<br><u>Setting</u> | Logic Level<br>To Enable WP | Comment                   |

|-----------------------------|-----------------------------|---------------------------|

| 2-1                         | One                         | No Write Protect on RESET |

| 2-3                         | Zero                        | Write Protect on RESET    |

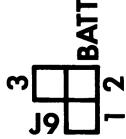

2.4.5 Connect Battery into Battery-Backup Circuit (Jumper J9)

The battery is shipped disconnected from the board circuitry by jumper J9. To connect the battery into the board circuitry, jumper as follows:

| Jumper        | J  | 1 | 1 |

|---------------|----|---|---|

| <u>Settir</u> | 1g |   |   |

| 2-1 | Battery connected into |

|-----|------------------------|

|     | board backup circuitry |

| 2-3 | Battery disconnected   |

|     | from board circuitry   |

## NOTE

Throughout this section, the terms "switch" and "jumper platform" are used interchangeably. The board is populated with five jumper platforms (S1 to S4 & S6). Selection of a position on the platform is made by inserting a jumper between two points on the platform. However, a standard DIP switch can be inserted on the platform to substitute for the jumper. Platform setting descriptions use the nomenclature silkscreened on the board.

Several options are available on the TM 990/204. In summary:

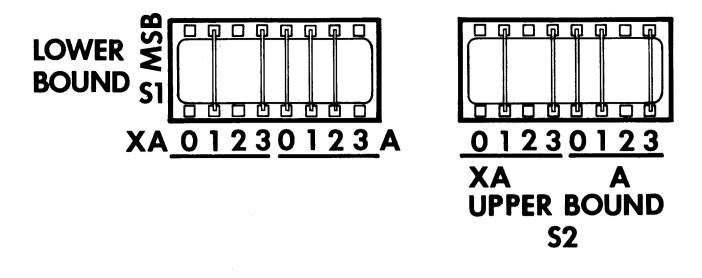

- S1: Selects lower address bound of RAM. If extended addressing (500 K words) is used, settings S1-XAO to S1-A3 are used; if nonextended addressing (32 K words) is used, only S1-AO to S1-A3 are used. This platform and platform S2 allow mapping the board into a system memory map scheme. Jumper J5 must be set to the number of address lines used (15 for 32 K words or 19 for 500 K words).

- S2: Selects upper address bound of RAM. If extended addressing (500 K words) is used, all switches S2-XAO to S2-A3 are used; if nonextended addressing is used (32 K words), only S2-AO to S2-A3 are used. Jumper J6 must be set to the number of address lines used (15 for 32 K words or 19 for 500 K words).

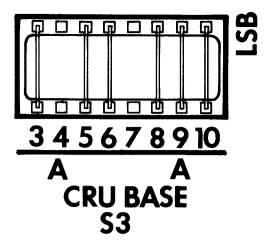

- S3: Selects the eight most-significant bits of the CRU address (values on address lines A3 to A10); this allows mapping the board's 16 CRU bits into the system CRU address scheme.

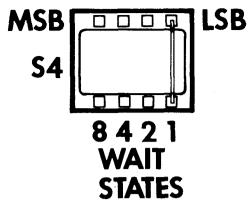

- S4: This four-position platform allows selection of 0 to 15 wait states depending upon access time of memory used and system clock.

- S5: Allows designating the entire board as write protected or not write protected. Designation can be made while board is installed in chassis. If write protect is selected (WP), this overrides any other jumper or software setting. If no write protection (NO WP) is selected, write protection is designated by other jumper settings and CRU bits.

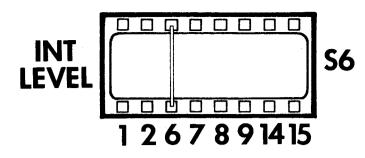

- S6: Selects the interrupt level to the microcomputer board that would occur should a write- protect or execute-protect violation occurand the interrupt is selected by jumper and switch settings. If S6 is unpopulated, an interrupt level would not be sent to the system bus.

These platforms and switches are covered in the following paragraphs:

#### Paragraph

| • | S1 | Lower address bound    | 2.5.1 |

|---|----|------------------------|-------|

| • | S2 | Upper address bound    | 2.5.1 |

| • | S3 | CRU base address       | 2.5.2 |

| • | S4 | Wait states            | 2.5.3 |

| • | S5 | Write protect board    | 2.5.4 |

| • | S6 | Interrupt Level Select | 2.5.5 |

## NOTES

- Platform S1 specifies the 8 MSBs of the lower memory bound, and if BLKO is populated, S1 specifies the beginning address of that block. S2 can be set to a value other than the actual 8 MSBs of the memory end address. These switches designate the addresses that will be interpreted by board hardware as the memory bounds.

- 2. If only 15 address lines are used (word addressing), failure to set jumpers J5 and J6 to 2-1 may inadvertently prohibit memory access.

Platforms S1 and S2 allow mapping the memory into a system memory map. Access to the board memory will be given only if the address is within the bounds specified by these switches. The most-significant bits (MSBs) of two addresses are specified by the user: the 4 or 8 MSBs of the lower address bound and the 4 or 8 MSBs of the upper address bound. Each is designated by an eight-position platform, divided into two four-bit segments:

- (1) four extended address bits (XAO to XA3), and

- (2) four MSBs (A0 to A3) of address lines A0 to A14 (word addressing).

The use of extended and non-extended addressing must first be designated at jumpers J5 and J6 as explained in paragraph 2.4.2. The switches designate the following:

|                                          | Exten         | ded Addre        | ssing                              | <u>Non-Ex</u>       | tended Ad      | dressing                           |

|------------------------------------------|---------------|------------------|------------------------------------|---------------------|----------------|------------------------------------|

|                                          | Plat-<br>form | Setting          | Jumper                             | Plat<br><u>form</u> | Setting        | Jumper                             |

| Memory lower bound<br>Memory upper bound | S1<br>S2      | XAO-A3<br>XAO-A3 | J5 2 <b>-</b> 3<br>J6 2 <b>-</b> 3 | S1<br>S2            | A0-A3<br>A0-A3 | J5 2 <b>-</b> 1<br>J6 2 <b>-</b> 1 |

If extended addressing is <u>not</u> used, set jumpers J5 and J6 to 2-1, and platform settings XAO to XA3 will be ignored. Table 2-2 lists various switch settings and corresponding address lines (in the table, an OFF indicates unjumpered or switch set to OFF, and an ON indicates jumpered or switch set to ON).

The "as shipped" switch S1 and S2 settings for all three versions of the TM 990/204 are shown below:

| TM 990/                                                                  | 204-1,2,3                                | TM 99                                                                    | 0/204-1                                  | ТМ 99                                                                    | 0/204-2                                 | TM 990/204-3                                                             |                                          |

|--------------------------------------------------------------------------|------------------------------------------|--------------------------------------------------------------------------|------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------|--------------------------------------------------------------------------|------------------------------------------|

| SWITCH                                                                   | LOCATION                                 | SWITCH                                                                   | LOCATION                                 | SWITCH                                                                   | LOCATION                                | SWITCH                                                                   | LOCATION                                 |

| S1-XA0<br>S1-XA1<br>S1-XA2<br>S1-XA3<br>S1-A0<br>S1-A1<br>S1-A2<br>S1-A3 | On<br>On<br>On<br>On<br>On<br>Off<br>Off | S2-XA0<br>S2-XA1<br>S2-XA2<br>S2-XA3<br>S2-A0<br>S2-A1<br>S2-A2<br>S2-A3 | On<br>On<br>On<br>On<br>On<br>Off<br>Off | S2-XA0<br>S2-XA1<br>S2-XA2<br>S2-XA3<br>S2-A0<br>S2-A1<br>S2-A2<br>S2-A3 | On<br>On<br>On<br>On<br>Off<br>On<br>On | S2-XA0<br>S2-XA1<br>S2-XA2<br>S2-XA3<br>S2-A0<br>S2-A1<br>S2-A2<br>S2-A3 | On<br>On<br>On<br>On<br>Off<br>Off<br>On |

# TABLE 2-2. LOWER AND UPPER ADDRESS BOUND SELECTION

|     | 1 <sub>PLA</sub> | TFOR | M S1 | OF | 8 S2 | SET | CING |     | LOWER<br>BOUND | UPPER<br>BOUND |

|-----|------------------|------|------|----|------|-----|------|-----|----------------|----------------|

| XAO | XA 1             | XA2  | XA3  |    | AO   | A 1 | A2   | A3  | (S1)           | (S2)           |

| ON  | ON               | ON   | ON   |    | ON   | ON  | ON   | ON  | 00000          | OOFFE          |

| ON  | ON               | ON   | ON   |    | ON   | ON  | ON   | OFF | 01000          | O 1FFE         |

| ON  | ON               | ON   | ON   |    | ON   | ON  | OFF  | ON  | 02000          | 02FFE          |

| ON  | ON               | ON   | ON   |    | ON   | ON  | OFF  | OFF | 03000          | 03FFE          |

| ON  | ON               | ON   | ON   |    | ON   | OFF | ON   | ON  | 04000          | 04FFE          |

| ON  | ON               | ON   | ON   |    | ON   | off | ON   | OFF | 05000          | 05FFE          |

| ON  | ON               | ON   | ON   |    | ON   | OFF | OFF  | ON  | 06000          | 06FFE          |

| ON  | ON               | ON   | ON   |    | ON   | OFF | OFF  | OFF | 07000          | 07FFE          |

| ON  | ON               | ON   | ON   |    | OFF  | ON  | ON   | ON  | 08000          | 08FFE          |

| ON  | ON               | ON   | ON   |    | OFF  | ON  | ON   | OFF | 09000          | 09FFE          |

| ON  | ON               | ON   | ON   |    | OFF  | ON  | OFF  | ON  | 000A0          | OAFFE          |

| ON  | ON               | ON   | ON   |    | OFF  | ON  | OFF  | OFF | 0B000          | OBFFE          |

| ON  | ON               | ON   | ON   |    | OFF  | OFF | ON   | ON  | 00000          | OCFFE          |

| ON  | ÓN               | ON   | ON   |    | OFF  | OFF | ON   | OFF | 0D000          | ODFFE          |

| ON  | ON               | ON   | ON   |    | OFF  | OFF | OFF  | ON  | 0E000          | OEFFE          |

| ON  | ON               | ON   | ON   |    | off  | OFF | OFF  | OFF | 0F000          | OFFFE          |

|     |                  |      |      | •  |      |     |      |     |                |                |

| ON  | OFF              | OFF  | OFF  |    | OFF  | OFF | OFF  | OFF | 7F000          | 7FFFE          |

| OF  | F ON             | ON   | ON   |    | ON   | ON  | ON   | ON  | 80000          | 80FFE          |

| OFI | f on             | ON   | ON   | •  | ON   | ON  | ON   | OFF | 81000          | 8 1FFE         |

|     |                  |      |      | •  |      |     |      |     |                |                |

| ÚFI | r off            | OFF  | OFF  |    | OFF  | OFF | OFF  | OFF | FF000          | FFFFE          |

Address line is a 0 = ON switch setting (jumpered)

Address line is a 1 = OFF switch setting (unjumpered)

FIGURE 2-2. SWITCH S1 & S2 ADDRESS SELECTION (for examples)

## NOTE

The memory in BLKO will always start at the address bits selected in platform S1.

Address Example 1 (No Extended Addressing):

System does not have extended addressing, and BLK0 and BLK1 are populated with the eight K bytes of memory located between addresses 1000<sub>16</sub> and 2FFE16:

- Set jumpers J5 and J6 to 2-1 (no extended addressing)

- Set platform S1-A0 to S1-A3 to ON ON OFF Set platform S2-A0 to S2-A3 to ON ON OFF ON OFF (100016 lower bound)

- (2FFE<sub>16</sub> upper bound)

- Platform S1-XA0 to S1-XA3 and S2-XA0 to S2-XA3 are ignored as jumpers J5 and J6 are set 2-1. The applicable halves of platforms S1 and S2 are shown properly jumpered in Figure 2-2.

Note that memory must exist in contiguous blocks, with each block taking up 4 K bytes of address space with BLKO followed by BLK1, followed by BLK2, followed by BLK3.

Address Example 2 (Extended Addressing):

The example system uses extended addressing with BLKO and BLK1 populated with the eight K bytes of memory located between addresses A1000<sub>16</sub> and A2FFE<sub>16</sub>). The switch configuration is shown in Figure 2-2.

- Set jumpers J5 and J6 to 2-3 (extended addressing) •

- Set platform S1-XAO to S1-XA3 to OFF ON OFF ON (A----16 extended • address)

- Set platform S1-A0 to S1-A3 to ON ON ON OFF (A100016 remainder of address)

- Set platform S2-XAO to S2-XA3 to OFF ON OFF ON (A----16 extended address)

- Set platform S2-A0 to S2-A3 to ON ON OFF ON (A2FFE16 remainder of address)

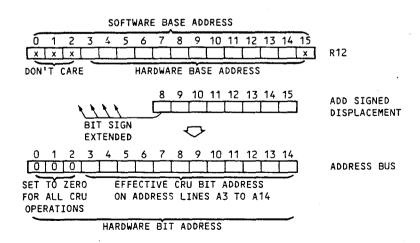

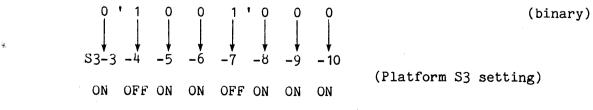

2.5.2 Select Start of CRU Address Space (Jumper Platform S3)

Through the Communications Register Unit (CRU), the microprocessor can serially communicate using single-bit and multiple-bit instructions to external hardware. The TMS 9900 and S481 microprocessors can address from 1 to 4096 CRU bits by using the value on address lines A3 to A14. This value is placed in register 12 before executing one of the five CRU instructions (see your microcomputer user's guide for further information on CRU instructions and addressing). The four LSB's of this 12-bit address select one of the 16 CRU bits as further defined in Section 3. The eight MSB's of this address are selected at jumper platform S3, which allows the user to designate a beginning CRU address in order to map the TM 990/204 board into an overall system CRU address scheme. For example, if three TM 990/204 boards are in the same system, each <u>must</u> have a unique CRU address so that their CRU bits can be selected individually. The boards' switches can be set so that each board's address is contiguous with the other boards.

Two CRU terms:

- CRU hardware base address: The value on bits 3 to 14 of register 12 when a CRU instruction is executed. A displacement is added or subtracted from this value (as required by the instruction) to select the desired bit to address.

- CRU software base address: The entire contents of register 12 when a CRU instruction is executed.

Table 2-3 shows the settings on platform S3. The Software Base Address column lists the resulting values in bits 3 to 10 of register 12, (thus, also on address lines A3 to A10 that will be compared to the platform values). This is the same as the eight MSB's of the CRU hardware base address. The four LSB's on the address lines (A11 to A14) address one of the 16 CRU functions on the board. If the values at platform S3 and address lines A3 to A10 compare, the corresponding board CRU functions will be addressed. Note that an ON setting (jumper installed) corresponds to a zero address bus value, and an OFF setting (jumpered not installed) corresponds to a one address bus value.

FIGURE 2-3. CRU ADDRESS NOMENCLATURE

| TABLE 2-3. | CRU | BASE | ADDRESS | SELECTION |

|------------|-----|------|---------|-----------|

|------------|-----|------|---------|-----------|

|     |      | SWIT | CH S | 3 SETT   | ING        | <del></del> |      | SOFTWARE        | HARDWARE        |

|-----|------|------|------|----------|------------|-------------|------|-----------------|-----------------|

| A3  | A 4  | A5   | A6   | A7       | <b>A</b> 8 | A9          | A 10 | BASE<br>ADDRESS | BASE<br>ADDRESS |

| ON  | ON   | ON   | ON   | ON       | ON         | ON          | ON   | 0000            | 0000            |

| ON  | ON   | ON   | ON   | ON       | ON         | ON          | OFF  | 0020            | 00 10           |

| ON  | ON   | ON   | ON   | ON       | ON         | OFF         | ON   | 0040            | 0020            |

| ON  | ON   | ON   | ON   | ON       | ON         | OFF         | OFF  | 0060            | 0030            |

| ON  | ON   | ON   | ON   | ON       | OFF        | ON          | ON   | 0080            | 0040            |

| ON  | ON   | ON   | ON   | ON       | OFF        | ON          | OFF  | OAOO            | 0050            |

|     |      |      |      | •        |            |             |      |                 |                 |

| ON  | ON   | ON   | ON   | OFF      | ON         | ON          | ON   | 0100            | 0080            |

| ON  | ON   | ON   | ON   | OF'f     | ON         | ON          | OFF  | 0120            | 0090            |

|     |      |      |      | •        |            |             |      |                 |                 |

| ON  | OFF  | OFF  | OFF  | OFF      | OFF        | OFF         | OFF  | OFEO            | 07F0            |

| OFF | ON   | ON   | ON   | ON       | ON         | ON          | ON   | 1000            | 0800            |

| OFF | ON   | ON   | UN   | ON<br>•  | ON         | ON          | OFF  | 1020            | 08 10           |

| OFF | OF'F | OFF  | OFF  | •<br>OFF | OFF        | off         | OFF  | 1FEO            | OFFO            |

NOTE: 0 = ON switch setting or jumpered (tied low) 1 = OFF switch setting or not jumpered (tied high)

NOTES

- Setting shown for hardware base addresses 0480<sub>16</sub> - 048F<sub>16</sub>

- 2. Jumpered = zero address line Unjumpered = one address line

- 3. As shipped configuration for 204-1, -2, -3.

FIGURE 2-4. CRU SWITCH SETTINGS AT S3 (for example below)

Example:

Determine the CRU software base address (contents to load into register 12) and S3 settings when a hardware base address of  $0480_{16}$  is used.

1. Write <u>hardware base address</u> in binary (corresponding to the eight MSBs of the address lines):

2. Place another zero on the right and shift left one bit (multiply hardware base address by 2 to get software base address):

0 1 1 ' 0 0 0 0 0'0 0 0 0 0 1 0 0 0 0 ' 0 0 0 n 0 9 0 0 (hex)

3. To determine switch settings, write the <u>hardware base address</u>. The eight MSB's on address lines A3 to A14 are the settings of switch S3 with a zero indicating an ON setting and a one indicating an OFF setting:

Thus, for a hardware base address of  $0480_{16}$  (step 1 above), load register 12 with  $0900_{16}$  (step 2 above) and set switches as in step 3 above. The range of CRU addresses are listed in Table 2-3.

Because the TM 990/204 memory expansion board may be populated with different

speed (access time) memories or used with different system bus clocks, wait states may be required to complete a memory read/write cycle. Platform S4 allows setting 0 to 15 wait states as shown by the settings in Tables 2-4 and 2-5.

For example, the TM 990/204 is shipped with 6514 CMOS RAMs (450 ns access time) requiring 1 wait state with a 3 MHz clock or 2 wait states with a 5 MHz clock.

TABLE 2-4. WAIT STATE SELECTION AT PLATFORM S4

|       |        |           | 1      | 114 T (D            |                           | RIOD IN NS |

|-------|--------|-----------|--------|---------------------|---------------------------|------------|

| SWITC | CH SET | TING AT   | C S4 ' | WAIT                | 3 MHz                     | 5 MHz      |

| 8     | 4      | 2         | 1      | STATES <sup>2</sup> | CLOCK                     | CLOCK      |

|       |        |           |        |                     |                           |            |

| OFF   | OFF    | OFF       | OFF    | 0                   | 000 ns                    | 000 ns     |

| OFF   | OFF    | OFF       | ON     | 1                   | 330 ns                    | 198 ns     |

| OFF   | OFF    | ON        | OFF    | 2                   | 660 ns                    | 396 ns     |

| OFF   | OFF    | ON        | ON     | 3                   | 990 ns                    | 585 ns     |

|       | ~ **   |           | 0.77   |                     | 1000                      |            |

| OFF   | ON     | OFF       | OFF    | 4                   | 1320 ns                   | 792 ns     |

| OFF   | ON     | OFF       | ON     | 5                   | 1650 ns                   | 990 ns     |

| OFF   | ON     | ON        | OFF    | 6                   | 1980 ns                   | 1188 ns    |

| OFF   | ON     | ON        | ON     | 7                   | 2310 ns                   | 1386 ns    |

| ON    | OFF    | OFF       | OFF    | 8                   | 2640 ns                   | 1584 ns    |

| ON    | OFF    | OFF       | ON     | 9                   | 2970 ns                   | 1782 ns    |

| ON    | OFF    | ON        | OFF    | 10                  | 3300 ns                   | 1980 ns    |

| ON    | OFF    | ON        | ON     | 11                  | 3630 ns                   | 2178 ns    |

|       | 011    | <b>UN</b> | ON     | ••                  | <b>J</b> 0 <b>J</b> 0 IIS | 2110 115   |

| ON    | ON     | OFF       | OFF    | 12                  | 3960 ns                   | 2376 ns    |

| ON    | ON     | OFF       | ON     | 13                  | 4290 ns                   | 2574 ns    |

| ON    | ON     | ON        | OFF    | 14                  | 4620 ns                   | 2772 ns    |

| ON    | ON     | ON        | ON     | 15                  | 4950 ns                   | 2970 ns    |

NOTE: 1. ON = jumpered; OFF = unjumpered

| TABLE 2-5. WAIT STATES FOR EXAMPLE MEMO |

|-----------------------------------------|

|-----------------------------------------|

|              | WAIT STATES |       |                                          |   |  |

|--------------|-------------|-------|------------------------------------------|---|--|

| MEMORY SPEED | 3 MHz       | 5 MHz | MEMORY TYPE                              | 1 |  |

| 150 ns       | 0           | 0     | TMS 2114-15 (NMOS)                       | ] |  |

| 250 ns       | 0           | 1     | TMS 2114-25 (NMOS), uPD444/6514-3 (CMOS) |   |  |

| 450/500 ns   | 1           | 2     | uPD444/6514 (CMOS)                       |   |  |

| 650 ns       | 2           | 3     |                                          |   |  |

| 800 ns       | 2           | 4     |                                          |   |  |

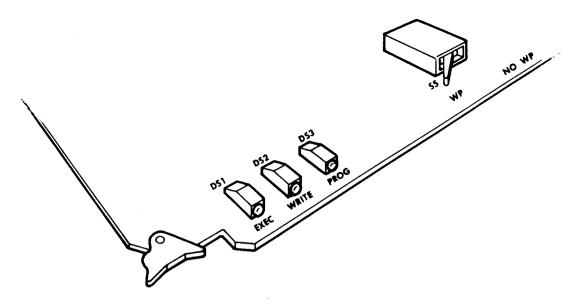

FIGURE 2-5. LEDs AND WRITE PROTECT SWITCH AT FRONT OF BOARD

2.5.4 Write Protect Entire Board (Switch S5)

Switch S5 allows a hardware setting of all the onboard memory to a write protect state (cannot be written to). Switch S5 is accessable from the front of the board when installed in a card cage as shown in Figure 2-5. Set the switch as follows:

Switch S5 Setting

WPWrite protect all memoryNO WPWrite protect blocks only as set by software

When the switch is set to NO WP, write protect is CRU selectable (software selectable) on a block basis through CRU bits 0 to 3.

When switch S5 is set to WP, software cannot disable the write protect status of the entire memory as set by this switch. Also, when set to WP, a write-protect interrupt will not occur <u>unless</u> a write-protect interrupt was also enabled via CRU bits 0 to 3 and the interrupt level set at platform S6. Merely setting S5 to WP <u>does not</u> also cause a write-protect interrupt. The setting of this switch can be checked through software by reading CRU bit 10.

2.5.5 Select Level of Interrupt to CPU (Platform S6)

Several interrupt levels or a no-interrupt can be selected. This interrupt will go to the CPU board if a level is selected at platform S6 and either of the following two violations is attempted:

- Attempt to write into a memory block which has been designated as write protected through CRU bits 0-3

- Attempt to execute an instruction in a block of memory which has been designated as execute-protected through CRU bits 4-7.

If an attempt is made to violate these CRU-selectable protections, an interrupt, if jumpered at plat-

form S6, is sent to the CPU. The interrupt service routine can then check for possible causes (CRU bits 8 and 9 indicate if a write- or executeprotect violation occurred) The following interrupts can be selected at S6: 1, 2, 6, 7, 8, 9, 14, 15 as shown on the silkscreen at the jumper platform.

The adjacent platform drawing shows interrupt  $\boldsymbol{6}$  jumpered, the level jumpered as shipped.

## 2.6 LED INDICATORS

Three LEDs are provided at the front of the board as shown in Figure 2-5. These indicate the following as seen from left to right:

- EXEC (DS1): Execute-protect violation attempted. Will remain lit until reset by writing first a zero and then a one to CRU bit 8.

- WRITE (DS2): Write-protect violation attempted. Will remain lit until reset by writing first a zero and then a one to CRU bit 8.

- PROG (DS3): Reserved for user definition. This can be lit or turned off by setting CRU bit 10 to a zero or one respectively.

Note that if enabled at CRU bits 0 to 7, a write-protect or execute-protect violation attempt will always illuminate an LED. However, actual sending of an interrupt depends upon jumpering platform S6.

## 2.7 INSTALLING A MINIMUM SYSTEM

After making the desired jumper and switch settings, the user can install a minimum system as described below. Also, sections 2.9 and 2.10 contain several general demonstration routines, complete with jumper and switch settings, that can be executed to demonstrate general board operation. Make the following attachments and installations:

1) Attach power supply connections to the card cage as shown in the card cage user manual.

Power should always be disconnected when attaching power cable to a chassis or when installing or removing a board from a card cage.

2) Make the proper jumper connections as listed in Table 2-1 and explained in section 2.4. If battery backup is desired, please jumper J9 in the 2-1 postion; this jumper is shipped 2-3 to deselect battery backup. The battery will come to a full charge within 16-20 hours.

- 3) Make the proper platform connections as described in section 2.5.

- 4) Install the microcomputer board and TM 990/204 board into the card cage. If DMA is to be used, make the appropriate modifications to the backplane as described in the card cage user manual.

- 5) Attach the terminal cable to the EIA port on the microcomputer.

- 6) Apply power. If the TIBUG monitor is installed, it should come up by actuating the RESET switch on the microcomputer board and pressing the RETURN key on the terminal.

# 2.8 CONSIDERATIONS

- Do not remove or install the TM 990/204 board while system Vcc power is applied.

- Upon an I/O reset (e.g., by toggling the RESET switch on the microcomputer board), all CRU bits are reset to the zero level. This means that the execute-protect feature is disabled after an I/O reset and must be set by software (the write-protect feature is conditional on jumper J8 set 2-3; see section 2.4.4).

- Battery backup merely retains RAM data during a power loss to the system; other board logic is not backed up. Battery data is provided in section 2.11.

- If more than one memory module is in a system, each must occupy unique (1) memory space and (2) CRU address space.

# 2.9 EXAMPLE PROGRAM

The following programs can be used to immediately demonstrate operation of the TM 990/204 expansion memory board.

The following program demonstrates communication to the board via the CRU (the CRU is further explained in Section 3). This program, if loaded at memory address  $1000_{16}$  on the memory board will cause the user LED (marked DS3 as shown in Figure 2-5) to blink. Loading and executing this program requires that the monitor (e.g., TIBUG) be installed on the microcomputer board.

The following are program aspects:

- 1) CRU software base address is  $0900_{16}$  (switch S3 set as in Figure 2-4).

- Minimum memory required is a half block (more optional) inserted in BLKO.

- 3) Memory start address is 1000<sub>16</sub> with platforms S1 and S2 set as shown in Figure 2-2. If extended addressing used, switches S1-XA0 to S1-XA3 and S2-XA0 to S2-XA3 are set to all ON.

- 4) Jumpers J5 and J6 set to 2-1 for non-extended addressing or 2-3 for extended addressing, as required.

- 5) Jumper J8 is set 2-1 for no write protect at RESET.

Do <u>not</u> use the CRU command of the monitor after powerup and before executing this program as bits can be mistakenly written to that would affect program execution.

Powerup the system. Toggle the RESET switch on the microcomputer board; the monitor heading should be printed on the terminal.

Load the following program at the memory address shown in the left column below beginning at  $1000_{16}$  using the memory inspect/change command (M) of the monitor (TIBUG commands are used herein). Beginning at address  $1000_{16}$ , change the location's contents to the object values as shown in the listing below (Objt column), then repeat at the next memory address using the space bar. When last value is entered, complete this final memory change with a carriage return, then use the monitor to change the Program Counter to  $1000_{16}$ , and execute with the monitor execute (E) command.

Mem. Addr Objt

| 1000 02E0<br>1002 1020 | Ĺ      | WPI >           | 1020   | SET WORKSPACE POINTER               |

|------------------------|--------|-----------------|--------|-------------------------------------|

| 1004 020C<br>1006 0900 | L      | I R1            | 2,>900 | LOAD SOFTWARE BASE ADDRESS INTO R12 |

| 1008 1D0A              | LOOP S | BO 10           |        | TURN ON USER LED                    |

| 100A 0600              | D      | EC RO           |        | DECREMENT COUNTER TO ZERO           |

| 100C 16FE              | J      | 'NE <b>\$</b> - | 2      | LOOP UNTIL ZERO                     |

| 100E 1EOA              | S      | BZ 10           |        | TURN OFF USER LED                   |

| 1010 0600              | D      | EC RO           |        | DECREMENT COUNTER TO ZERO           |

| 1012 16FE              | J      | 'NE \$-         | 2      | LOOP UNTIL ZERO                     |

| 1014 10F9              | J      | 'MP LO          | OP     | REPEAT BLINK SEQUENCE               |

Exit this loop by pressing the microcomputer RESET switch.

# 2.10 DEMONSTRATING WRITE PROTECT USING TIBUG COMMANDS

The programmable (through the CRU) write-protect bits can be demonstrated by using the system monitor (e.g., TIBUG, the commands used herein).

The following are program aspects (the first five steps are the same as for the program in 2.8; the sixth step has been added):

- 1) CRU software base address is  $0900_{16}$  (hardware base address of  $0480_{16}$ ) used with switch S3 set as shown in Figure 2-4.

- 2) Minimum memory required is a half block (more optional) inserted in BLK0.

- 3) Memory start address is 1000<sub>16</sub> with switches S1 and S2 set as shown in Figure 2-2.

- 4) Jumpers J5 and J6 set to 2-1 for non-extended addressing or 2-3 for extended addressing.

- 5) Jumper J8 set 2-1 for no write protect at RESET (also designates that a one sets write protect and a zero disables write protect when writing to CRU bits 0 to 3 (corresponding to blocks BLK0 to BLK3)).

- 6) Platform S6 unjumpered so that no interrupt will be issued when a write protect violation occurs.

By using the CRU (C) command of the monitor (e.g., TIBUG), a populated block of memory can be write protected or unprotected. This feature can be then demonstrated by using the memory inspect/change (M) monitor command to attempt changing memory (writing to it).

To address the board as mapped into the CRU at software base address  $0900_{16}$ , use the CRU inspect/change command (C) running under the monitor. Then write to the CRU by designating a value to apply to the CRU address. See your microcomputer user's guide for detail information on this TIBUG command.

To demonstrate write protecting BLKO, do the following exercise at the terminal (note, CR = carriage return, SP = space, MS = minus key, and XXXX = unknown hex value).

## Keyboard Interaction

## Comment

?C 900 (CR) 0900 = XXXX 0000 (CR)?M 1000 (CR) 1000 = XXXXAAAA (SP) 1002 = XXXXBBBB (SP) 1004 = XXXXCCCC (SP) 1006 = XXXX(MS) 1004 = CCCC(MS) 1002 = BBBB(MS)1000 = AAAA(CR) 20 900 (CR) 0900 = 0000 0401 (CR) ?M 1000 (CR) 1000 = AAAA1111 (SP) 1002 = BBBB2222 (SP) 1004 = CCCC3333 (SP) 1006 = XXXX(MS) 1004 = CCCC(MS) 1002 = BBBB(MS) 1000 = AAAA(CR) ?

View CRU values beginning at 090016 CRU bits to zero (no write protect)<sup>1</sup> Inspect beginning of memory Change address contents to AAAA Change address contents to BBBB Change address contents to CCCC Minus key returns to previous address Value changed (address written to) Value changed Value changed Return to CRU address 090016 Write protect BLKO, turn on user LED1 Return to memory again Attempt to change (write to) address Attempt to change address contents Attempt to change address contents Minus key returns to previous address Contents unchanged, write protected Contents unchanged. write protected Contents unchanged, write protected

NOTE: 1. All zeroes written to the CRU base address disables write protect and turns off the user LED. A hex pattern of 0401 to the CRU base address contains two one-value bits which enable write protect and turn on the user LED.

## 2.11 BATTERY BACKUP

The TM 990/204 module comes with a 3.6 V dc (nominal) battery which supplies Vcc to the memory chips in case of a power failure. Battery backup is provided for a 96-hour period on a fully populated board, with additional time on a partially populated board. Onboard circuitry determines a power failure to make the switch to battery backup.

The module is shipped with the battery disconnected from onboard circuitry. Jumper J9 must be set 2-1 for connecting the battery to the backup circuitry. Jumpers J1 to J4 select battery backup for RAM blocks BLKO to BLK3 respectively; these must be installed 2-3 to be connected to battery backup. The user is able to specify battery backup for just part of the memory blocks; this permits a mix of CMOS RAM and NMOS RAM. Because NMOS RAM requires a high amount of current; jumpers J1 to J4 allow NMOS blocks to be deselected.

Two manufacturers that provide replacement batteries for the TM 990/204:

1) Part no.: MS2501 and MS2503

Company: Gould, Inc. Portable Battery Division 931 N. Vandalia Street St. Paul, Minnesota 55114

- 2) Part no.: 41B019AD00201

- Company: General Electric Battery Department P.O. Box 861 Gainesville, Fla. 32602

Battery specifications are listed in section 1.3. Detail specifications are available from the manufacturer.

If the Gould model MS2501 is preferred, three batteries are used. In this case, inter-battery connection is made on the board by soldering the battery leads to the plated through holes positioned between the first and second batteries and between the second and third batteries on the board.

CAUTION

Do not place or lay the TM 990/204 Module on a conductive surface. You may seriously damage the battery and CMOS RAM if a metal surface touches the conductor side of the module.

#### SECTION 3

## PROGRAMMING THE TM 990/204

#### 3.1 GENERAL

The TM 990/204 has several programming features using the Communication Register Unit (CRU). Each board must have a unique CRU address, and the selection of the CRU addresses is defined in section 2.5.2 of this manual and in your microcomputer user's guide. Table 3-1 is a summary of the 16 programmable CRU addresses on the TM 990/204, showing the results of reading and applying various logic levels at the different displacements from the base address.

## 3.2 SELECT CRU BASE ADDRESS

The CRU base address is first selected in hardware as shown in section 2.5.2, which describes setting switch platform S3. If more than one TM 990/204 board is in a system, programming will be facilitated by making each board's 16-bit CRU address space contiguous (e.g.,  $0200_{16}$ ,  $0220_{16}$ , etc., for software base addresses). This allows multiboard access using different displacements without changing register 12 contents. Be aware of other CRU addresses in the system; use a software base address of  $0200_{16}$  or greater to avoid conflicts with dedicated CRU features on the microcomputer board.

CAUTION

In constructing a CRU map for a system, be careful that CRU addresses for each board are unique in the system so that CRU addresses on one board do not conflict with addresses on other boards.

Example to load the software base address:

LI R12,>200 SET SOFTWARE BASE ADDRESS OF 0200

This will be the CRU address used for some examples in this section. Once the software base address has been chosen at switch S3 and loaded into register 12, single-bit CRU instructions can be used to address any of the CRU bits:

| SBZ | 0 | BLKO | NOT WRITE PROTECTED |

|-----|---|------|---------------------|

| SBO | 1 | BLK1 | WRITE PROTECTED     |

Or the same effect can occur using multibit instructions:

| LI   | R1,>0200 | LOAD | BINARY  | VALUE  | 0000  | 0010   | IN   | 1ST  | BYTE | OF | R 1 |

|------|----------|------|---------|--------|-------|--------|------|------|------|----|-----|

| LDCR | R1,2     | BLKO | NOT WRI | TE PRI | ED; I | BLK1 I | WRIT | E PF | RTED |    |     |

## 3.3 CRU BITS

Table 3-1 lists the different functions available through the CRU. These are covered in the following paragraphs.

NOTE

An I/O reset (e.g., caused by pressing the microcomputer RESET switch) will place all CRU bits in the zero state.

| DIS-<br>PLACE-<br>MENT | READ BIT MEANING                                                                                       | <sup>1</sup> WRITE-TO-BIT EFFECT                                                                                                                                                                                                                                                                                         |

|------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                      | Setting of BLKO write protect<br>bit as set according to<br>WRITE-TO-BIT column on right               | <pre>20 = BLK0 not write protected 21 = BLK0 write protected</pre>                                                                                                                                                                                                                                                       |

| 1                      | Setting of BLK1 write protect<br>bit as set according to<br>WRITE-TO-BIT column on right               | <pre>20 = BLK1 not write protected <sup>2</sup>1 = BLK1 write protected</pre>                                                                                                                                                                                                                                            |

| 2                      | Setting of BLK2 write protect<br>bit as set according to<br>WRITE-TO-BIT column on right               | <pre>20 = BLK2 not write protected 21 = BLK2 write protected</pre>                                                                                                                                                                                                                                                       |

| 3                      | Setting of BLK3 write protect<br>bit as set according to<br>WRITE-TO-BIT column on right               | <pre>20 = BLK3 not write protected <sup>2</sup>1 = BLK3 write protected</pre>                                                                                                                                                                                                                                            |

| 4                      | Setting of BLKO execute pro-<br>tect bit as set according to<br>WRITE-TO-BIT column on right           | 0 = BLKO not execute protected<br>1 = BLKO execute protected                                                                                                                                                                                                                                                             |

| 5                      | Setting of BLK1 execute pro-<br>tect bit as set according to<br>WRITE-TO-BIT column on right           | 0 = BLK1 not execute protected<br>1 = BLK1 execute protected                                                                                                                                                                                                                                                             |

| 6                      | Setting of BLK2 execute pro-<br>tect bit as set according to<br>WRITE-TO-BIT column on right           | 0 = BLK2 not execute protected<br>1 = BLK2 execute protected                                                                                                                                                                                                                                                             |

| 7                      | Setting of BLK3 execute pro-<br>tect bit as set according to<br>WRITE-TO-BIT column on right           | 0 = BLK3 not execute protected<br>1 = BLK3 execute protected                                                                                                                                                                                                                                                             |

| 8                      | <pre>0 = No write-protect violation    (latch) 1 = Write-protect violation    occurred (latched)</pre> | <pre>1/0=When a write protect or execute<br/>protect violation occurs, bit<br/>8 or 9 (depending on the vio-<br/>lation) is set to a one and<br/>it (they) remains in that state<br/>until write-bit 8 is reset. Bit</pre>                                                                                               |

|                        | NOTE                                                                                                   | 8 is reset by writing a one to<br>it and then writing a zero to                                                                                                                                                                                                                                                          |

| (                      | he toggle procedure for bit 8<br>set to one then set to zero)<br>s opposite that for bit 11.           | it (i.e., toggle bit 8). If bit<br>8 is not toggled, the value at<br>that bit will remain at its<br>present value. By toggling bit<br>8, LEDs DS1 and DS2 are<br>extinguished and bit 8 is set<br>to a zero state to allow sens-<br>ing a state change should a<br>write-protect or execute-<br>protect violation occur. |

# TABLE 3-1. TM 990/204 CRU MAP (Sheet 1 of 2)

| DIS-<br>PLACE-<br>MENT | READ BIT MEANING                                                                                                                                                               | WRITE-TO-BIT EFFECT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9                      | <pre>0 = No execute-protect violation 1 = Execute-protect violation</pre>                                                                                                      | <pre>0 = Memory available to system 1 = Memory cannot be accessed</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 10                     | 0 = Wrt Prot Switch S5 to WP<br>1 = Wrt Prot Switch S5 to NO WP                                                                                                                | 0 = Turn off user LED DS3<br>1 = Turn on user LED DS3                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 11                     | <pre>0 = Board not addressed (latch);<br/>a change from this state to<br/>a one indicates the board<br/>had been addressed.<br/>1 = Board had been addressed<br/>(latch)</pre> | <pre>1/0=When a board-addressed<br/>condition occurs, bit 11 is set<br/>to a one and remains in that<br/>state until reset.Bit 11 can be<br/>reset by first writing a zero<br/>to it and then writing a one to<br/>it (i.e., toggle bit 11). If<br/>the bit is not toggled, the bit<br/>will remain in its present<br/>state. If bit 11 is toggled,<br/>its read value will be set to<br/>a zero to allow sensing a state<br/>change (to a one) should a<br/>board-addressed condition<br/>occur.</pre> |

| 12                     | Flag bit value as set                                                                                                                                                          | Set Flag bit to one or zero                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |