As you are now the owner of this document which should have come to you for free, please consider making a donation of £1 or more for the upkeep of the (Radar) website which holds this document. I give my time for free, but it costs me money to bring this document to you. You can donate here <u>https://blunham.com/Misc/Texas</u>

Many thanks.

Please do not upload this copyright pdf document to any other website. Breach of copyright may result in a criminal conviction.

This Acrobat document was generated by me, Colin Hinson, from a document held by me. I requested permission to publish this from Texas Instruments (twice) but received no reply. It is presented here (for free) and this pdf version of the document is my copyright in much the same way as a photograph would be. If you believe the document to be under other copyright, please contact me.

The document should have been downloaded from my website <u>https://blunham.com/</u>, or any mirror site named on that site. If you downloaded it from elsewhere, please let me know (particularly if you were charged for it). You can contact me via my Genuki email page: <u>https://www.genuki.org.uk/big/eng/YKS/various?recipient=colin</u>

You may not copy the file for onward transmission of the data nor attempt to make monetary gain by the use of these files. If you want someone else to have a copy of the file, point them at the website. (<u>https://blunham.com/Misc/Texas</u>). Please do not point them at the file itself as it may move or the site may be updated.

It should be noted that most of the pages are identifiable as having been processed by me.

If you find missing pages, pages in the wrong order, anything else wrong with the file or simply want to make a comment, please drop me a line (see above).

It is my hope that you find the file of use to you.

Colin Hinson In the village of Blunham, Bedfordshire.

I put a lot of time into producing these files which is why you are met with this page when you open the file.

TEXAS INSTRUMENTS

# TM 990

# TM 990/310 I/O Expansion Module

# MICROPROCESSOR SERIES<sup>™</sup>

**User's Guide**

# TABLE OF CONTENTS

PAGE

# SECTION

| 1. | INTRODUCTION<br>1.1 General                       | -1                                            |

|----|---------------------------------------------------|-----------------------------------------------|

| 2. | <pre>INSTALLATION AND OPERATION 2.1 General</pre> | 2-1<br>2-2<br>2-2<br>2-2<br>2-5<br>2-7        |

| 3. | THEORY OF OPERATION<br>3.1 General                | 3-1<br>3-5<br>3-6<br>3-7<br>3-7<br>3-7<br>3-9 |

| 4. | APPLICATIONS<br>4.1 General                       | +-1<br>+-2<br>+-2<br>+-3                      |

| 5. | <pre>TM 990/310 PROGRAMMING 5.1 General</pre>     | 5-1<br>5-1<br>5-2<br>5-5<br>5-8               |

## APPENDICES

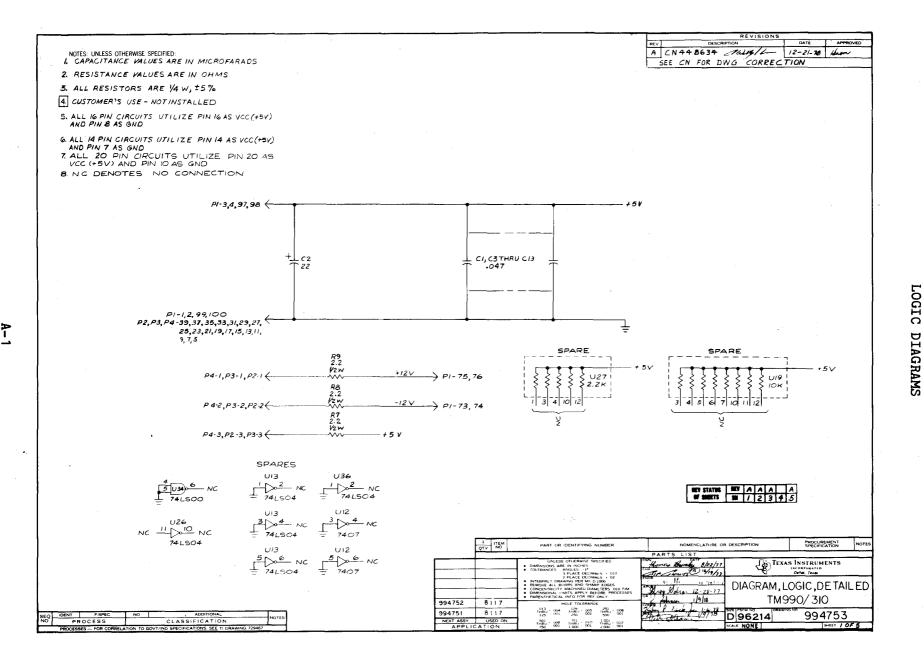

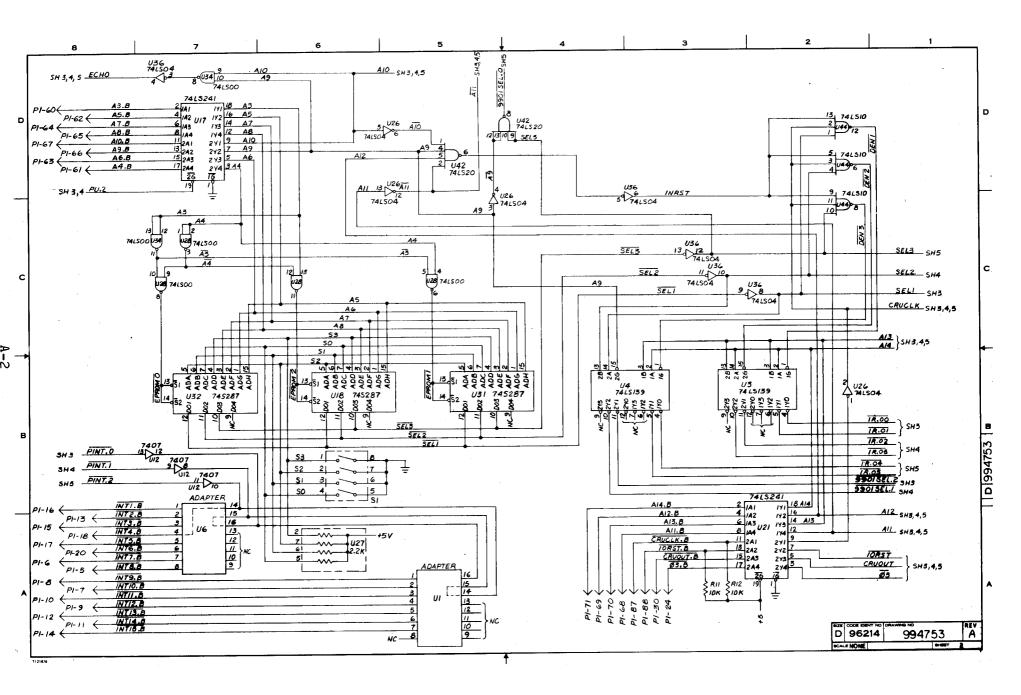

- A LOGIC DIAGRAMS

- B PARTS LIST

TABLE

C TMS 9901 PROGRAMMABLE SYSTEMS INTERFACE DATA MANUAL

# LIST OF ILLUSTRATIONS

| FIGURE                                                                       |                                        | P                                                                                                                                                                                                                                                                                                                                         | AGE                                    |

|------------------------------------------------------------------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Figure                                                                       | 1-1                                    | TM 990/310 48 I/O Module                                                                                                                                                                                                                                                                                                                  | 1–2                                    |

| Figure<br>Figure                                                             |                                        | Use of Switch S1 to Set CRU Address Map<br>Interrupt Priority Jumper Wiring at U1 and U6                                                                                                                                                                                                                                                  |                                        |

| Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure | 3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7 | TM 990/310, 48-Bit I/O Board Simplified Block Diagram<br>CRU Address Decoding.<br>TMS 9901 Logic (Typical of 3).<br>Echo Logic (Typical of 3 Circuits).<br>Interrupt Storage Logic.<br>Interrupt Priority Logic.<br>TM 990/310 Output Timing for LDCR with 16 Bits of One's.<br>TM 990/310 Input Timing for STCR Reading 16 Bits of One's | 3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8 |

| Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure                     | 4-2<br>4-3<br>4-4<br>4-5               | Medium Power Output Signal Conditioning Circuit<br>High Power Output Signal Conditioning Circuit<br>Medium Power Optical Isolator Circuit<br>High Power Optical Isolator Circuit<br>Typical Testing Configuration                                                                                                                         | 4-2<br>4-3<br>4-3<br>4-4               |

| Figure<br>Figure                                                             |                                        | Cable for Example Programs<br>Interrupt Path for Example 5.3.3                                                                                                                                                                                                                                                                            |                                        |

# LIST OF TABLES

PAGE

| Table 2-<br>Table 2- |       | e Connector (P2, P3, P4)<br>ssis Interface Connector |                             |                  |

|----------------------|-------|------------------------------------------------------|-----------------------------|------------------|

| Table 4-             | 1 5MT | Connector Wiring                                     |                             | <br>4-6          |

| Table 5-             | 1 CRU | Map                                                  | • • • • • • • • • • • • • • | <br>5 <b>-</b> 3 |

#### SECTION 1

#### INTRODUCTION

#### 1.1 GENERAL

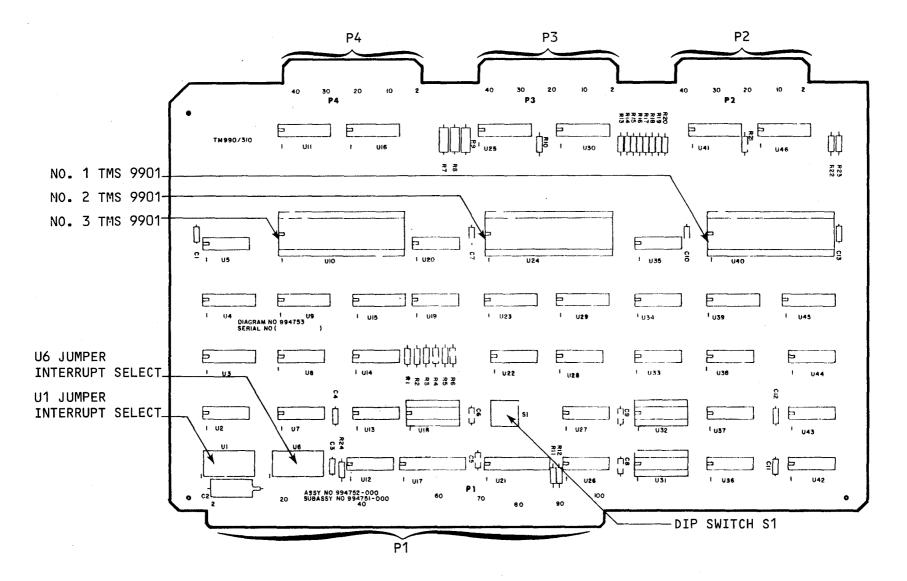

The TM 990/310 is a 48-bit input/output board designed for use with the TM 990/1XX series of Texas Instruments microcomputers. Figure 1-1 is a photograph of the board identifying the edge connectors and principle components of the board.

The TM 990/310 board offers the following features:

- 48 bits individually programmable as inputs or outputs; 27 of these bits may be programmed as logic-zero-sensitive interrupts, rather than inputs or outputs.

- Three negative edge-triggered interrupts and three positive edgetriggered interrupts; each of the six interrupts are edge-detected, stored, and have unique software resets. The edge inputs are pulse shaped by Schmitt trigger circuits.

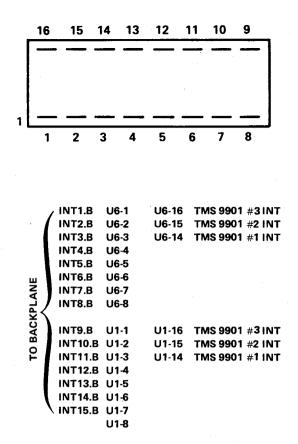

- Backplane interrupt priority is determined by wires installed on two 16-pin platforms.

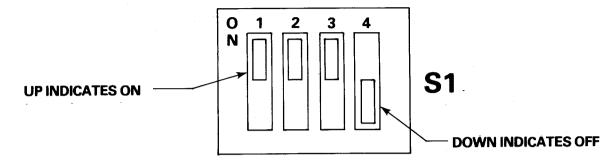

- Board CRU base address is changed by altering the contents of S1, a four-switch DIP.

- All 48 input/output signals may be echoed back into the CRU via STCR instructions.

- Compatible with TM 990 CRU bus.

- CRU addressing provided for up to 14 cards per system.

- In multiple card I/O systems, CRU addressing can be switch selected such that all CRU addresses are consecutive.

- Contains three programable interval timers.

- Plugs into TM 990/510 or equivalent\* chassis.

- Inputs and outputs are TTL compatible.

- May be used with wire-wrap, solder, or ribbon cable edge connectors.

#### 1.2 SPECIFICATIONS

Power requirements: +5 V, +5%, 800 mA.

Temperature Requirements:

Operating Temperature  $0^{\circ}$  C to  $70^{\circ}$  C Storage Temperature  $-65^{\circ}$  C to  $150^{\circ}$  C

Equivalent chassis include the TM 990/520, /530, /510A, and /520A.

1-1

FIGURE 1-1. TM 990/310 48-1/0 MODULE

1-2

Physical Characteristics:

| Width:            | 28 cm (11 inches)           |

|-------------------|-----------------------------|

| Height:           | 19 cm (7.5 inches)          |

| Thickness:        | 0.16 cm (0.062 inch)        |

| Component height: | 12.7 mm (0.50 inch) maximum |

Edge Triggered Interrupt Inputs:

Positive-going threshold voltage: 1.9 V max. Negative-going threshold voltage: 0.5 V min. Hysteresis: 0.4 V max. Allowed voltage range: -0.3 V to 7.0 V Input current: -2.72 mA @ V<sub>IN</sub> = 0.4V -1.22 mA @ V<sub>IN</sub> = 2.7 V

Programmed Inputs:

High-level input voltage: 2.0 V, minimum Low-level input voltage: 0.8 V, maximum Allowed voltage range: -0.3 V to 7 V Input current: - 1.01 mA maximum @ 0.4 V

Programmed Outputs:

```

High-level output voltage: 2.4 V, minimum @ -300 uA

2.0 V, minimum @ -460 uA

Low-level output voltage: 0.56 V, maximum @ 2.3 mA

Maximum user current sink: 2.2 mA

```

#### 1.3 APPLICABLE DOCUMENTS

- TMS 9900 Microprocessor Data Manual

- TMS 9901 Programmable Systems Interface Data Manual (provided in Appendix E).

- TM 990/401 TIBUG Monitor Listing

- TM 990/100MA User's Manual

- Model 990 Computer, TMS 9900 Microprocessor Assembly Language Programmer's Guide (P/N 943441-9701)

- TM 990/507 Cable and 5MT System User's Guide

#### SECTION 2

#### INSTALLATION AND OPERATION

## 2.1 GENERAL

This section describes:

- Equipment required for TM 990/310 board operation.

- Switch array S1 on the TM 990/310 board used to select TMS 9901 CRU base address.

- Jumper platforms U1 and U6 used to select interrupt level when an interrupt occurs at one of the three TMS 9901's on the board.

- Installation of the board into a microcomputer system.

- Programs to check out board operation.

It is presumed that the user is familiar with the TMS 9901 as well as the hardware and programming aspects of the host microcomputer. This data is available in the following manuals:

- TMS 990/1XX Microcomputer User's Guide

- TMS 9901 Programmable Systems Interface Data Manual

A copy of the latter manual can be found in Appendix D.

#### 2.2 REQUIRED EQUIPMENT

To use the TM 990/310 effectively, the user must also supply the following equipment:

• Power Supplies:

+5 V <u>+</u>5%, 3 A +12 V <u>+</u>5%, 0.5 A -12 V +5%, 0.5 A

- Host Microcomputer: One of the TM 990/1XX series; in the following examples, the TM 990/100MA-1.

- Chassis: TM 990/510 card cage (or equivalent)

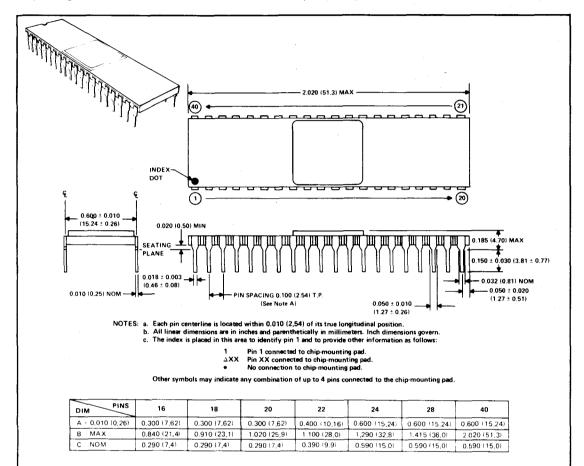

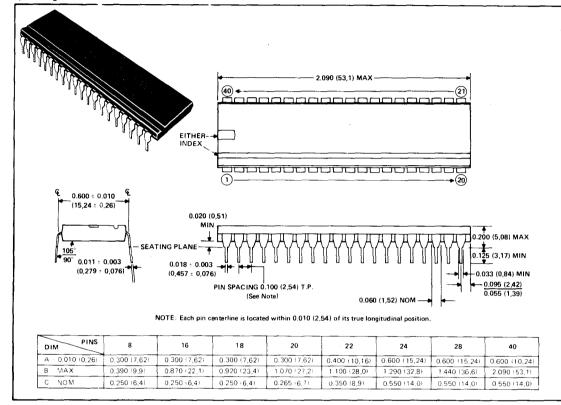

- Edge Connectors: Three 40-pin (0.1 inch centers) PCB edge connectors. Will mate to TI H421111-20 (wire-wrap), Viking 3VH20/1JN5 (solder), 3M 3464-0001 (ribbon cable), or equivalent. A three-connector kit TM 990/521, is available from Texas Instruments.

- Terminal Device: Any RS-232-C device operable at a baud rate of 110, 300, 1200, or 9600 baud or an ASR33 Teletype modified for 20 mA current loop operation.

#### 2.3 BOARD SWITCHES, JUMPERS, CONNECTORS

2.3.1 CRU Address Selection and Switch Array S1

The three TMS 9901's on the TM 990/310 board are addressed through the system's address bus when a CRU instruction is executed (LDCR, STCR, TB, SBO, and SBZ). Before execution, a CRU software base address is placed into register 12; the resulting bits 3 to 14 (4 to 14 on the TM 990/180M) contain the CRU hardware base address as further explained in your microcomputer user's guide.

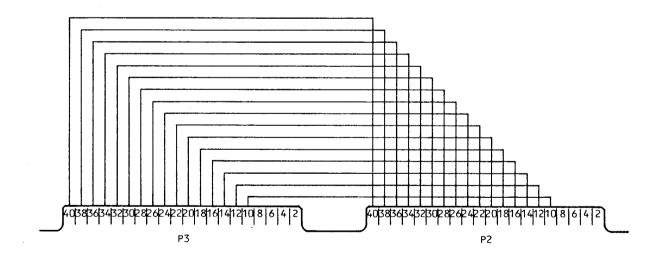

Switch S1 allows you to select the CRU hardware base address in increments of  $CO_{16}$  that you can use to address a particular TMS 9901. Figure 2-1 shows the switch S1 settings and the resulting CRU hardware (B) and software base addresses. The resulting CRU base address is the one that addresses the no. 1 TMS 9901 (accessed through edge connector J2). As shown at the bottom of Figure 2-1, the other TMS 9901's are addressed using the base address plus a designated displacement.

The first 32 CRU bits addressed are bits 0 to 31 (0 to  $1F_{16}$ ) at the TMS 9901 which select:

- Interrupt or clock mode (bit 0 select)

- Interrupt mask or clock interval (bits 1 to 15)

- Data output or input (bits 16 to 31)

Further data is available in the TMS 9901 data manual (Appendix E).

As shown in Figure 2-1, two of the next 16 bits addressed will reset edge-triggered interrupts (INT5- and INT6-) that have been triggered at the TMS 9901. INT5- is a negative edge-triggered interrupt, and INT6- a positive edge-triggered interrupt. Edge-triggered interrupts will remain active until reset by an LDCR instruction of prescribed address (e.g., a pulse at CRU base address B + 0024<sub>16</sub> resets interrupt 5 at no. 1 TMS 9901 and B + 0025<sub>16</sub> resets interrupt 6 at the same TMS 9901).

As shown in Figure 2-1, the next 16 bits can be read (echoed) in order to test a bit pattern output from the TMS 9901. The bit pattern output is stored in a buffer that can be read (using the STCR instruction) and compared to the bit pattern sent. For example, the following code will read the value output at no. 1 TMS 9901 location at CRU software base address  $0200_{16}$  (as selected at switch S1):

| LI   | R12, >0260 | Set CRU address            |

|------|------------|----------------------------|

| STCR | R1,0       | Store 16-bits output in R1 |

2.3.2 Interrupt Level Selection on Jumper Plugs U1 and U6

When any interrupt is recognized at a TMS 9901 on the TM 990/310, a signal (INTREQ-) is issued from the TMS 9901 on the I/O board to the backplane and then to the TMS 9901 on the microcomputer board. There it is monitored for priority, and, if enabled, a signal is issued to the microprocessor to obtain Workspace Pointer (WP) and Program Counter (PC) values from interrupt traps in lower memory.

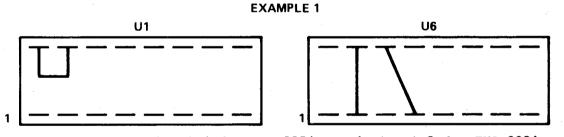

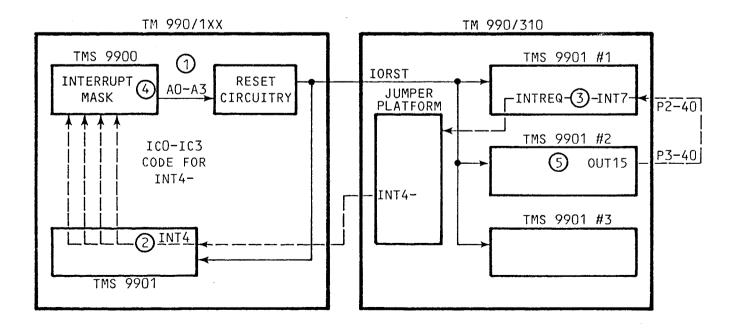

The user can select the interrupt level or levels (up to 3 are possible) by wiring jumpers at platforms U1 and U6, shown in Figure 1-1 in the lower left corner of the board. Note that each TMS 9901 may be jumpered to unique backplane priority levels, or all three may be jumpered to the same backplane priority level (the TM 990/310 is initially jumpered for all three TMS 9901's dedicated to backplane priority interrupt 4).

| S1 S<br>1 |     | I SETT | INGS | EQUALS<br>BINARY | TM 310 BOARD<br>CRU HARDWARE (B)<br>BASE ADDRESS<br>(BASE 16) | CORRESPONDING<br>REGISTER<br>12 CONTENTS<br>(CRU SOFTWARE<br>BASE ADDRESS)<br>(BASE 16) |

|-----------|-----|--------|------|------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| ON        | ON  | ON     | ON   | 0                | 0100                                                          | 0200                                                                                    |

| ON        | ON. | ON     | OFF  | 1                | 01C0                                                          | 0380                                                                                    |

| ON        | ON  | OFF    | ON   | 2                | 0280                                                          | 0500                                                                                    |

| ON        | ON  | OFF    | OFF  | 3                | 0340                                                          | 0680                                                                                    |

| ON        | OFF | ON     | ON   | 4                | 0400                                                          | 0800                                                                                    |

| ON        | OFF | ON     | OFF  | 5                | 04C0                                                          | 0980                                                                                    |

| ON        | OFF | OFF    | ON   | 6                | 0580                                                          | 0B00                                                                                    |

| ON        | OFF | OFF    | OFF  | 7                | 0640                                                          | 0C80                                                                                    |

| OFF       | ON  | ON     | ON   | 8                | 0700                                                          | 0E00                                                                                    |

| OFF       | ON  | ON     | OFF  | 9                | 07C0                                                          | 0F80                                                                                    |

| OFF       | ON  | OFF    | ON   | А                | 0880                                                          | 1100                                                                                    |

| OFF       | ON  | OFF    | OFF  | в                | 0940                                                          | 1280                                                                                    |

| OFF       | OFF | ON     | ON   | С                | 0A00                                                          | 1400                                                                                    |

| OFF       | OFF | ON     | OFF  | D                | 0AC0                                                          | 1580                                                                                    |

| OFF       | OFF | OFF    | ON   | E                | NOT USED                                                      | NOT USED                                                                                |

| OFF       | OFF | OFF    | OFF  | F                | NOT USED                                                      | NOT USED                                                                                |

|           |     |        |      |                  |                                                               |                                                                                         |

CORRESPONDING

| DEVICE                    | ADDRESSED USING<br>CRU HARDWARE<br>BASE ADDRESS (B)<br>AND DISPLACEMENT | CORRESPONDING<br>CRU SOFTWARE<br>BASE ADDRESS<br>R12 CONTENTS (BASE 16) | NUMBER<br>OF BITS |

|---------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------|

| No. 1 TMS 9901 (P2)       | *B + 0000 to B + 001F                                                   | R12 + 0000 to R12 + 003E                                                | 32                |

| Edge-triggered INT5 reset | B + 0024                                                                | R12 + 0048                                                              | 1                 |

| Edge-triggered INT6 reset | B + 0025                                                                | R12 + 004A                                                              | 1                 |

| Echo                      | B + 0030 to B + 003F                                                    | R12 + 0060 to R12 + 007E                                                | 16                |

| No. 2 TMS 9901 (P3)       | B + 0040 to B + 005F                                                    | R12 + 0080 to R12 + 009E                                                | 32                |

| Edge-triggered INT5 reset | B + 0065                                                                | R12 + 00CA                                                              | 1                 |

| Edge-triggered INT6 reset | B + 0066                                                                | R12 + 00CC                                                              | 1                 |

| Echo                      | B + 0070 to B + 007F                                                    | R12 + 00E0 to R12 + 00FF                                                | 16                |

| No. 3 TMS 9901 (P4)       | B + 0080 to B + 009F                                                    | R12 + 0100 to R12 + 013F                                                | 32                |

| Edge-triggered INT5 reset | B + 00A4                                                                | R12 + 0148                                                              | 2                 |

| Edge-triggered INT6 reset | B + 00A5                                                                | R12 + 014A                                                              | 1                 |

| Echo                      | B + 00B0 to B + 00BF                                                    | R12 + 0160 to R12 + 017E                                                | 16                |

\*B is the hardware base address computed in the table in the middle of this figure.

FIGURE 2-1. USE OF SWITCH S1 TO SET CRU ADDRESS MAP

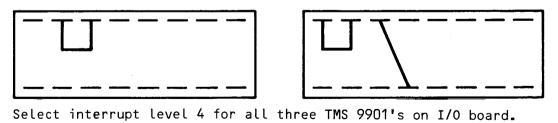

Select interrupt level 4 for TMS 9901 no. 1; level 2 for TMS 9901 no. 2 and 3.

EXAMPLE 2

NOTE: TM 990/310 is factory wired to priority 4 for all three TMS 9901's.

FIGURE 2-2. INTERRUPT PRIORITY JUMPER WIRING AT U1 AND U6

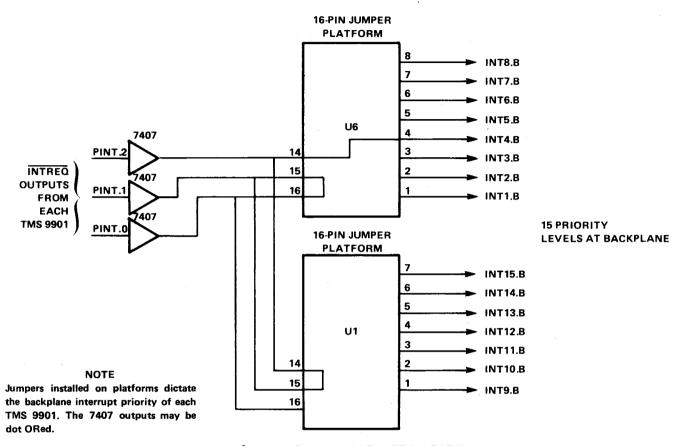

As shown in Figure 2-2, a wire is attached to pins 16, 15, and 14 to respectively select the interrupt level sent by the no. 1, and no. 2, and no. 3 TMS 9901's on the I/O board. Note that pins 14, 15, and 16 of U1 are connected to pins 14, 15, and 16 of U6. Thus the configuration in the second example of Figure 2-2 will cause interrupts at all three I/O board TMS 9901's to go to INT4 at the TMS 9901 on the microcomputer board. This is the configuration as wired at the factory.

As explained in the microcomputer user's guide, vector addresses have been programmed into TIBUG EPROM for interrupt traps 3 and 4 on the TM 990/100MA. The user can program these RAM locations for use as an interrupt handler as described in the microcomputer user's guide. On the TM 990/180M, vector addresses have been programmed into EPROM for interrupts 1 and 2.

#### 2.3.3 Edge Connectors P1, P2, P3, and P4

PININUMPER SIGNATURE

Edge connectors P2, P3, and P4 interface directly to the I/O board TMS 9901's through onboard series resistors. TMS 9901 signatures at these connectors are listed in Table 2-1.

TABLE 2-1. EDGE CONNECTOR (P2, P3, P4) PIN ASSIGNMENTS

| PIN NUMBER         | SIGNATURE      |                 |    |                                               |

|--------------------|----------------|-----------------|----|-----------------------------------------------|

| P2, P3, P4 - 20    | PO             | <b>\</b>        |    |                                               |

| 22                 | P1             | 1               |    |                                               |

| 14                 | P2             |                 |    | NOTES                                         |

| 16                 | P3             |                 |    | 10166                                         |

| 18                 | P4             |                 |    |                                               |

| 10                 | P5             | 1               | 1. | Connector P2 connects to the lowest addressed |

| 12                 | P6             | 1               |    | TMS 9901, P3 connects to the next addressed   |

| 24                 | INT15/P7       | TMS 9901        |    | TMMS 9901, and P4 connects to the highest     |

| 26                 | INT14/P8       | / I/O Signals   |    | addressed TMS 9901.                           |

| 28                 | INT13/P9       | 1               |    |                                               |

| 30                 | INT12/P10      |                 | ~  |                                               |

| 32                 | INT11/P11      |                 | 2. | If you want to make your own cable, be aware  |

| 34                 | INT10/P12      | 1               |    | that the connector plugs of various vendors,  |

| 36                 | INT9/P13       |                 |    | including TI, do not necessarily use the      |

| 38                 | INT8/P14       | 1               |    | numbering schemes on the board edge           |

| 40                 | INT7/P15       | /               |    | connector. ALWAYS refer to the board edge     |

| 6                  | Negative edge  | -triggered INT5 |    | <b>U</b>                                      |

| 8                  | Positive edge- | triggered INT6  |    | when wiring a connector.                      |

| 1                  | +12V           |                 |    |                                               |

| 2                  | -12V           |                 |    |                                               |

| 3                  | +5V            |                 |    |                                               |

| 4                  | Spare          |                 |    |                                               |

| All Remaining Pins | Ground         |                 |    |                                               |

|                    |                |                 |    |                                               |

TMS 9901 pins P0 to P5 act as data out or data in lines, depending on how the TMS 9901 is programmed (input or output mode).

If programmed to the interrupt mode, an active low signal to even-numbered pins 24 to 40 will cause activation of signal INTREQ- to the TMS 9901 on the microcomputer board. The level to the microcomputer board is selected by the jumpers at U1 and U6 as described in paragraph 2.3.2.

A negative-going signal to pin 6 or positive-going signal to pin 8 will also cause INTREQ- to be active.

The voltage at pins 1, 2, and 3 goes through 2.2 ohm, 0.5W series limiting resistors. Power in excess of this rating could destroy the resistors; thus caution should be taken to prevent excess current (250 mA maximum recommended).

Table 2-2 is a list of the signals at connector P1 which interfaces to the backplane of the TM 990/510 chassis.

TABLE 2-2. TM 990/310 CHASSIS INTERFACE CONNECTOR (P1) SIGNAL ASSIGNMENTS

| P1<br>PIN | SIGNAL    | P1<br>PIN | SIGNAL   |

|-----------|-----------|-----------|----------|

|           |           | <br>      |          |

| 57        | AO.B      | 13        | INT2.B-  |

| 58        | A1.B      | 15        | INT3.B-  |

| 59        | A2.B      | 18        | INT4.B-  |

| 60        | A3.B      | 10        | INT5.B-  |

| 61        | -         |           | INT6.B-  |

|           | A4.B      | 20<br>6   | INT7.B-  |

| 62        | A5.B      |           |          |

| 63        | A6.B      | 5<br>8    | INT8.B-  |

| 64        | A7.B      |           | INT9.B-  |

| 65        | A8.B      | 7         | INT10.B- |

| 66        | A9.B      | 10        | INT11.B- |

| 67        | A10.B     | 9         | INT12.B- |

| 68        | A11.B     | 12        | INT13.B- |

| 69        | A12.B     | 11        | INT14.B- |

| 70        | A13.B     | 14        | INT15.B- |

| 71        | A14.B     | 3         | +5V      |

| 72        | A15.B     | 4         | +5V      |

| 24        | ø3.B-     | 97        | +5V      |

| 87        | CRUCLK.B- | 98        | +5V      |

| 30        | CRUOUT.B  | 1         | GND      |

| 29        | CRUIN.B   | 2         | GND      |

| 88        | IORST.B-  | 99        | GND      |

| 16        | INT 1.B-  | 100       | GND      |

#### 2.4 INSTALLATION

The following procedure is for a TM 990/310 module used with a TM 990/100MA-1 CPU (with TIBUG installed on EPROM):

- a. Attach jumper J1 to the P1-18 position on the TM 990/100MA board. This provides interrupt level 4 from the backplane to the TM 990/310.

- b. Wire the voltages into the terminal strip in the chassis, switch on the power supplies, and check the voltages. Switch off power. Set all switches on S1, the dual in line package (DIP) on the TM 990/310 board, to the ON positions (CRU software base address of 020016).

- c. Install the TM 990/100MA-1 and TM 990/310 circuit boards in the chassis. Attach the terminal connector to J2 on the TM 990/100MA-1. Note that the TM 990/310 board has only one ejector in order to accomodate three external connectors.

- d. Power up the terminal device and switch on the power supplies.

- e. Actuate the RESET switch on the TM 990/100MA-1 board and press the letter A key or a carriage return (CR) on the terminal device. TIBUG, the debug monitor program, will output an initialization message.

#### 2.5 BOARD CHECKOUT

Software routines that can be loaded and executed by the user, using the TIBUG monitor, are provided in Section 5.

#### THEORY OF OPERATION

#### 3.1 GENERAL

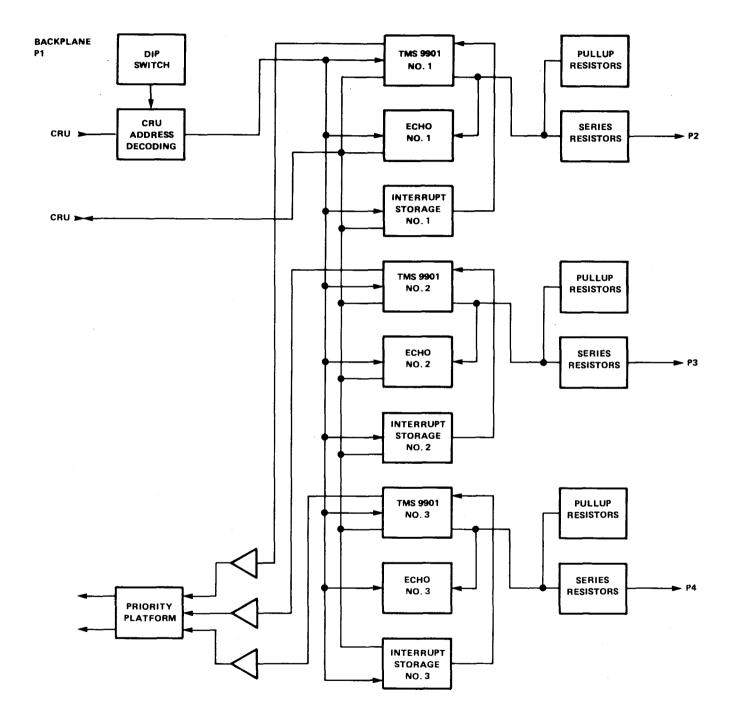

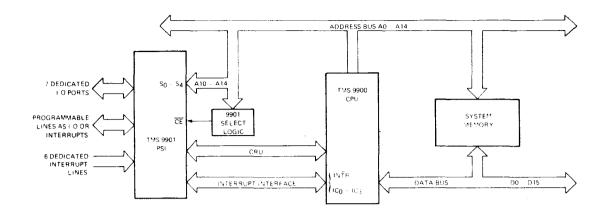

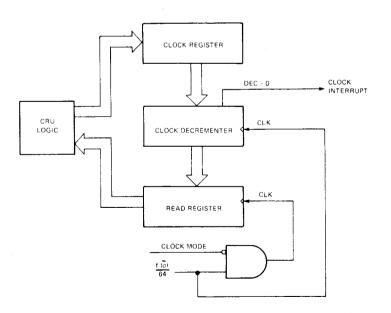

This section describes the theory of operation for the TM 990/310 I/O board. The block diagram in Figure 3-1 defines the basic blocks that comprise the TM 990/310.

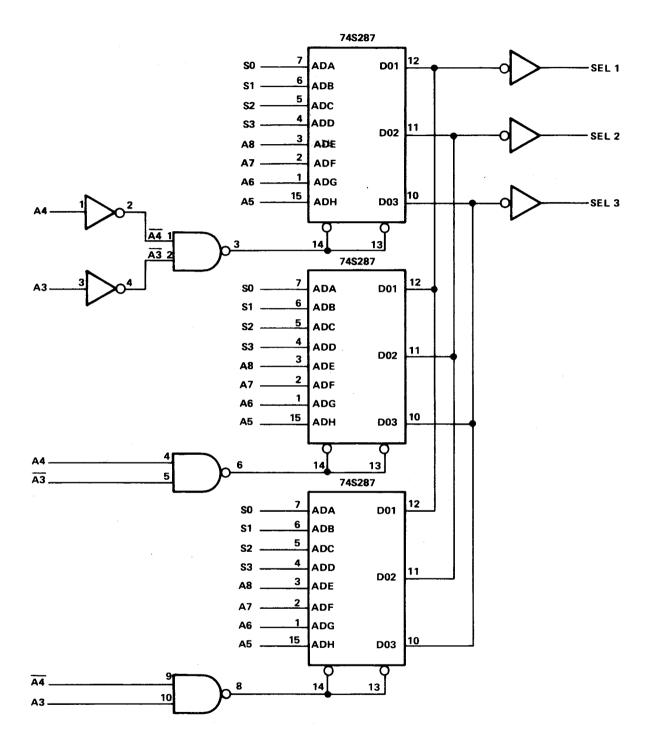

#### 3.2 CRU ADDRESS DECODING

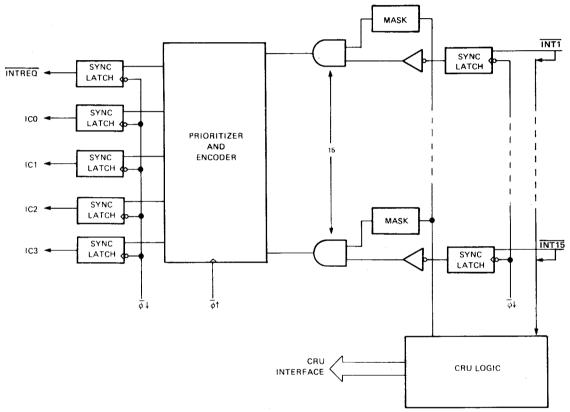

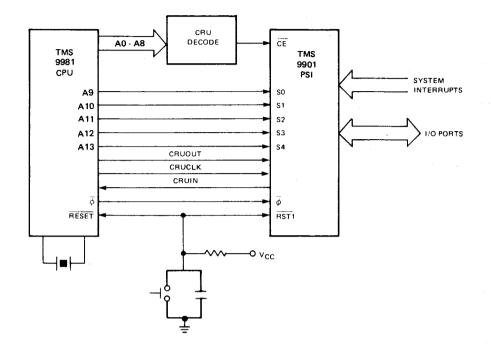

Figure 3-2 is a schematic of CRU address decoding. The following terms are generated by the CRU address coding

MUXENO-MUXEN1-MUXEN2-Echo multiplexer enables MUXEN3-MUXEN4-MUXEN5-9901SEL.0-9901SEL.1-TMS 9901 enables 990 1SEL.2-IR.00-IR.01-IR.02-Buffered interrupt resets IR.03-IR.04-IR.05-

These terms are combinational functions of the address lines, and vary with the settings of switch S1. Three 74S287's generate the terms SEL1, SEL2, and SEL3 which provide enable inputs to the combinational logic that generates the device enables.

The address lines to the 74S287's are provided by the four switch outputs and backplane address lines A5 through A8. Individual 74S287's are enabled, depending on the state of address lines A3 and A4. Since each switch setting represents 192 ( $CO_{16}$ ) CRU addresses, the 74S287's are programmed to generate three outputs (SEL1, SEL2, SEL3) which individually enable 64 different CRU addresses. Each group of 64 encompasses one TMS 9901, the I/O echo and interrupt resets.

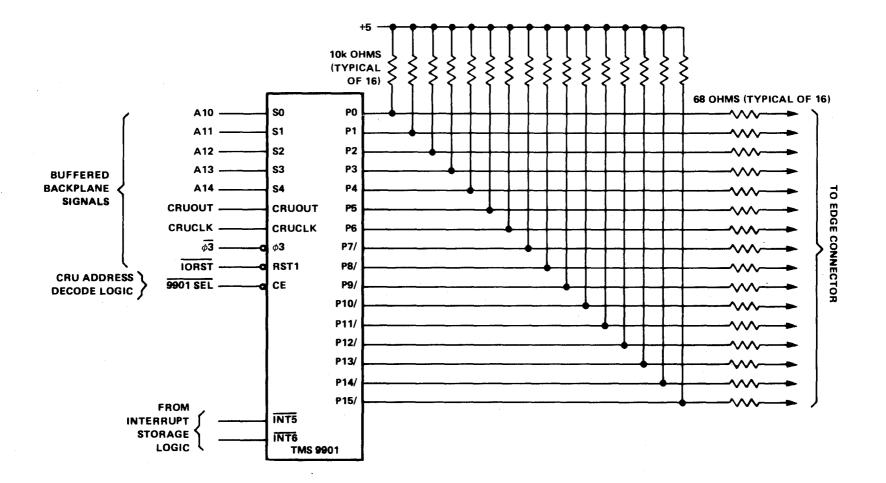

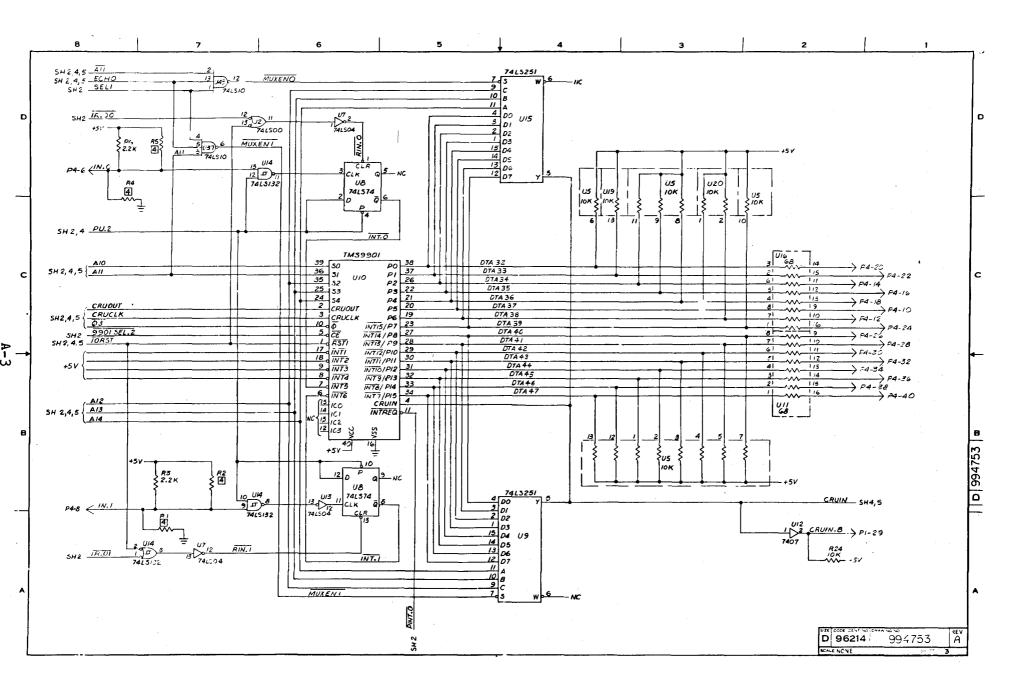

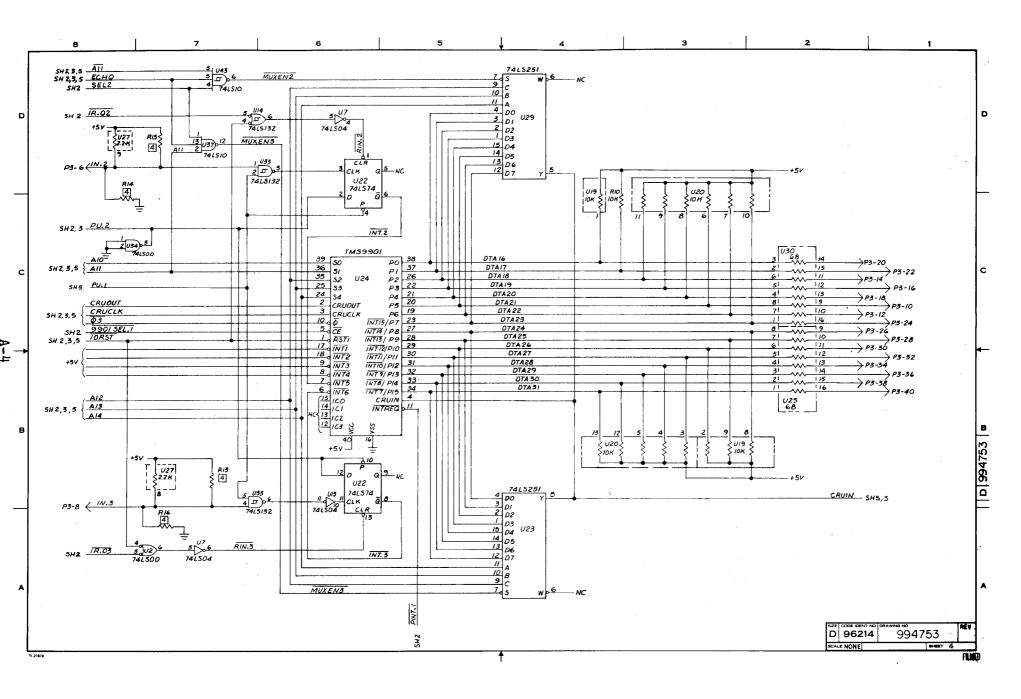

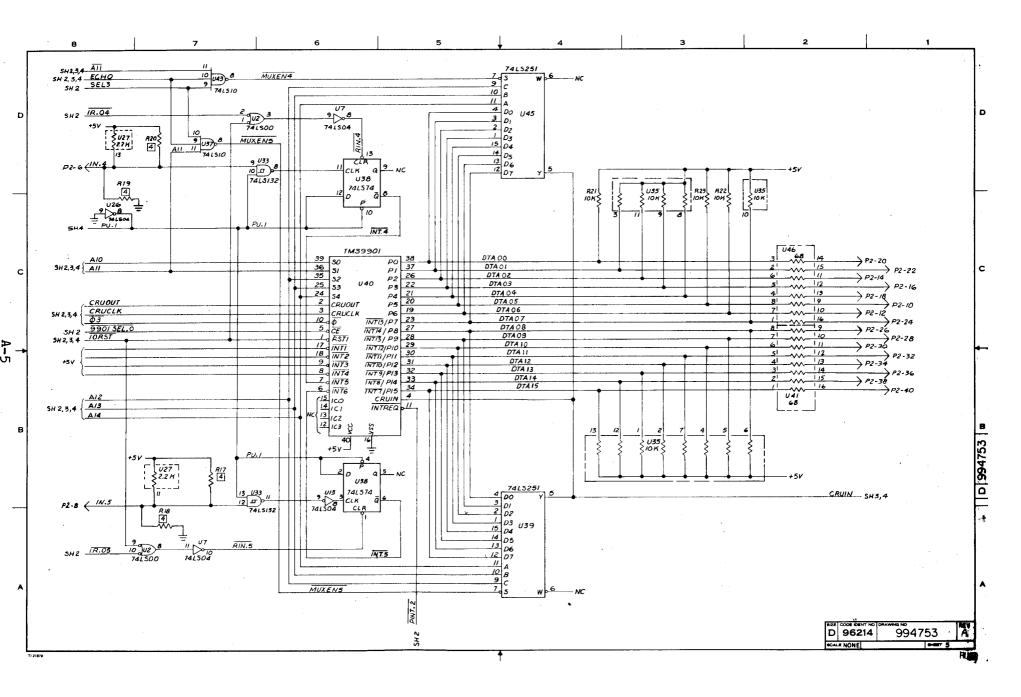

#### 3.3 TMS 9901 LOGIC

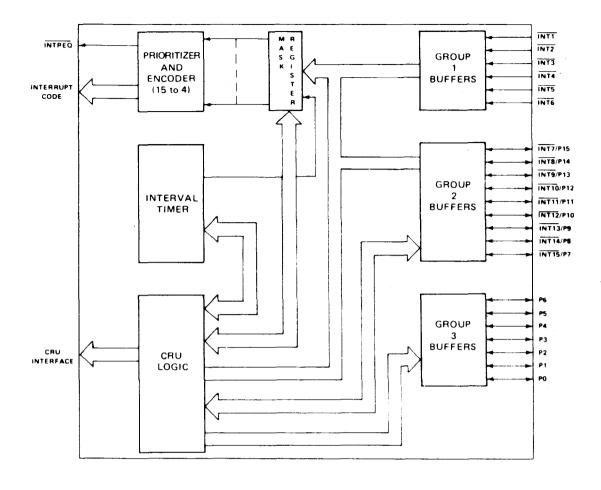

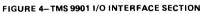

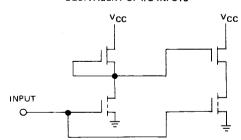

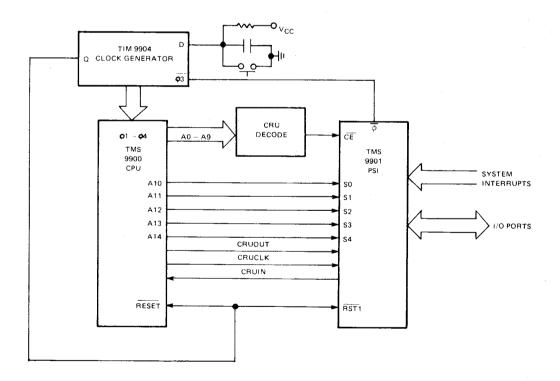

The three TMS 9901's are enabled by CRU address decoding logic outputs. As shown in Figure 3-3, the select inputs, S0 through S4, are connected to backplane address lines A10, A11, A12, A13, and A14. These TMS 9901 inputs select the individual data bits and control functions within the TMS 9901.

3-1

FIGURE 3-1. TM 990/310, 48-BIT INPUT/OUTPUT BOARD SIMPLIFIED BLOCK DIAGRAM

FIGURE 3-2. CRU ADDRESS DECODING

FIGURE 3-3. TMS 9901 LOGIC (TYPICAL OF 3)

3-4

The CRU interface signals CRUOUT, CRUCLK, and CRUIN control input and output between the TMS 9901 and the CRU. The INTEQ- output of each TMS 9901 is an input to the 7407 open collector buffers. The backplane reset signal is connected to each TMS 9901 reset input, and the backplane phase-1 clock is connected to each TMS 9901 clock input.

Each of the 16 I/O bits of each TMS 9901 is connected to a 10K ohm pullup resistor and an echo multiplexer input as well as a 68-ohm series resistor connected to the appropriate pin of one of the three board edge connectors. The INT5- and INT6- inputs of each TMS 9901 are connected to latched interrupt lines.

It should be noted that since the TMS 9901 interfaces to the serial CRU, the TMS 9901 lines, when outputting data, will assume their output state one bit at a time.

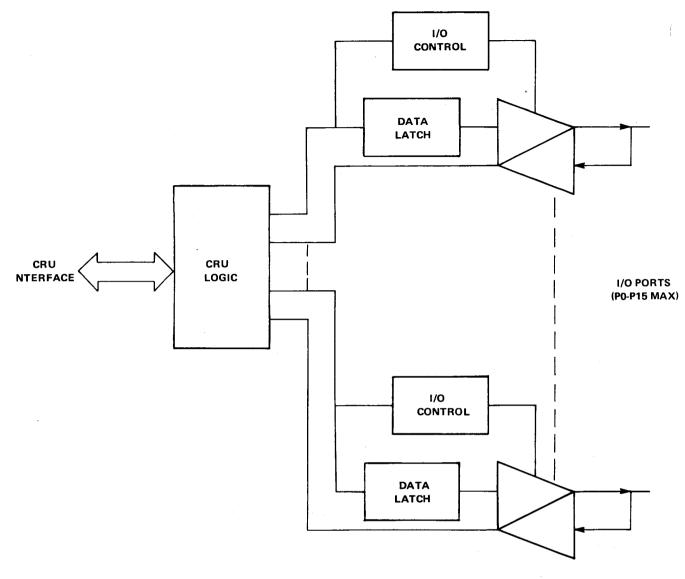

#### 3.4 DATA ECHO LOGIC

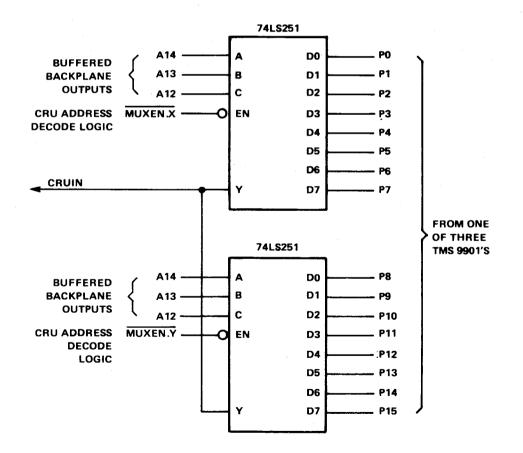

The data echo logic shown in Figure 3-4 is implemented with six 74LS251 multiplexers. Each multiplexer is enabled by a CRU address decoding output. The appropriate data bit is switched through the multiplexer onto the CRUIN line by the state of backplane address bits A14, A13, and A12.

## FIGURE 3-4. ECHO LOGIC (TYPICAL OF 3 CIRCUITS)

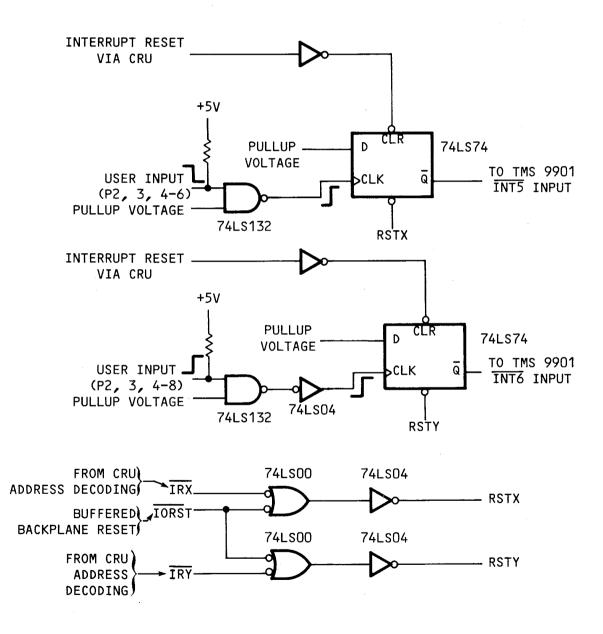

#### 3.5 INTERRUPT BUFFER LOGIC

The interrupt buffers are composed of 74LS74 D flip-flops as shown in Figure 3-5. Each interrupt input from the appropriate edge connector is pulse shaped through 74LS132 Schmitt trigger circuits. For the three negative-edge INT5-inputs, the 74LS132 output provides the clock input to the 74LS74. The D input is tied high and the CLEAR input is the logical NOR of the appropriate software reset bit and the backplane reset signal. The 74LS74 clock inputs for the positive-edge triggered INT6- interrupts are 74LS04 ouputs. The 74LS04 input is provided by the Schmitt trigger output. Each TMS 9901 INT5- and INT6- input is provided by the false 74LS74 outputs.

#### FIGURE 3-5. INTERRPUT STORAGE LOGIC

#### 3.6 INTERRUPT PRIORITY LOGIC

The three 7407 open collector interrupt outputs are connected to two 16-pin platforms as shown in Figure 3-6. Wires installed on these platforms determine the backplane priority of the three TMS 9901 interrupts. All three TMS 9901 interrupts are initially jumpered to interrupt priority level 4.

FIGURE 3-6. INTERRUPT PRIORITY LOGIC

#### 3.7 HARDWARE INTERFACE

The TM 990/310 user interface is implemented through three identical 40-pin edge connectors. (See Section 1.2 for signal characteristics.) Each of these connectors provide data I/O, interrupt inputs, and power (Table 2-1 lists these functions).

#### 3.7.1 TMS 9901 I/O Lines

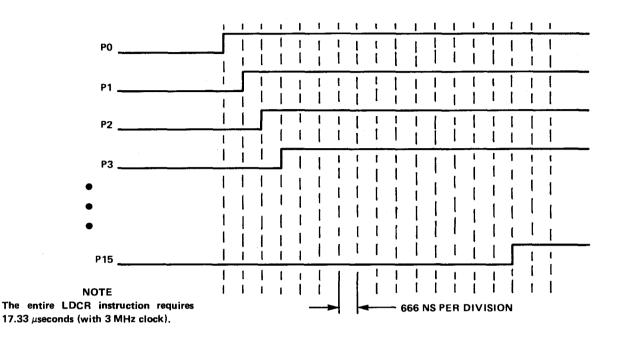

Sixteen TMS 9901 lines are individually programmable as inputs or outputs. Nine of these lines (INT15/P7 to INT7/P15) may be programmed as either unbuffered, logic-zero-activated interrupts or as inputs or outputs. A TMS 9901 I/O line, when in output mode, buffers the data output from memory and this data remains stable until changed. Since the TMS 9901 interfaces through the serial CRU, the I/O lines programmed as outputs assume their programmed state in serial fashion if data is output via a LDCR instruction that addresses successive bits.

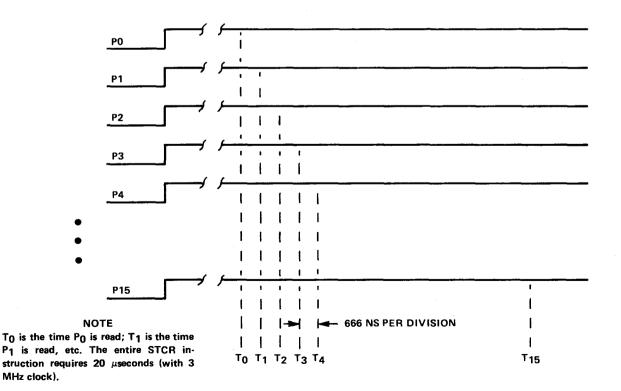

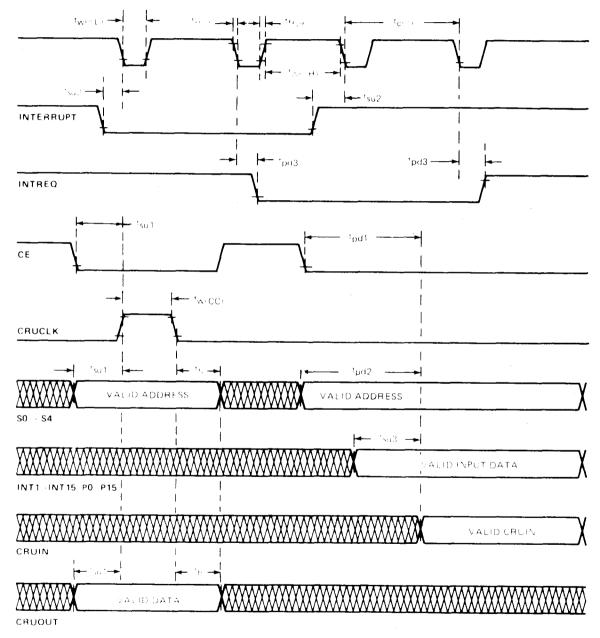

The timing diagram in Figure 3-7 illustrates the timing for an LDCR utilizing all 16 I/O lines as outputs. Data input via the TMS 9901 I/O lines is accepted serially, one bit at a time; therefore, since there is no input data storage, the system timing must ensure that the input data remains stable until the software has read the data via a TB or STCR instruction. Figure 3-8 illustrates the timing for a 16-bit STCR operation.

FIGURE 3-8. TM 990/310 INPUT TIMING FOR STCR READING 16 BITS OF ONE'S

#### 3.7.2 Edge-Triggered Interrupts

There is one positive edge-triggered (connector pin 8) interrupt and one negative-edge triggered (connector pin 6) interrupt. These interrupt lines pass through Schmitt trigger circuits.

3.7.3 Power Outlets at Connectors

5V, 12V, and -12~V are available at the connectors. Each voltage is in series with a 2.2 ohm, 0.5 watt resistor to limit maximum current drawn from these lines.

Excessive current drawn from any of these supplies will cause a significant voltage drop across the resistor or, if large enough, will destroy the resistor. If the user wishes to utilize current from these voltages, the required current must be added to the specified value for the appropriate backplane power supply. User circuits must allow for the resulting voltage drop across these resistors.

#### SECTION 4

#### APPLICATIONS

#### 4.1 GENERAL

For the user requiring high ouput power drive or input/output optical isolation, the TM 990/512 prototyping board may be utilized for the required circuitry.

## 4.2 OUTPUT SIGNAL CONDITIONING, MEDIUM POWER

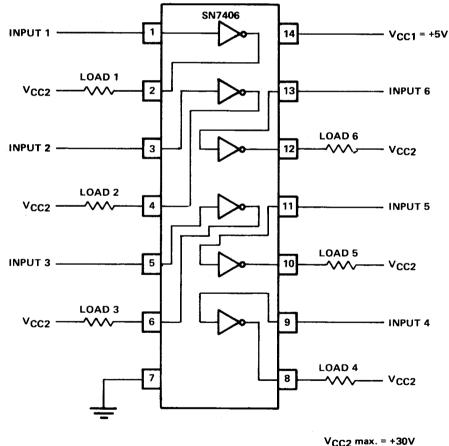

This is shown in Figure 4-1. For TM 990/310 outputs requiring current drive greater than 2.6 mA but less than 40 mA, the SN7406 hex open collector inverting buffer is recommended. Note that this device will withstand a maximum pullup voltage of 30 volts. A typical application of the SN7406 is driving LED's.

To condition TM 990/310 data bits 0 through 5 as buffered outputs, the circuitry shown in Figure 4-1 is recommended.

I load max. = 40 mA

FIGURE 4-1. MEDIUM-POWER OUTPUT SIGNAL CONDITIONING CIRCUIT

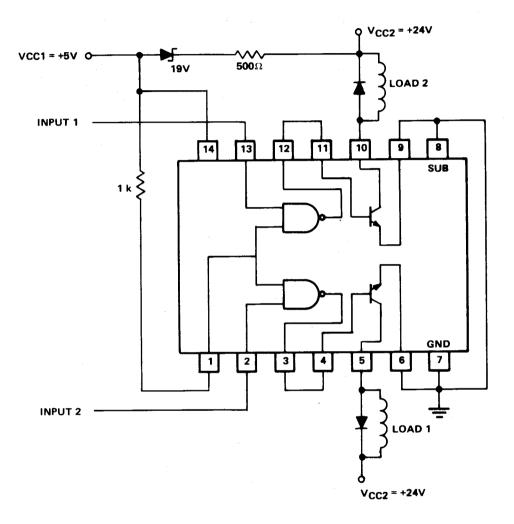

For TM 990/310 outputs requiring more current drive than supplied by the SN7406 but less than 300 mA, the SN75460 open collector power buffer is recommended. The device will withstand a pullup voltage of 30 volts.

To drive 24-volt relays with TM 990/310 data bits 0 and 1, the circuitry shown in Figure 4-2 is recommended. The 19 V Zenier diode prevents damage to the SN75460 if the 5V supply is inactive while  $V_{\rm cc2}$  is active.

FIGURE 4-2. HIGH POWER OUTPUT SIGNAL CONDITIONING CIRCUIT

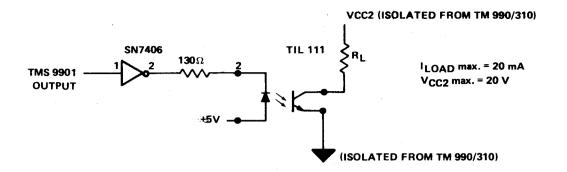

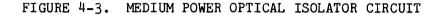

#### 4.4 OUTPUT SIGNAL CONDITIONING, OPTICAL ISOLATION

For the user who requires TM 990/310 output isolation, the TIL 111 optical coupler is recommended for current output drive up to 20 mA. If more current drive is required, the optical coupler output must drive a buffer circuit such as the SN75460 to provide the current drive. It should be noted that the optical coupler output breakdown voltage is 30 volts.

Figure 4-3 illustrates a 20 mA optically isolated circuit. To condition TM 990/310 data bit 0 as an optically-coupled 300-mA output, the circuitry illustrated in Figure 4-4 is recommended.

ILOAD max. = 300 mA V<sub>CC2</sub> max. = 40 V ILOAD max. = 20 mA

# FIGURE 4-4. HIGH POWER OPTICAL ISOLATOR CIRCUIT

#### 4.5 LOGIC TESTING

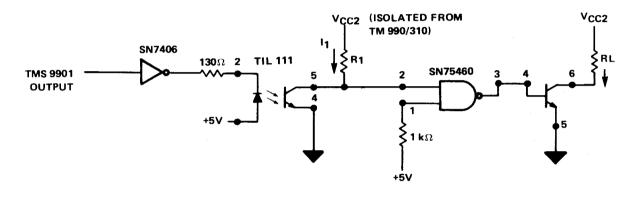

The TM 990/310 provides an ideal method to check circuit boards and other logic networks. The diagram in Figure 4-5 illustrates a circuit board tester with the capability to generate and check a total of 96 bits. For example, the tester could be programmed to output patterns on 80 pins and check resulting signals on 16 pins. A typical software sequence would be as follows:

- a. Set all 96 bits (all three TMS 9901's) to input mode (set bit 15, RST2, to zero at each TMS 9901).

- b. Output a test pattern to the selected 80 bits (outputting data to a bit automatically switches the bit to output mode).

- c. Echo the output data, and verify that no output bits are shorted on the board being tested.

- d. Input the resulting output signals from the board being tested, and compare for valid operation.

- e. Repeat steps b, c, and d for as many test patterns as required.

Note that this test configuration will provide 2.2 mA per bit to the board under test. If more current drive is required, high current amplifiers should be implemented on a TM 990/512 prototyping board.

FIGURE 4-5. TYPICAL TESTING CONFIGURATION

## 4.6 5MT INPUT/OUTPUT SYSTEM

For industrial automation applications involving programmable control of ac and dc switches, solenoid valves, or pilot lights, the TM 990/310 will interface to 5MT I/O modules installed on a mounting baseplate. The 5MT system features the following characteristics:

- 3.8 kVdc optical coupler isolator

- LED indicator lights

- Plug-in modules

- Terminal strip on mounting baseplate for field-wired devices

- Designated to meet UL50B spacing requirements

- Meets NEMA ICS2-230 noise immunity standard for industrial controls and MIL-STD-461A, conducted and radiated susceptibility

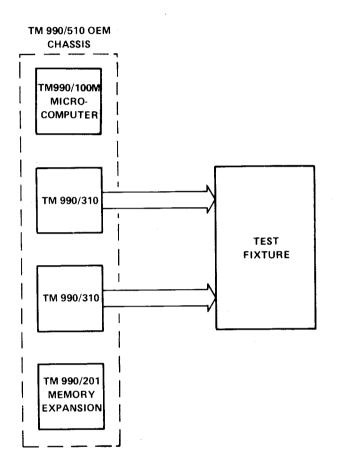

- Module-to-module isolation

The 5MT uses a baseplate which may contain up to 16 plug-in modules. Connection between the TM 990/310 and 5MT is by a TM 990/507 cable as shown in Figure 4-6. Further information is available in the TM 990/507 and 5MT System User's Guide.

FIGURE 4-6. 5MT CIRCUITRY

- 5MT14-30CL DC Output Module enables the TM 990/310 to control high power dc outputs.

- 5MT12-40AL AC Output Module enables the TM 990/310 to control high power ac outputs.

- 5MT13-D03L DC Input Module converts high voltage dc inputs to voltage inputs compatible with the TM 990/310.

- 5MT11-A05L AC Input Module converts high voltage ac inputs to voltage inputs compatible with the TM 990/310.

The following operational characteristics must be considered when using the 5MT module:

a. The reset signal (from the logical OR of power-up reset, the RESET switch on the microcomputer board, or the RSET external instruction) will force all 48 I/O bits to the high state; therefore, all 5MT outputs will be initially active. The user who finds this feature undesirable may use an output-data-clear instruction in the reset interrupt subroutine. This would require the user to modify TIBUG, the debug monitor, or replace the TIBUG entirely. Table 4-1 indicates the requirements for the cable between the TM 990/310 and the 5MT baseplate. Further information on the 5MT series may be obtained from:

Texas Instruments Incorporated Industrial Controls 34 Forest Attleboro, MA. 02703

# TABLE 4-1. 5MT CONNECTOR WIRING

| SIGNAL          |    | 5MT D CONNECTOR | TM 990/310 EDGE CONNECTOR |

|-----------------|----|-----------------|---------------------------|

| Data Bit/Module | 5  | 1               | 10                        |

| Data Bit/Module | 4  | 2               | 18                        |

| Data Bit/Module | 2  | 3               | 14                        |

| Data Bit/Module | 0  | 4               | 20                        |

| Data Bit/Module | 7  | 5               | 24                        |

| Data Bit/Module | 9  | 6               | 28                        |

| Data Bit/Module | 11 | 7               | 32                        |

| Data Bit/Module | 13 | 8               | 36                        |

| Data Bit/Module | 15 | 9               | 40                        |

| Ground/Module   | 2  | 10              | 13                        |

| Ground/Module   | 0  | 11              | 19                        |

| Ground/Module   | 5  | 12              | 9                         |

| Ground/Module   | 7  | 13              | 23                        |

| Ground/Module   | 9  | 14              | 27                        |

| Ground/Module   | 11 | 15              | 21                        |

| Ground/Module   | 13 | 16              | 35                        |

| Ground/Module   | 15 | 17              | 39                        |

| Ground/Module   | NC | 18              | _                         |

| Ground/Module   | NC | 19              | _                         |

| Ground/Module   | NC | 20              | _                         |

| Data Bit/Module | 3  | 21              | 16                        |

| Data Bit/Module | 1  | 22              | 22                        |

| Data Bit/Module | 6  | 23              | 12                        |

| Data Bit/Module | 8  | 24              | 26                        |

| Data Bit/Module | 10 | 25              | 30                        |

| Data Bit/Module | 12 | 26              | 34                        |

| Data Bit/Module | 14 | 27              | 38                        |

| Ground/Module   | 3  | 28              | 15                        |

| Ground/Module   | 1  | 29              | 21                        |

| Ground/Module   | 4  | 30              | 17                        |

| Ground/Module   | 6  | 31              | 11                        |

| Ground/Module   | 8  | 32              | 25                        |

| Ground/Module   | 10 | 33              | 29                        |

| Ground/Module   | 12 | 34              | 33                        |

| Ground/Module   | 14 | 35              | 37                        |

| VCC2            |    | 36              | —                         |

| AC Common       |    | 37              |                           |

NOTE: 5MT D CONNECTOR IS AMP 205713-1

#### TM 990/310 PROGRAMMING

#### 5.1 GENERAL

This section describes how to use the CRU to access the TM 990/310 and how to do the following:

- Set and use input and output

- Use the clock

- Use interrupts

#### 5.2 PROGRAMMING CONSIDERATIONS

The following sections contain points which should be kept in mind while writing software for the TM 990/310 or while studying the examples.

5.2.1 Input/Output

The 16 I/O pins of the TMS 9901 will be set to the input mode by any of the following:

- 1. Activating the RESET switch on the microcomputer board (TM 990/1XX).

- 2. Completion of a powerup reset.

- 3. Execution of the RESET external instruction.

- 4. Writing a zero to CRU bit 15 of a TMS 9901 while it is in the clock mode.

All 48 I/O bits on the TM 990/310 will be reset by 1, 2 or 3 above. Only one specified TMS 9901 will be reset by number 4 above.

Bits are set as output bits by writing a value to them. Once addressed as outputs, bits remain outputs until reset.

Since all 48 I/O bits have pullup resistors, all bits wired as outputs (to relays, solenoids, LED's, etc.) will be put in the logic one state by any reset condition, until changed by user software.

CAUTION

Once a bit is set as an output, do not attempt to use it as an input before it is reset or the output buffers may be damaged.

#### 5.2.2 Interrupts

At each P2, P3 and P4 connector, nine of the 16 I/O lines can be used as logic zero interrupts (active low). These are the INT7-/P15 through INT15-/P7 lines at the TMS 9901.

The TMS 9901 responds to a negative-edge-triggered interrupt at its INT5input and a positive-edge-triggered interrupt at its INT6- input. The edge-triggered interrupts, levels 5 and 6 of each TMS 9901, must be software reset with CRU output instructions (see Table 5-1).

#### NOTE

INT1-, INT2-, INT3-, and INT4- to each TMS 9901 are unused. (INT5- and INT6- are edge-triggered interrupts, and INT7- to INT15- are shared with I/O ports P15 to P7 respectively.)

A backplane reset or execution of the RSET external instruction resets all edge-triggered interrupts and sets all three TMS 9901's to input mode.

Jumper platforms U1 and U6 are wired at the factory so that all interrupts at P2, P3 and P4 will result in a level 4 interrupt input to the TMS 9901 on the microcomputer board. It might be advantageous, from a software point of view, to have the individual TMS 9901's dedicated to three different interrupts. They can be changed as explained in paragraph 2.3.2.

The interrupt levels of the three TMS 9901's should not be confused with backplane priority. Each TMS 9901 has a maximum of fifteen interrupt levels (four are always unused) which may be enabled or disabled by the TM 990/310 software. Backplane priority refers to the TMS 9900 priority levels. For example, all interrupt levels of the TM 990/310 are initially wired to backplane priority 4 (connect to bus pin INT4-).

#### 5.3 EXAMPLE PROGRAMS

The following switch S1 settings are assumed for all of the following examples:

Switch No's = 1 2 3 4 ON ON OFF ON (Hexadecimal)

This setting corresponds to CRU base addresses (hexadecimal) as follows:

| Port | TMS 9901      | Hardware<br>Base Address | Software<br>Base Address |

|------|---------------|--------------------------|--------------------------|

| P2   | TMS 9901 No.1 | 0280                     | 0500                     |

| P3   | TMS 9901 No.2 | 02C0                     | 0580                     |

| P4   | TMS 9901 No.3 | 0300                     | 0600                     |

A complete CRU map of the three ports is given in Table 5-1.

#### NOTE

Each port uses an address space of 64 CRU bits. As shown in Table 5-1, port addresses are contiguous with port P2 the lowest address followed by P3 which is followed by P4.

TABLE 5-1. CRU MAP (SHEET 1 OF 2)

|           |             | , 1                  |            |      |                        |                                   |

|-----------|-------------|----------------------|------------|------|------------------------|-----------------------------------|

| Softwa    | re Displace | ment <sub>16</sub> ' |            |      |                        |                                   |

| TMS 9901  | TMS 9901    | TMS 9901             | P2/P3/P4   | CRU2 | CRU <sup>3</sup>       | cru <sup>5</sup>                  |

| No.1 (P2) | No.2 (P3)   | No.3 (P4)            | Pin No.    | Bit  | Read                   | Write                             |

| 0         | 80          | 100                  | _          | 0    | Control                | Control                           |

| Ů         | 00          | 100                  | -          | 0    | Bit                    | Bit                               |

| 2         | 82          | 102                  | _          | 1    | - /CLK1                | MASK1/CLK1                        |

| 4         | 84          | 104                  | _          | 2    | - /CLK2                | MASK2/CLK2                        |

| 6         | 86          | 106                  | · _        | 3    | - /CLK3                | MASK3/CLK3                        |

| 8         | 88          | 108                  |            | 4    | - /CLK4                | MASK4/CLK4                        |

| A         | 8A          | 10A                  | 6          | 5    | INT5/CLK5              | MASK5/CLK5                        |

| С         | 8C          | 10C                  | 8          | 6    | INT6/CLK6              | MASK6/CLK6                        |

| Е         | 8E          | 10E                  | 40         | 7    | INT7/CLK7              | MASK7/CLK7                        |

| 10        | 90          | 110                  | 38         | 8    | INT8/CLK8              | MASK8/CLK8                        |

| 12        | 92          | 112                  | 36         | 9    | INT9/CLK9              | MASK9/CLK9                        |

| 14        | 94          | 114                  | 34         | 10   | INT10/CLK10            | MASK10/CLK10                      |

| 16        | 96          | 116                  | 32         | 11   | INT11/CLK11            | MASK11/CLK11                      |

| 18        | 98          | 118                  | 30         | 12   | INT12/CLK12            | MASK12/CLK12                      |

| 1A        | 9A          | 1 1A                 | 28         | 13   | INT13/CLK13            | MASK13/CLK13                      |

| 1C        | 9C          | 11C                  | 26         | 14   | INT14/CLK14            | MASK14/CLK14                      |

| 1E        | 9E          | 1 1E                 | 24         | 15   | INT15/INTREQ           | MASK15/RST2-                      |

| 20        | AO          | 120                  | 20         | 16   | INO                    | OUTO                              |

| 22        | A2          | 122                  | 22         | 17   | IN1                    | OUT 1                             |

| 24        | A4          | 124                  | 14         | 18   | IN2                    | OUT2                              |

| 26        | Aó          | 126                  | 16         | 19   | IN3                    | OUT 3                             |

| 28        | A8          | 128                  | 18         | 20   | IN4                    | OUT4                              |

| 2A        | AA          | 12A                  | 10         | 21   | IN5                    | OUT5                              |

| 20        | AC          | 120                  | 12         | 22   | IN6                    | OUT6                              |

| 2E        | AE          | 12E                  | 24         | 23   | IN7/INT15 <sup>4</sup> | OUT7                              |

| 30        | B0          | 130                  | 26         | 24   | IN8/INT14              | OUT8                              |

| 32        | B2          | 132                  | 28         | 25   | IN9/INT13              | OUT9                              |

| 34        | В4          | 134                  | 30         | 26   | IN10/INT12             | OUT 10                            |

| 36        | B6          | 136                  | 32         | 27   | IN11/INT11             | OUT 1 1                           |

| 38        | в8          | 138                  | 34         | 28   | IN12/INT10             | OUT 12                            |

| 3A        | BA          | 13A                  | 36         | 29   | IN13/INT9              | OUT 13                            |

| 3C        | BC          | 13C                  | 38         | 30   | IN14/INT8              | OUT 14                            |

| 3E        | BE          | 13E                  | 40         | 31   | IN15/INT7              | OUT 15                            |

| 40        | CO          | 140                  | -          | 32   | _                      | _                                 |

| 42        | C2          | 142                  | -          | 33   | -                      | _                                 |

| 44        | C4          | 144                  | -          | 34   | -                      | -                                 |

| 46        | Сб          | 146                  | <b>_</b> · | 35   | -                      | _                                 |

| 48        | C8          | 148                  | -          | 36   | -                      | INT5 Reset (P1,P3                 |

| 4A        | CA          | 14A                  | -          | 37   | -                      | only)<br>INT6 Reset(P1,P3)        |

| 4C        | CC          | 14C                  | -          | 38   | -                      | INT5 Reset (P2)<br>INT6 Reset (P2 |

| 4E        | CE          | 14E                  |            |      |                        | only)                             |

| 40        |             | 146                  | •••        | 39   | <b></b>                | -                                 |

TABLE 5-1. CRU MAP (SHEET 2 OF 2)

| Softwa                | re Displace           | ment <sub>16</sub> 1  |                     |                         |                          |                           |

|-----------------------|-----------------------|-----------------------|---------------------|-------------------------|--------------------------|---------------------------|

| TMS 9901<br>No.1 (P2) | TMS 9901<br>No.2 (P3) | TMS 9901<br>No.3 (P4) | P2/P3/P4<br>Pin No. | CRU <sup>2</sup><br>Bit | CRU <sup>3</sup><br>Read | CRU <sup>5</sup><br>Write |

| 50                    | DO                    | 150                   | -                   | 40                      | -                        | -                         |

| 52                    | D2                    | 152                   |                     | 41                      | -                        | -                         |

| 54                    | D4                    | 154                   | -                   | 42                      | -                        | -                         |

| 56                    | D6                    | 156                   | -                   | 43                      | -                        | -                         |

| 58                    | D8                    | 158                   |                     | 44                      | -                        | -                         |

| 5A                    | DA                    | 15A                   | -                   | 45                      | -                        | · _                       |

| 50                    | DC                    | 15C                   | <b>-</b>            | 46                      | -                        | -                         |

| 5E                    | DE                    | 15E                   | -                   | 47                      | -                        | -                         |

| 60                    | EO                    | 160                   | 20                  | 48                      | Echo OUTO                | -                         |

| 62                    | E2                    | 162                   | 22                  | 49                      | Echo OUT1                | -                         |

| 64                    | Е4                    | 164                   | 14                  | 50                      | Echo OUT2                | -                         |

| 66                    | E6                    | 166                   | 16                  | 51                      | Echo OUT3                | -                         |

| 68                    | E8                    | 168                   | 18                  | 52                      | Echo OUT4                | -                         |

| 6A                    | EA                    | 16A                   | 10                  | 53                      | Echo OUT5                |                           |

| 6C                    | EC                    | 16C                   | 12                  | 54                      | Echo OUT6                | -                         |

| 6E                    | EE                    | 16E                   | 24                  | 55                      | Echo OUT7                | -                         |

| 70                    | FO                    | 170                   | 26                  | 56                      | Echo OUT8                | -                         |

| 72                    | F2                    | 172                   | 28                  | 57                      | Echo OUT9                | _                         |

| 74                    | F4                    | 174                   | 30                  | 58                      | Echo OUT10               | -                         |

| 76                    | Fб                    | 176                   | 32                  | 59                      | Echo OUT11               | -                         |

| 78                    | F8                    | 178                   | 34                  | 60                      | Echo OUT12               | -                         |

| 7A                    | FA                    | 17A                   | 36                  | 61                      | Echo OUT13               | -                         |

| 7C                    | FC                    | 17C                   | 38                  | 62                      | Echo OUT14               | -                         |

| 7E                    | FE                    | 17E                   | 40                  | 63                      | Echo OUT 15              | -                         |

<sup>1</sup>This column represents the value to be added to the software base address, as determined by switch S1, to access a given block of bits (e.g., add 2016 to the software base address to place values on OUTO through OUT15 with a LDCR instruction loading 16 bits).

<sup>2</sup>This column represents the displacement to be used with a CRU single bit instruction (e.g., SBO, SBZ, TB) with no displacement added to the base address.

<sup>3</sup>When Control Bit = 1, the top 16 bits of this column represent the CLK Read register or the INTREQ bit. When Control Bit = 0, the top 16 bits of this column represents the incoming interrupts (if enabled).

<sup>4</sup>The following 9 bits represent I/O bits unless the interrupt mask is set (enable= 1) for the corresponding INTX.

<sup>5</sup>When Control bit = 1, writing to the CLK bits sets the clock and writing to RST2- causes a reset. When Control Bit = 0, writing a 1 to a MASK bit enables the corresponding INTX.

## 5.3.1 Input/Output Example Program

This program demonstrates using the I/O and Echo bits. A cable as shown in Figure 5-1 will be needed for this program. The cable connects P2 (TMS 9901 no. 1) and P3 (TMS 9901 no. 2) so that the output bits of no. 1 TMS 9901 connect to the input bits of no. 2 TMS 9901.

- Reset the TMS 9901's.

- Set TMS 9901 no. 1 as output; output a test pattern.

- Read TMS 9901 no. 1 Echo bits and compare with test pattern; output error message if not the same.

- Read TMS 9901 no. 2 input bits and compare with test pattern; output error message if not the same.

- If both tests pass, print message and branch to monitor.

FIGURE 5-1. CABLE FOR EXAMPLE PROGRAMS

|                                                               |                 | ****                   | ***********                    | ***************************************                                                                                                                                                                                     |

|---------------------------------------------------------------|-----------------|------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                               | *<br>*<br>*     | INPU                   | I/OUTPUT EXAMI                 | * PLE PROGRAM *                                                                                                                                                                                                             |

|                                                               | *****<br>*      |                        |                                | ***************************************                                                                                                                                                                                     |

|                                                               | *               | MAIN                   | PROGRAM                        | *                                                                                                                                                                                                                           |

| F000                                                          | *****           |                        | *************<br>>F000         | ****************                                                                                                                                                                                                            |

| F 000                                                         | ¥               | AONG                   | ~F000                          |                                                                                                                                                                                                                             |

|                                                               | *<br>*          | DEFIN                  | NITIONS                        |                                                                                                                                                                                                                             |

| 0500<br>0520<br>0540<br>0560<br>F000                          | PORT 1<br>INT2  | equ<br>Equ<br>Equ      | >0580                          | CRU ADDRESS OF 9901 NO.1 - INTERRUPT SECT.<br>CRU ADDRESS OF 9901 NO.1 - PORT SECTION<br>CRU ADDRESS OF 9901 NO.2 - INTERRUPT SECT.<br>CRU ADDRESS OF 9901 NO.2 - PORT SECTION<br>WORKSPACE                                 |

|                                                               | *               | INIT                   | LALIZATION                     |                                                                                                                                                                                                                             |

|                                                               | *               | RESET                  | 5 9901 NO.1                    |                                                                                                                                                                                                                             |

| F020 02E0                                                     | -               | LWPI                   | WSP                            |                                                                                                                                                                                                                             |

| F022 F000<br>F024 020C                                        | INIT            | LI                     | R12, INT1                      | LOAD CRU ADDRESS OF 9901 NO.1                                                                                                                                                                                               |

| F026 0500<br>F028 1D00                                        |                 | SBO                    | 0                              | SET TO CLOCK MODE                                                                                                                                                                                                           |

| FO2A 1EOF                                                     | ×               | SBZ                    | 15                             | RESET                                                                                                                                                                                                                       |

|                                                               | *               | RESE                   | F 9901 NO.2                    |                                                                                                                                                                                                                             |

| F02C 020C<br>F02E 0580                                        |                 | LI                     | R12,INT2                       | LOAD CRU ADDRESS OF 9901 NO.2                                                                                                                                                                                               |

| F030 1D00<br>F032 1E0F                                        | *               | SBO<br>SBZ             | 0<br>15                        | SET TO CLOCK MODE<br>RESET                                                                                                                                                                                                  |

|                                                               | *               | SET                    | PORT 1 (9901 )                 | NO.1) AS OUTPUT; OUTPUT PATTERN                                                                                                                                                                                             |

| F034 020C<br>F036 0520                                        |                 | LI                     | R12, PORT1                     | LOAD CRU ADDRESS OF PORT 1                                                                                                                                                                                                  |

| F038 0202<br>F038 AAAA                                        |                 | LI                     | R2,>AAAA                       | LOAD BIT PATTERN '1010101010101010'                                                                                                                                                                                         |

| F03C 3002                                                     | ¥               | LDCR                   | R2,0                           | SETS PORT 1 = OUTPUT, OUTPUTS PATTERN                                                                                                                                                                                       |

| F03E 3403<br>F040 80C2<br>F042 1606                           | <br>*<br>*<br>* | AI<br>STCR<br>C<br>JNE | R12,>40<br>R3,0<br>2,3<br>ERR1 | MS 9901 NO. 1; COMPARE WITH TEST PATTERN<br>SET CRU ADDRESS TO ECHO CHARACTERS<br>ECHOS PORT 1 OUTPUT BACK TO R3<br>IS OUTPUT AND ECHO THE SAME?<br>IF NOT, OUTPUT ERROR MESSAGE<br>MS 9901 NO.2; COMPARE WITH TEST PATTERN |

| EO HILL COOC                                                  | *               |                        |                                |                                                                                                                                                                                                                             |

| F044 020C<br>F046 0580<br>F048 3404<br>F04A 8102<br>F04C 160F |                 | STCR<br>C              |                                | SET CRU BASE ADDRESS TO PORT 2 (9901 No.2)<br>READ PORT 2 INPUTS<br>PORT 2 INPUTS EQUAL PORT 1 OUTPUTS<br>IF NOT, OUTPUT ERROR MESSAGE                                                                                      |

| F04C 160F                                                     |                 | JNE                    | ERR2                           | IF NOT, OUTPUT ERROR MESSAGE                                                                                                                                                                                                |

|                                                                                              | *<br>*    | IF B                                      | OTH TESTS PAS                                                        | S, GO TO FINISH                                                                                                   |

|----------------------------------------------------------------------------------------------|-----------|-------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| F04E 101D                                                                                    | *****     | JMP                                       |                                                                      | TESTS PASSED, GO TO FINISH                                                                                        |

|                                                                                              | * ERR     |                                           | SSAGES                                                               | ***************************************                                                                           |

|                                                                                              |           | *****                                     | ******                                                               | *<br>************************************                                                                         |

|                                                                                              | ¥<br>¥    | ERRO                                      | R MESSAGE 1 -                                                        | ERROR- NO ECHO                                                                                                    |

| F050 2FA0<br>F052 F058                                                                       | ERR1      | XOP                                       | @MESS1,14                                                            | OUTPUT ERROR MESSAGE 1                                                                                            |

| F054 0460<br>F056 0080                                                                       |           | В                                         | <b>e</b> >80                                                         | BRANCH TO MONITOR                                                                                                 |

| F058ODOAF05A45F05B52F05C52F05D4FF05E52F05F2DF06020F0614EF0624FF06320F06445F06543F06648F0674F | MESS 1    | TEXT                                      | 'ERROR- NO E                                                         |                                                                                                                   |

| F068 ODOA                                                                                    |           | ር እስጥ እ                                   |                                                                      |                                                                                                                   |

| F06A 0000                                                                                    | ¥         |                                           |                                                                      | CARRAGE RETURN/LINE FEED<br>END OF MESSAGE TAG                                                                    |

| F06A 0000                                                                                    | *         | DATA                                      | >0000                                                                |                                                                                                                   |

| F06C 2FAO                                                                                    | **        | DATA                                      | >0000<br>R MESSAGE 2 -                                               | END OF MESSAGE TAG                                                                                                |

|                                                                                              | *         | DATA<br>ERROI                             | >0000<br>R MESSAGE 2 -                                               | END OF MESSAGE TAG<br>ERROR- NO INPUTS                                                                            |

| F06C 2FA0<br>F06E F074<br>F070 0460                                                          | *<br>ERR2 | DATA<br>ERROI<br>XOP<br>B<br>DATA<br>TEXT | >0000<br>R MESSAGE 2 -<br>@MESS2,14<br>@>80<br>>0D0A<br>'ERROR- NO I | END OF MESSAGE TAG<br>ERROR- NO INPUTS<br>OUTPUT ERROR MESSAGE 2<br>BRANCH TO MONITOR<br>CARRAGE RETURN/LINE FEED |

|              |              | *<br>*<br>* | MESS | AGE 3 - | TESTS  | PASSED                   |

|--------------|--------------|-------------|------|---------|--------|--------------------------|

| F08A<br>F08C | 2FA0<br>F092 | FIN         | XOP  | @MESS3, | 14     |                          |

| F08E<br>F090 |              |             | В    | @>80    |        | BRANCH TO MONITOR        |

| F092         | ODOA         | MESS3       | DATA | >ODOA   |        | CARRAGE RETURN/LINE FEED |

| F094         | 54           |             | TEXT | 'TESTS  | PASSEI | <b>)</b>                 |

| F095         | 45           |             |      |         |        |                          |

| F096         | 53           |             |      |         |        |                          |

| F097         | 54           |             |      |         |        |                          |

| F098         | 53           |             |      |         |        |                          |

| F099         | 20           |             |      |         |        |                          |

| F09A         | 50           |             |      |         |        |                          |

| F09B         | 41           |             |      |         |        |                          |

| F09C         | 53           |             |      |         |        |                          |

| F09D         | 53           |             |      |         |        |                          |

| F09E         | 45           |             |      |         |        |                          |

| F09F         | 44           |             |      |         |        |                          |

| FOAO         | ODOA         |             | DATA | > ODOA  |        | CARRAGE RETURN/LINE FEED |

| F0A2         | 0000         |             | DATA | >0000   |        | END OF MESSAGE TAG       |

5.3.2 Clock Example Program (Polling)

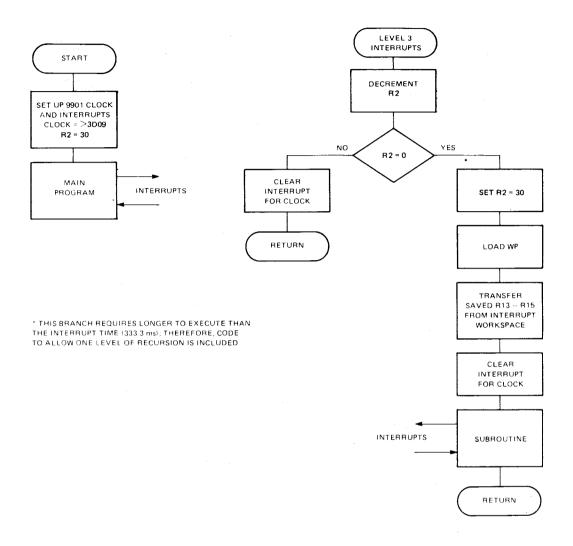

This program demonstrates how to set and use the clock on no. 1 TMS 9901 on the TM 990/310 module. After a period of five seconds, a message is written. This example requires no TM 990/310 cable or connectors. The steps of this program are as follows:

- 1. Reset the TMS 9901.