As you are now the owner of this document which should have come to you for free, please consider making a donation of £1 or more for the upkeep of the (Radar) website which holds this document. I give my time for free, but it costs me money to bring this document to you. You can donate here <u>https://blunham.com/Misc/Texas</u>

Many thanks.

Please do not upload this copyright pdf document to any other website. Breach of copyright may result in a criminal conviction.

This Acrobat document was generated by me, Colin Hinson, from a document held by me. I requested permission to publish this from Texas Instruments (twice) but received no reply. It is presented here (for free) and this pdf version of the document is my copyright in much the same way as a photograph would be. If you believe the document to be under other copyright, please contact me.

The document should have been downloaded from my website <u>https://blunham.com/</u>, or any mirror site named on that site. If you downloaded it from elsewhere, please let me know (particularly if you were charged for it). You can contact me via my Genuki email page: <u>https://www.genuki.org.uk/big/eng/YKS/various?recipient=colin</u>

You may not copy the file for onward transmission of the data nor attempt to make monetary gain by the use of these files. If you want someone else to have a copy of the file, point them at the website. (<u>https://blunham.com/Misc/Texas</u>). Please do not point them at the file itself as it may move or the site may be updated.

It should be noted that most of the pages are identifiable as having been processed by me.

If you find missing pages, pages in the wrong order, anything else wrong with the file or simply want to make a comment, please drop me a line (see above).

It is my hope that you find the file of use to you.

Colin Hinson In the village of Blunham, Bedfordshire.

I put a lot of time into producing these files which is why you are met with this page when you open the file.

The Engineering Staff of TEXAS INSTRUMENTS LIMITED

Semiconductor Group

May 1982 DM-11

# Texas Instruments

Texas Instruments . . . the inventor of the integrated circuit, the microprocessor, and the microcomputer . . . is a leader in the technology that provides electronic sensing, control, computing, and even speech. For additional information on TI's high-technology products contact:

Texas Instruments Incorporated Regional Technology Center 515 W. Algonquin Road Arlington Heights, IL 60005 (312) 640-2909

Texas Instruments Incorporated Regional Technology Center 3300 N.E. Expressway Building 8 Atlanta, GA 30341 (404) 452-4682 Texas Instruments Incorporated Regional Technology Center 17620 Fitch Avenue Irvine, CA 92714 (714) 545-5210

Texas Instruments Incorporated Regional Technology Center Dallas, TX

\*will open 2Q82\*

Texas Instruments Incorporated Regional Technology Center 400-2 Totten Pond Road Waltham, MA 02154 (617) 890-6671

Texas Instruments Incorporated Regional Technology Center 5353 Betsy Ross Drive Santa Clara, CA 95054 (408) 748-2300

#### **IMPORTANT NOTICES**

Texas Instruments reserves the right to make changes at any time to improve design and to supply the best possible product for the spectrum of users.

This publication is printed in the United States of America and is copyrighted by Texas Instruments Incorporated. All rights reserved. No part of these publications may be reproduced in any manner including storage in a retrieval system or transmittal via electronic means, or other reproduction in any form or any method (electronic, mechanical, photocopying, recording, or otherwise) without prior written permission of Texas Instruments Incorporated.

TI owns utility patents relevant to talking electronic apparatus and intends to license such patents on reasonable terms and conditions and on a non-discriminatory basis to its buyers and non-buyers alike. The foregoing intent to license TI's utility patents does not apply if the buyer's product infringes any TI design patent, copyright, or trademark, or is of such appearance as to confuse consumers as to its origin.

TI intends to enforce its intellectual property rights to the fullest extent permitted by law. Neither the sale by TI of integrated circuits or other semiconductor components nor the granting of technical assistance or other information by TI to its buyers, actual or prospective, to assist in the use of such semiconductor components shall grant to, convey or confer on Buyer or Buyer's customer, or upon anyone claiming under Buyer, a license, expressed or implied, under any patent rights, copyrights, trademarks, or other intellectual property rights of TI covering or relating to any combination, machine or process in which such semiconductor components might be or are used.

> Copyright © 1982 Texas Instruments Incorporated

## TABLE OF CONTENTS

| 1. | INTRODUCTION                                                | . 1  |

|----|-------------------------------------------------------------|------|

| 2. | THEORY OF OPERATION   2.1 Linear Predictive Coding          | 1    |

|    | 2.2 TMS5110A                                                | . 2  |

| 3. | OPERATION OF TMS5110A VSP WITH TMS6100 VSM / TMS6125 VSM    | . 5  |

| 4. | TMS5110A SPECIFICATIONS                                     | . 7  |

|    | 4.1 Absolute Maximum Ratings                                | . 7  |

|    | 4.2 Recommended Operating Conditions                        | . 7  |

|    | 4.3 Electrical Characteristics                              | . 7  |

|    | 4.4 Timing Requirements, Data Output and I/O Mode Switching | . 7  |

|    | 4.5 Timing Requirements, Command and Data Transfer          | . 8  |

|    | 4.6 Switching Characteristics                               | . 8  |

| 5. | MECHANICAL DATA                                             | . 10 |

|    | 5.1 TMS5110A 28-Pin 600 mil Plastic Package                 | . 10 |

|    | 5.2 TMS5110A 28-Pin 400 mil Plastic Package                 |      |

|    | 5.3 Pin Assignments and Functions                           |      |

|    | 5.4 Terminal Assignments                                    | . 12 |

## APPENDIX

| System Clock |  | 13 |

|--------------|--|----|

|--------------|--|----|

## LIST OF ILLUSTRATIONS

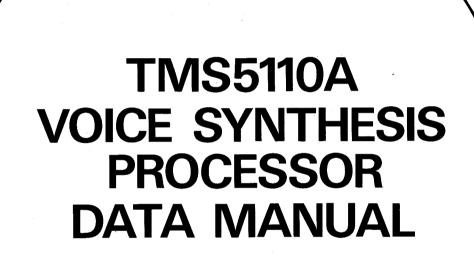

| Figure 1 | Operation Flow-Talk Command Sequence               | 4 |

|----------|----------------------------------------------------|---|

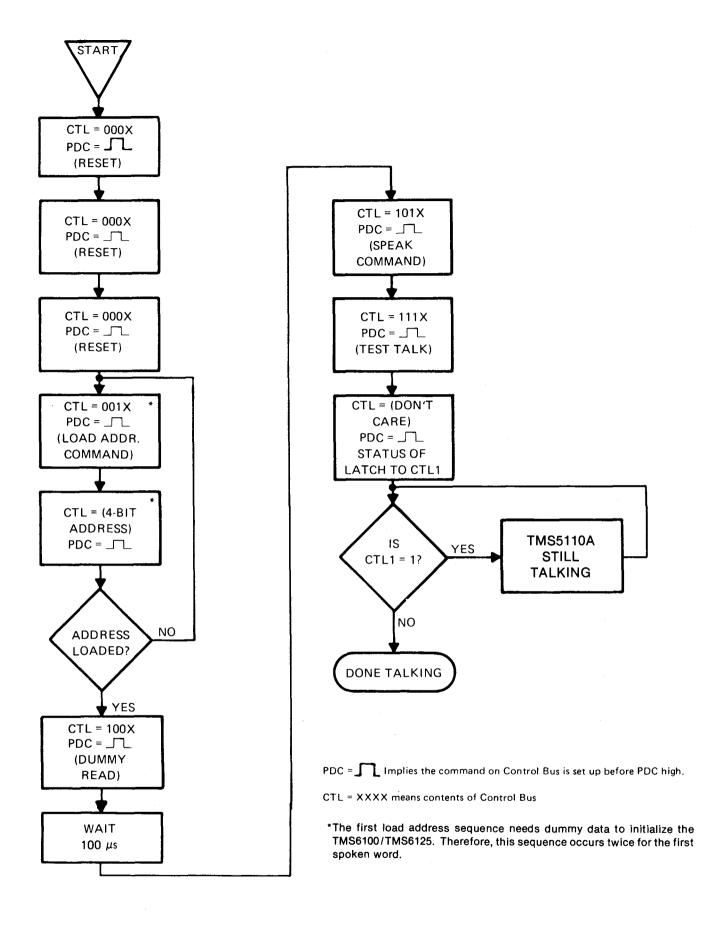

|          | Operation Flow-Read/Output Command Sequence        |   |

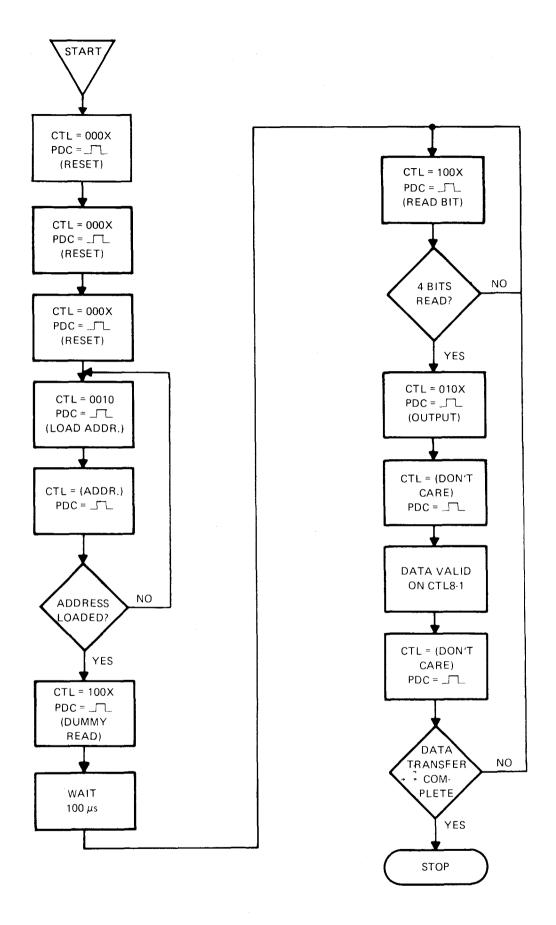

|          | Timing Diagram, Data Output and I/O Mode Switching |   |

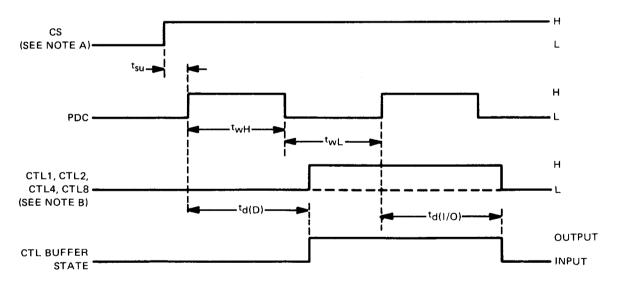

|          | Timing Diagram, Command and Data Transfer          |   |

|          | TMS5110A Oscillator                                |   |

## LIST OF TABLES

| Table 1   | TEN                          | 2 |

|-----------|------------------------------|---|

| Table 2   | TMS5110A Command List        | 2 |

| Table A-1 | A comparison of System Times |   |

## 1. INTRODUCTION

The TMS5110A is a PMOS Voice Synthesis Processor (VSP). Speech is synthesized by processing an externally provided variable data-rate bit stream of encoded speech data and converting the result to an audible output with an on-chip eight-bit D/A converter and push-pull amplifier. The TMS5110A is designed to work with up to sixteen TMS6100 128K-bit (ROM) or up to four TMS6125 32K-bit (ROM) Voice Synthesis Memories (VSM). The TMS5110A outputs all control signals necessary for direct control of the VSP which is provided by an external device (e.g. TMS1000) through four control pins and a command clock.

## 2. THEORY OF OPERATION

#### 2.1 LINEAR PREDICTIVE CODING

LPC synthesizes human speech by recovering from the original speech enough data to construct a time-varying digital filter model of the vocal tract. This filter is excited with a digital representation of either glottal air impulses (voiced sound) or the rush of air, which produces unvoiced sounds. The output of this filter model is passed through an 8-bit digital-to-analog (D/A) converter to produce a synthetic speech waveform. The TMS5110A performs all of these operations.

The TMS5110A design is based on a 40 hertz input frame rate (the rate at which new speech data — a maximum of 49 bits/frame — is obtained from the vocabulary memories). The output speech waveform from the D/A converter changes at an 8 kHz rate, which corresponds to a maximum speech output frequency of 4 kHz. Each 49-bit frame defines excitation and filter characteristics that are linearly interpolated (every 3.125 milliseconds) to be smoothly time-varying throughout the 25-millisecond interval between frames. This allows a 1960 bit/second maximum data rate to produce high-quality speech. The data rate is actually slower than this since certain parameters are not necessary in some instances, as described in the next section. Each 49-bit frame is composed of 13 parameters:

- (1) Energy (amplitude four bits)

- (2) Repeat bit

- (3) Pitch (fundamental frequency five bits)

- (4) Ten reflection coefficients (K-parameters-K1 and K2, five bits each; K3-K7, four bits each; K8-K10, three bits each)

The K parameters define the vocal transfer function.

A full set of parameters for each frame would require a data rate of 40 Hz  $\times$  49 bits = 1960 bit/second. Three special cases, in which a full frame is not necessary, allow the data rate to be considerably reduced:

- (1) Since the vocal tract changes shape relatively slowly, it is often possible to repeat previous reflection coefficient data. If the repeat bit is set to a 1, the K parameters from the previous frame are used and no more data is accessed from memory. This makes repeated frames only 10 bits in length (4 energy, 1 repeat, 5 pitch.)

- (2) Unvoiced sounds (such as s, f, t, sh) require fewer reflection coefficients. When pitch = 00000, only K1-K4 are used. K5-K10 are internally zeroed, making an unvoiced frame of 28 bits (4 energy, 1 repeat, 5 pitch, K1 and K2 five bits each, K3 and K4 four bits each).

- (3) When energy = 0000, no other data is required. Energy is zero during interword or intersyllable pauses. When energy = 1111, it is detected as an end-of-phrase and the TMS5110A stops talking. Both of these cases yield a fourbit frame.

The combination of these three cases has reduced the average data rate to nominally 1200 bits/sec.

EXAMPLE PHRASE — "TEN"

Table 1 shows the word "TEN" bit by bit, frame by frame.

| TABLE 1 - | - "TEN" |

|-----------|---------|

|-----------|---------|

| Frame | Erms  | E | c Pite | ch K1 | К2    | К3   | K4 | K5  | K6   | K7   | K8   | K9  | K10 | _   |

|-------|-------|---|--------|-------|-------|------|----|-----|------|------|------|-----|-----|-----|

| 1.    | 821.  |   | 8 (    | ) 24  | 2     | 7    | 5  |     |      |      | -    |     |     | -   |

| 2.    | 1011. |   | 8 (    | ) 18  | 6     | 3    | 5  |     |      |      |      |     |     |     |

| 3.    | 1357. | 1 | 2 16   | 5 20  | 10    | 4    | 10 | 8   | 9    | 5    | 1    | 2   | 3   |     |

| 4.    | 3523. | 1 | 4 15   | 5 21  | 14    | 5    | 7  | 7   | 11   | 10   | 3    | 2   | 3   |     |

| 5.    | 3559. | 1 | 4 16   | 5 20  | 14    | 5    | 10 | 8   | 12   | 11   | 4    | 2   | 3   |     |

| 6.    | 2734. | 1 | 4 17   | 7 21  | 13    | 6    | 7  | 7   | 10   | 10   | 6    | 1   | 4   |     |

| 7.    | 2460. | 1 | 4 18   | 3 23  | 14    | 7    | 7  | 5   | 6    | 9    | 6    | 2   | 3   |     |

| 8.    | 1831. | 1 | 4 2    | 1 23  | 14    | 7    | 7  | 5   | 5    | 8    | 6    | 2   | 3   |     |

| 9.    | 2164. | 1 | 4 25   | 5 23  | 11    | 11   | 7  | 4   | 8    | 8    | 6    | 3   | 3   |     |

| 10.   | 1553. | 1 | 3 26   | 5 21  | 13    | 11   | 5  | 4   | 8    | 10   | 6    | 2   | 4   |     |

| 11.   | 625.  |   | 1 2    | 7 19  | 18    | 6    | 3  | 5   | 9    | 10   | 4    | 3   | 3   |     |

| 12.   | 190.  |   | 8 28   | 3 19  | 6     | 4    | 6  | 12  | 5    | 8    | 4    | 2   | 5   |     |

| 13.   | 197.  |   | 7 2    | 9 19  | 6     | 4    | 6  | 12  | 5    | 8    | 4    | 2   | 5   |     |

| 15.   | 134.  |   | 7 30   | 0 19  | 7     | 5    | 5  | 12  | 7    | 8    | 4    | 2   | 5   |     |

| 16.   | 110.  |   | 6 30   | 0 21  | 6     | 4    | 3  | 12  | 9    | 7    | 5    | 2   | 5   |     |

| Frame | Ec    | R | Pitch  | K1    | K2    | K3   |    | K4  | K5   | K6   | K7   | K8  | К9  | K1  |

| 1.    | 1000  | 0 | 00000  | 11000 | 00010 | 0111 |    | 101 |      |      |      |     |     |     |

| 2.    | 1000  | 0 | 00000  | 10010 | 00110 | 0011 |    | 101 |      |      |      |     |     | ~   |

| 3.    | 1100  | 0 | 10000  | 10100 | 01010 | 0100 |    | 010 | 1000 | 1001 | 0101 | 001 | 010 | 01  |

| 4.    | 1110  | 0 | 01111  | 10101 | 01110 | 0101 |    | 111 | 0111 | 1011 | 1010 | 011 | 010 | 01  |

| 5.    | 1110  | 0 | 10000  | 10100 | 01110 | 0101 |    | 010 | 1000 | 1100 | 1011 | 100 | 010 | 01  |

| 6.    | 1110  | 0 | 10001  | 10101 | 01101 | 0110 |    | 111 | 0111 | 1010 | 1010 | 110 | 001 | 10  |

| 7.    | 1110  | 0 | 10010  | 10111 | 01110 | 0111 | 0  | 111 | 0101 | 0110 | 1001 | 110 | 010 | 01  |

| 8.    | 1110  | 1 | 10101  |       |       |      | -  |     |      |      |      |     | 011 | 0.4 |

| 9.    | 1110  | 0 | 11001  | 10111 | 01011 | 1011 |    | 111 | 0100 | 1000 | 1000 | 110 | 011 | 01  |

| 10.   | 1101  | 0 | 11010  | 10101 | 01101 | 1011 |    | 101 | 0100 | 1000 | 1010 | 110 | 010 | 10  |

| 11.   | 1011  | 0 | 11011  | 10011 | 10010 | 0110 |    | 011 | 0101 | 1001 | 1010 | 100 | 011 | 01  |

| 12.   | 1000  | 0 | 11100  | 10011 | 00110 | 0100 | 0  | 110 | 1100 | 0101 | 1000 | 100 | 010 | 10  |

| 13.   | 0111  | 1 | 11101  |       |       |      | ~  | 404 | 4400 |      | 4000 | 100 | 010 | 10  |

| 14.   | 0111  | 0 | 11110  | 10011 | 00111 | 0101 | -  | 101 | 1100 | 0111 | 1000 | 100 | 010 | 10  |

| 15.   | 0110  | 0 | 11110  | 10101 | 00110 | 0100 | 0  | 011 | 1100 | 1001 | 0111 | 101 | 010 | 10  |

| 16.   | 1111  |   |        |       |       |      |    |     |      |      |      |     |     |     |

#### 2.2 TMS5110A

The TMS5110A is controlled by commands on five pins: the Control Bus (CTL 1,2,4,8) and the processor data clock (PDC) (see Table 2). A command is first set up on the Control Bus (with the PDC low), then strobed into the device by toggling the PDC (low – high – low). Multi-nibble commands, such as Load Address, are executed by strobing in the command first, then setting up the data on the Control Bus and toggling the PDC. The beginning of each command description gives the binary form of each command.

|               |               | PDC'S |      |               |          |

|---------------|---------------|-------|------|---------------|----------|

| NAME          | CTL8<br>(MSB) | CTL4  | CTL2 | CTL1<br>(LSB) | REQUIRED |

| RESET         | 0             | 0     | 0    | x             | 1        |

| LOAD ADDRESS  | 0             | 0     | 1    | X             | 2        |

| OUTPUT        | 0             | 1     | 0    | х             | 3        |

| READ BIT      | 1             | 0     | 0    | x             | 1        |

| SPEAK         | 1             | 0     | ì    | x             | 1        |

| READ & BRANCH | 1             | 1     | 0    | х             | 1        |

| TEST TALK     | 1             | 1     | 1    | X             | 3        |

## TABLE 2 — TMS5110A COMMAND LIST

### RESET

The Reset command (000X) is used to synchronize a command sequence. Since there are some multi-nibble commands (such as Load Address, which requires a Load Address command followed by address data), the TMS5110A may not be ready to accept a command, for example, when the device is expecting data in a load address sequence. The Reset command must be executed three times to ensure that the next toggling of the PDC will strobe in a command, not data.

The Reset command can also be used to halt speech. The execution of the Reset command while the TMS5110A is talking completely halts the device, but does not clear any internal registers. This allows the rest of the phrase to be spoken upon subsequent execution of the Speak command.

### LOAD ADDRESS

This command (001X) loads the address of a phrase contained in the VSM. This is a two-nibble command, the first nibble is the Load Address command (001X). Once this has been toggled in, the TMS5110A expects the data on the Control Bus to be four address bits. Upon toggling the PDC, the chip gates this address (along with the proper control signals) to the VSM. This two-nibble sequence is repeated as many times as necessary to complete loading of the VSM address register. For example, the TMS6100 requires five Load Address sequences, i.e., it takes exactly ten toggles of the PDC to load an address.

## **READ & BRANCH**

This instruction (110X) is an indirect load address command for a single ROM system. The first step is to load an address. This is the address of a word in the VSM that contains the address of data that the user desires. The Read and Branch command is now executed and the VSM address register is loaded with the contents of the ROM byte (specified in the Load Address sequence) and the next consecutive byte. In this manner a look-up table of phrase addresses can be stored in the VSM and easily accessed. The execution of this command also performs a dummy read so that a Read Bit or Speak command can be immediately executed to access data or begin speech (Note: the addressed byte holds the MSB's of the VSM address. The next sequential byte holds the eight LSB's of the VSM address.) The VSM uses only the 14 LSB's of these two bytes, and therefore the Read and Branch command is local to only one VSM, i.e., a lookup table for data must be on the same chip as the data itself.

#### SPEAK

This command (101X) is used to start the TMS5110A talking. After an address has been loaded and a dummy read performed (see Figure 1), this command is toggled into the TMS5110A and it immediately begins transferring data from the VSM and talking. The speech can now be interrupted by the Reset command, if desired, and restarted later by simply toggling the Speak command into the device again. If no Reset command is issued during the speech, the device continues talking until it detects an end of phrase datum (energy = 1111).

#### TEST TALK

The Test Talk command (111X) was created so that the controlling device would know when the TMS5110A is finished talking. This is a three PDC command: the first PDC clocks in the command; the second gates the status of the talk latch in the device to CTL1 and enables the CTL output buffers; the third returns the CTL pins to inputs. After the falling edge of the second PDC, CTL1 will be high if the TMS5110A is talking. As soon as the device detects an end of phrase datum, it will go low indicating the end of speech. Note that no commands will be understood by the device until the third PDC is used, since the CTL output buffers are enabled. (See Figure 1). Also note that the method of issuing three Reset commands (see Reset command section) would also guarantee the next toggle of the PDC to mean a command exists on CTL.

#### **READ BIT/OUTPUT**

The Read Bit command (100X) is used for two reasons: (1) reading data out of the VSM in conjuction with the Output command (010X), and (2) changing the direction of the ADD8/Data line from VSP output to VSP input (a "dummy read" option prior to using a "Speak" command).

FIGURE 1 - OPERATION FLOW - TALK COMMAND SEQUENCE

Data can be read out of the VSM by:

- (1) Loading a 20-bit address,

- (2) Performing a dummy read,

- (3) Performing four Read Bit commands sequentially to load the 4-bit data buffer in the TMS5110A

- (4) Toggling the PDC with an Output command on CTL,

- (5) Toggling the PDC again to reverse the CTL pins to outputs,

- (6) Toggling the PDC again to return the CTL pins to inputs,

- (7) Going to step 3 and repeating until all needed data is obtained

Data is transferred between the VSM and the speech synthesizer over the ADD8 pin. Since this pin is usually an input on the VSM and an output on the TMS5110A, a dummy read is required to reverse the data flow so that data is now transferred in the other direction. This need only be performed when a new address is loaded. The correct direction of the data flow will still be set in cases such as interrupted speech or in between sequential data reads (see M0-Transfer bit section).

#### 3. OPERATION OF TMS5110A VSP WITH TMS6100 VSM / TMS6125 VSM.

This section is intended as an aid for those who may desire to interface the TMS6100 ROM / TMS6125 ROM to the TMS5110A. The following sections describe the timing of the control signals (ADD1, ADD2, ADD4, ADD8, ROMCLK, M0, and M1) that the TMS5110A provides to the ROM. It is suggested that the reader obtain a copy of the TMS6100/TMS6125 specification to further clarify this discussion.

## **DESCRIPTION OF THE TMS6100**

The TMS6100 contains an auto-incrementing address register. No further load address sequences are needed if the data is sequentially positioned in the ROM. See Figure 2 for operation flow.

The TMS6100 is a mask-programmable PMOS 128K-bit Read-Only Memory internally organized as 16K words of 8 bits. Externally it appears as  $128K \times 1$ . Once the 20-bit address (14 bits to select a byte within the device, 4 chip select banks, 2 bits ignored) is loaded through ADD1, ADD2, ADD4, and ADD8 in five Load Address sequences, data is read out bit-wise by toggling a control pin M0. The ROM contains an on-chip address counter that is incremented every eight bits (eight toggles of M0). The four internal chip select banks are a mask-programmable option, and allow parallel connection of up to 16 ROMs (about 30 minutes of speech) without the need of external select circuitry.

#### **DESCRIPTION OF THE TMS6125**

The TMS6125 is a PMOS 32K ROM internally organized as  $4K \times 8$ . Externally it appears as a 1-bit serial output. Once the 16-bit address (12 bits to select a byte within the device, 2 chip select banks, 2 bits ignored) is loaded through ADD1, ADD2, ADD4, and ADD8 in four Load Address sequences, data is read out bit-wise by toggling a control pin M0. The address is internally incremented after 8 bits have been read. There is a mask programmable internal bank select option allowing parallel connection of up to 4 ROMs (16K bytes).

#### M1 — LOAD ADDRESS

The TMS5110A loads an address into the TMS6100/TMS6125 using the ADD bus and M1 control pin. As the PDC is brought high during the address portion of a load address sequence, the TMS5110A brings M1 high and gates the CTL bus to the ADD bus. When the PDC is brought low, M1 goes low and the VSM stores the nibble in its address register. This 18-bit register is filled after five toggles of M1 in the TMS6100 and 4 toggles in the TMS6125. (M1 stays low when the Load Address command (001  $\times$ ) is clocked in).

#### M0 — TRANSFER BIT

Data is transferred from the ROM to the TMS5110A over the ADD8 pin. Toggling M0 instructs the ROM to transfer the next required bit. As the PDC is brought high during a Read Bit command, the TMS5110A toggles M0 and accepts the new bit into its four-bit buffer over the ADD8 pin. The first M0 after a load address sequence changes the direction of the ADD8/Data line.

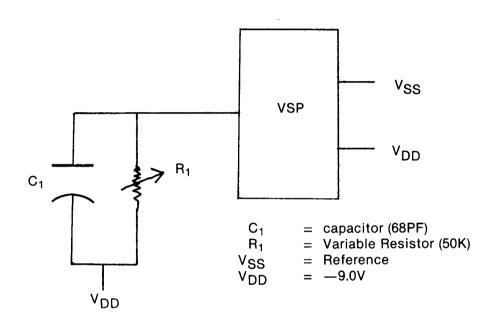

#### ROM CLOCK

The TMS5110A system oscillator clock is divided by four to generate ROMCLK, which is used as the input clock to the TMS6100/TMS6125. To achieve maximum speech quality ROMCLK must be adjusted to match the data rate at which the particular TMS6100/TMS6125 vocabulary was processed. A 40 hertz frame rate requires ROMCLK to be  $160 \pm 5\%$  kHz.

FIGURE 2 - OPERATION FLOW - READ/OUTPUT COMMAND SEQUENCE

## 4. TMS5110A SPECIFICATIONS

## 4.1 ABSOLUTE MAXIMUM RATINGS\* OVER OPERATING FREE-AIR TEMPERATURE RANGE (UNLESS OTHERWISE NOTED)

| Supply Voltage, VDD (see Note 1)  | -20 V to +0.3 V                       |

|-----------------------------------|---------------------------------------|

| Voltage applied to any device pin | -24 V to +0.3 V                       |

| Storage temperature               | $-30^{\circ}$ C to $+125^{\circ}$ C   |

| Operating temperature             | $0^{\circ}C \text{ to } +70^{\circ}C$ |

| Continuous power dissipation      | 60 <b>0</b> mW                        |

NOTE 1: All voltage values are with respect to  $\rm V_{SS}.$

\*Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or beyond those listed under the "Recommended Operating Conditions" section of this specification is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

#### 4.2 RECOMMENDED OPERATING CONDITIONS

| PARAMETER                                      | MIN             | NOM | MAX | UNIT |

|------------------------------------------------|-----------------|-----|-----|------|

| Supply voltage, V <sub>DD</sub>                | -8.3            | -9  | 9.7 | v    |

| High-level input voltage (see Note 2)          | -0.7            |     | 0   | V    |

| Low-level input voltage (see Note 2)           | V <sub>DD</sub> |     | -4  | V    |

| Oscillator frequency (external RC)             | 608             | 640 | 674 | kHz  |

| Operating free-air temperature, T <sub>A</sub> | 0               | 25  | 70  | °c   |

#### 4.3 ELECTRICAL CHARACTERISTICS OVER OPERATING FREE-AIR TEMPERATURE RANGE, VDD = -9 V

|                 | P                   | ARAMETER                        | TEST CONDITIONS             | MIN<br>(S | TYP MAX<br>ee Note 2) | UNIT |

|-----------------|---------------------|---------------------------------|-----------------------------|-----------|-----------------------|------|

| V               | High-level ADD8     |                                 |                             | -0.7      | 0                     |      |

| VIH             | input voltage       | CTL1, CTL2, CTL4, CTL8, PDC, CS |                             | -0.95     | 0                     | V    |

| VIL             | Low-level input vol | tage, all inputs                |                             | -12       | 4                     | V    |

|                 | High-level          | ROM CLK, CPU CLK, 10, 11,       | $I_{OH} = -100 \mu A$       | -0.5      | 0                     |      |

| ∨он             | output voltage      | ADD1, ADD2, ADD4, ADD8          | 100 1                       |           |                       | V    |

|                 |                     | CTL1, CTL2, CTL4, CTL8          | $I_{OH} = -400 \mu A$       | -0.7      | 0                     |      |

| VOL             | Low-level output v  | oltage, all outputs             | OL = 100 μA                 | VDD       | 5                     | V    |

| ЧΗ              | High-level input cu | rrent                           | V <sub>1</sub> = 0 V        |           | 100                   | μA   |

| ЧĽ              | Low-level input cur | rrent                           | $V_1 = -12V$                |           | -50                   | μA   |

| 1 <sub>DD</sub> | Supply current      |                                 | All inputs and outputs open |           | -20 -35               | mA   |

|                 | D                   |                                 | 100-Ω speaker load,         |           |                       |      |

|                 | Power output to sp  |                                 | 50- $\Omega$ each output    | 30        |                       | mW   |

NOTE 2: The algebraic convention, where the more negative (less positive) limit is designated as minimum, is used in this data sheet for logic voltage levels only.

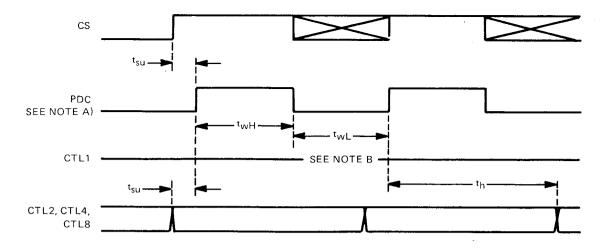

#### 4.4 TIMING REQUIREMENTS, DATA OUTPUT AND I/O MODE SWITCHING (TEST TALK, OUTPUT) SEE FIGURE 3

|                  | PARAMETER                                         | MIN MAX | UNIT               |

|------------------|---------------------------------------------------|---------|--------------------|

| t <sub>su</sub>  | CS setup time                                     | 0       | μs                 |

| <sup>t</sup> wH  | Pulse width, PDC high                             | 1       | cycle              |

| t <sub>w</sub> H | Pulse width, PDC high, f <sub>osc</sub> = 640 kHz | 6.25    | μs                 |

| twL              | Pulse width, PDC low                              | 1       | cycle <sup>‡</sup> |

| twL              | Pulse width, PDC low, f <sub>osc</sub> = 640 kHz  | 6.25    | μs                 |

<sup>†</sup> Typical values are at  $T_A = 25^{\circ}C$ .

<sup>†</sup> Cycle refers to the equivalent time in CPU clock cycles,

## 4.5 TIMING REQUIREMENTS, COMMAND AND DATA TRANSFER (LOAD ADDRESS, RESET, READ BIT, READY BRANCH, SPEAK) SEE FIGURE 4

|                 | PARAMETER                                         | MIN MAX | UNIT               |

|-----------------|---------------------------------------------------|---------|--------------------|

| t <sub>su</sub> | Data and CS setup time                            | 0       | μs                 |

| th              | Data hold time                                    | 1.75    | cycle <sup>‡</sup> |

| th              | Data hold time, f <sub>osc</sub> = 640 kHz *      | 10.9    | μs                 |

| twH             | Pulse width, PDC high                             | 1       | cycle <sup>‡</sup> |

| twH             | Pulse width, PDC high, f <sub>osc</sub> = 640 kHz | 6.25    | μs                 |

| twL             | Pulse width, PDC low                              | 1       | cycle <sup>‡</sup> |

| twL             | Pulse width, PDC low, f <sub>OSC</sub> = 640 kHz  | 6.25    | μs                 |

\* The system clock is set by using the ROM clock (160 kHz).

## 4.6 SWITCHING CHARACTERISTICS OVER OPERATING FREE-AIR TEMPERATURE RANGE, $V_{DD} = -9$

|                     | PARAMETER                    | TEST CONDITIONS            | MIN  | TYP <sup>†</sup> | MAX | UNIT               |

|---------------------|------------------------------|----------------------------|------|------------------|-----|--------------------|

| f <sub>osc</sub>    | Oscillator frequency         |                            | 608  | 640              | 674 | kHz                |

| td(D)               | Data output time             |                            | 1.25 |                  |     | cycle <sup>‡</sup> |

| td(D)               | Data output time             | f <sub>osc</sub> = 640 kHz | 7.8  |                  | 8.1 | μs                 |

| <sup>t</sup> d(1/0) | Output buffer switching time |                            | 1.25 |                  |     | cycle <sup>‡</sup> |

| <sup>t</sup> d(I/O) | Output buffer switching time | f <sub>osc</sub> = 640 kHz | 7.8  |                  | 8.1 | μs                 |

<sup>†</sup> Typical values are at  $T_A = 25^{\circ}C$ .

<sup>‡</sup> Cycle refers to the equivalent time in CPU clock cycles.

NOTES: A. Output buffers are enabled only while CS is high. Turn-on and turn-off delays are equivalent to 0.75 instruction cycle. B. For TEST TALK, only CTL1 is active.

#### FIGURE 3 - TIMING DIAGRAM, DATA OUTPUT AND I/O MODE SWITCHING

NOTES: A. Refer to command descriptions for PDC requirements.

B. CTL1 is irrelevant (don't care) for command transfer; same as CTL2, CTL4, CTL8 for address transfer.

FIGURE 4 - TIMING DIAGRAM, COMMAND AND DATA TRANSFER

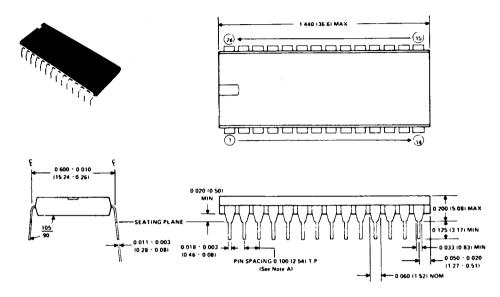

## 5. MECHANICAL DATA

#### 5.1 TMS 5110A - 28-PIN PLASTIC PACKAGE, .100" PIN CENTER SPACING, .600" PIN ROW SPACING

NOTES: a. Each pin centerline is located within 0.010 inch (0.26 millimeters) of its true longitudinal position. b. All linear dimensions are shown in inches (and parenthetically in millimeters for reference only). Inch dimensions govern.

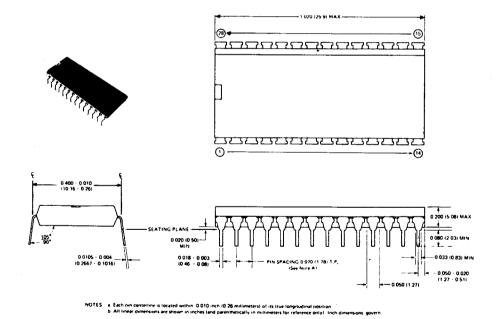

#### 5.2 TMS 5110A - 28 PIN PLASTIC PACKAGE, .070" PIN CENTER SPACING, .400" PIN ROW SPACING

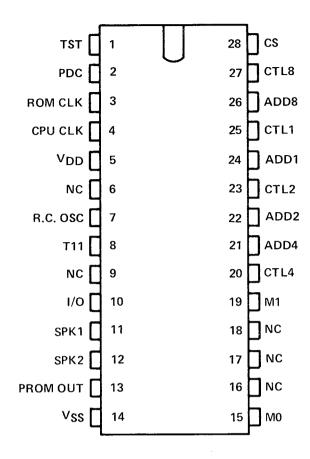

| PIN | NAME            | IN/OUT | FUNCTION                               |

|-----|-----------------|--------|----------------------------------------|

| 1   | TST             |        | For factory testing only               |

| 2   | PDC             | 1      | Processor data clock                   |

| 3   | RÓM CLK         | 0      | Clock to control TMS6100 ROM (160 kHz) |

| 4   | CPU CLK         | 0      | Output clock for CPU (320 kHz)         |

| 5   | VDD             | 1      | Drain supply voltage (–9V NOM)         |

| 6   | NC              | I      | No connection                          |

| 7   | R.C. OSC.       | 1      | RC option pin (640 kHz)                |

| 8   | T11             |        | Sync for serial data out               |

| 9   | NC              | _      | No connection                          |

| 10  | 1/0             | 0      | Serial data out                        |

| 11  | SPK1            | 0      | Analog speech out                      |

| 12  | SPK2            | 0      | Analog speech out                      |

| 13  | PROM OUT        |        | Test                                   |

| 14  | V <sub>SS</sub> | I      | Substrate supply voltage (0 V NOM)     |

| 15  | MO              | 0      | Transfer data to VSP control           |

| 16  | NC              | _      | No connection                          |

| 17  | NC              |        | No connection                          |

| 18  | NC              | _      | No connection                          |

| 19  | M1              | 0      | Load address to VSM control            |

| 20  | CTL4            | 1/0    | Control/read data bus                  |

| 21  | ADD4            | 0      | Address to VSM                         |

| 22  | ADD2            | 0      | Address to VSM                         |

| 23  | CTL2            | I/O    | Control/read data bus                  |

| 24  | ADD1            | Ο      | Address to VSM (LSB)                   |

| 25  | CTL1            | I/O    | Control/read data bus (LSB)            |

| 26  | ADD8            | 1/0    | Address to VSM/data to VSP (MSB)       |

| 27  | CTL8            | I/O    | Control/read data bus (MSB)            |

| 28  | CS              | I      | Chip select                            |

#### APPENDIX

## SYSTEM CLOCKS\*

## TABLE A-1 - A COMPARISON OF SYSTEM TIMES

| SAMPLE RATE:           | 10 kHz         | 8 kHz     |

|------------------------|----------------|-----------|

| FRAME RATE             | 50 Hz          | 40 Hz     |

| FRAME PERIOD           | 20 ms          | 25 ms     |

| INTERPOLATION RATE     | 400 Hz         | 320 Hz    |

| INTERPOLATION INTERVAL | 2.5 ms         | 3.125 ms  |

| SAMPLE RATE            | 10 kHz         | 8 kHz     |

| SAMPLE PERIOD          | 100 µs         | 125 μs    |

| ROM CLOCK RATE         | 200 kHz        | 160 kHz   |

| ROM CLOCK PERIOD       | 5 µs           | 6.25 μs   |

| RC OSC RATE            | 800 kHz        | 640 kHz   |

| RC OSC PERIOD          | <b>1250</b> ns | 1562.5 ns |

NOTE: All timing references in this data manual are based on an 8-kHz sample rate.