As you are now the owner of this document which should have come to you for free, please consider making a donation of £1 or more for the upkeep of the (Radar) website which holds this document. I give my time for free, but it costs me money to bring this document to you. You can donate here <u>https://blunham.com/Misc/Texas</u>

Many thanks.

Please do not upload this copyright pdf document to any other website. Breach of copyright may result in a criminal conviction.

This Acrobat document was generated by me, Colin Hinson, from a document held by me. I requested permission to publish this from Texas Instruments (twice) but received no reply. It is presented here (for free) and this pdf version of the document is my copyright in much the same way as a photograph would be. If you believe the document to be under other copyright, please contact me.

The document should have been downloaded from my website <u>https://blunham.com/</u>, or any mirror site named on that site. If you downloaded it from elsewhere, please let me know (particularly if you were charged for it). You can contact me via my Genuki email page: <u>https://www.genuki.org.uk/big/eng/YKS/various?recipient=colin</u>

You may not copy the file for onward transmission of the data nor attempt to make monetary gain by the use of these files. If you want someone else to have a copy of the file, point them at the website. (<u>https://blunham.com/Misc/Texas</u>). Please do not point them at the file itself as it may move or the site may be updated.

It should be noted that most of the pages are identifiable as having been processed by me.

If you find missing pages, pages in the wrong order, anything else wrong with the file or simply want to make a comment, please drop me a line (see above).

It is my hope that you find the file of use to you.

Colin Hinson In the village of Blunham, Bedfordshire.

I put a lot of time into producing these files which is why you are met with this page when you open the file.

J.

TEXAS INSTRUMENTS

# TM 990

## TM 990/303B Floppy-Disk Controller

## **MICROPROCESSOR SERIES™**

**User's Guide**

Leasnil Unical

#### TABLE OF CONTENTS

| SEC | <b>FION</b>                                                         | TITLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PAGE                                                                                 |

|-----|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| 1.  | INTRO                                                               | DUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                      |

|     | 1.1<br>1.2<br>1.3<br>1.4<br>1.5                                     | General.<br>Features.<br>Manual Organization<br>Typical System Configuration.<br>Power.<br>1.5.1 TM 990/303B Power Requirements.<br>1.5.2 Disk Drive DC Power Requirements.<br>Environment.                                                                                                                                                                                                                                                                                          | 1-2<br>1-5<br>1-5<br>1-6<br>1-6<br>1-7<br>1-7                                        |

|     | 1.7                                                                 | Applicable Documents                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1-7                                                                                  |

| 2.  | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10 | ALLATION AND OPERATION<br>General<br>Unpacking.<br>Required Equipment.<br>Jumpers on TM 990/303B Module.<br>Jumpers on Disk Drives.<br>Module Installation.<br>Cabling.<br>System Check and Power Application.<br>Onboard LED Error Check.<br>Two or More TM 990/303B Modules in a System.<br>2.10.1 Bus Access Arbitration.<br>2.10.2 Unique CRU Address Required for Each Module.<br>Demonstration Program.                                                                        | 2-1<br>2-2<br>2-2<br>2-6<br>2-7<br>2-10<br>2-10<br>2-10<br>2-11<br>2-12              |

| 3.  | COMM                                                                | JNICATING WITH THE TM 990/303B DISK CONTROLLER                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                      |

| -   | 3.1<br>3.2<br>3.3                                                   | General<br>Considerations.<br>Communication through the CRU (Software Base Address 210 <sub>16</sub> )<br>3.3.1 Output to Disk Controller over CRU<br>3.3.1.1 Command List Address Byte (Bits 0-7)<br>3.3.1.2 COMMAND Bit (Bit 8)<br>3.3.1.3 CUE Bit (Bit 10).<br>3.3.1.4 INTERRUPT ENABLE Bit (Bit 13)<br>3.3.1.5 RESET Disk Controller Bit (Bit 14)                                                                                                                                | 3-2<br>3-5<br>3-11<br>3-11<br>3-11<br>3-11<br>3-11<br>3-11<br>3-11                   |

|     |                                                                     | <pre>3.3.2 Input from Disk Controller over CRU<br/>3.3.2.1 ACCEPT Bit (Bit 11)<br/>3.3.2.2 BUSY Bit (Bit 12)<br/>3.3.2.3 INTERRUPT ISSUED Bit (Bit 15)</pre>                                                                                                                                                                                                                                                                                                                         | 3-12<br>3-12                                                                         |

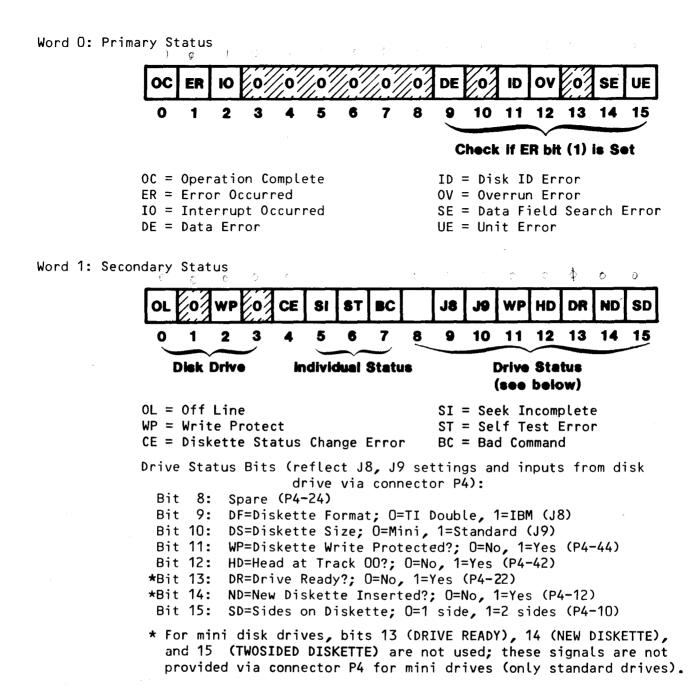

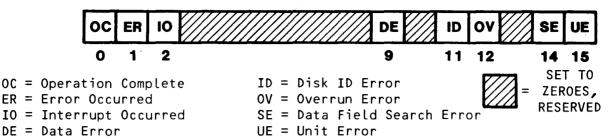

|     | 3.4                                                                 | Communication through Memory (Command List)<br>3.4.1 Word O, Primary Status and Error Indicator Word<br>3.4.1.1 Word O, Bit O, Operation Complete (OC)<br>3.4.1.2 Word O, Bit 1, Error Occurred (ER)<br>3.4.1.3 Word O, Bit 2, Interrupt Occurred (IO)<br>3.4.1.4 Word O, Bit 9, Data Error (DE)<br>3.4.1.5 Word O, Bit 11, Disk ID Error (ID)<br>3.4.1.6 Word O, Bit 12, Overrun Error (OV)<br>3.4.1.7 Word O, Bit 14, Search Error (SE)<br>3.4.1.8 Word O, Bit 15, Unit Error (UE) | 3-13<br>3-17<br>3-17<br>3-17<br>3-17<br>3-17<br>3-18<br>3-18<br>3-18<br>3-18<br>3-18 |

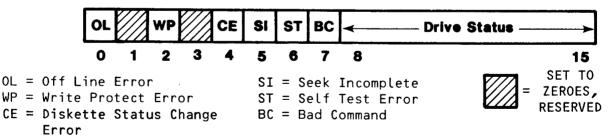

|     |                                                                     | 3.4.2 Word 1, Secondary Status and Error Indicator Word                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-18                                                                                 |

TITLE

|    |            | 3.4.2.1 Word 1, Bit 0, Unit Off Line Status (OL)<br>3.4.2.2 Word 1, Bit 2, Write Protect Status (WP)<br>3.4.2.3 Word 1, Bit 4, Diskette Status Change Error (CE)<br>3.4.2.4 Word 1, Bit 5, Seek Incomplete Error (SI) | 3–19<br>3–20<br>3–20 |

|----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|    |            | 3.4.2.5 Word 1, Bit 6, Self Test Error (ST)                                                                                                                                                                           | 3-20<br>3-20         |

|    |            | 3.4.2.7 Word 1, Bits 8 to 15, Drive Status                                                                                                                                                                            | 3-21                 |

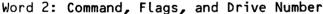

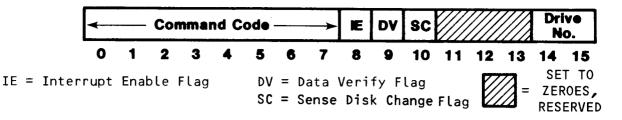

|    |            | 3.4.3 Word 2, Commands, Flags, and Drive No 3                                                                                                                                                                         | 3-22                 |

|    |            | 3.4.3.1 Word 2, Bits 0 to 7, Command Code 3                                                                                                                                                                           | 3-22                 |

|    |            | 3.4.3.2 Word 2, Bit 8, Interrupt Enable Flag                                                                                                                                                                          | 3-22                 |

|    |            | 3.4.3.3 Word 2, Bit 9, Data Verify Flag                                                                                                                                                                               | 3-22                 |

|    |            | 3.4.3.4 Word 2, Bit 10, Sense Disk Change Flag 3<br>3.4.3.5 Word 2, Bits 14 and 15, Drive ID                                                                                                                          | 3-22                 |

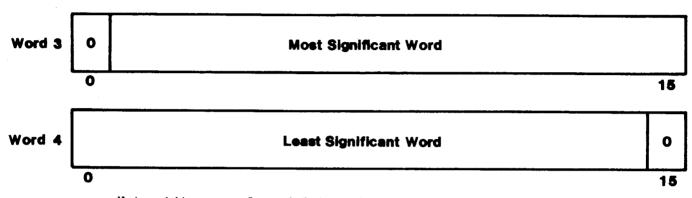

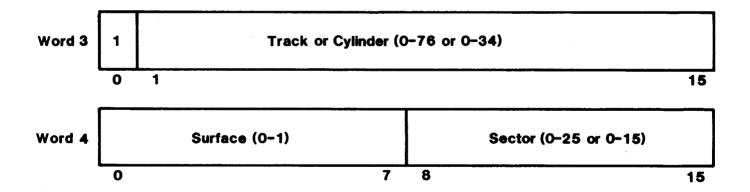

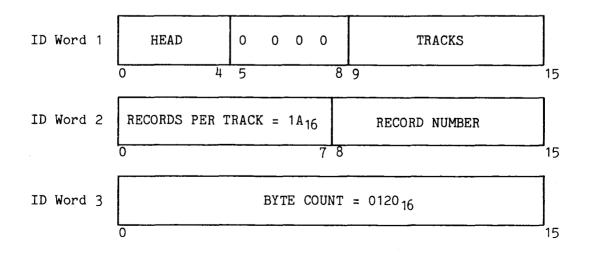

|    |            | 3.4.4 Words 3 and 4, Storage Address on Diskette                                                                                                                                                                      | 5-22                 |

|    |            | 3.4.4.1 Mass Storage Mode                                                                                                                                                                                             |                      |

|    |            | 3.4.4.2 Physical Storage Mode                                                                                                                                                                                         |                      |

|    |            | 3.4.5 Word 5, Byte Count                                                                                                                                                                                              |                      |

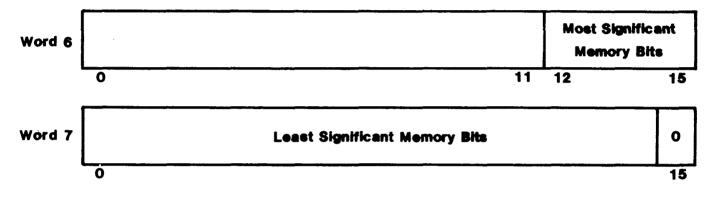

|    |            | 3.4.6 Words 6 and 7, Memory Address of Data to Transfer 3                                                                                                                                                             |                      |

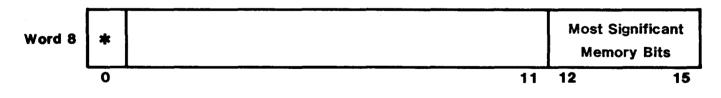

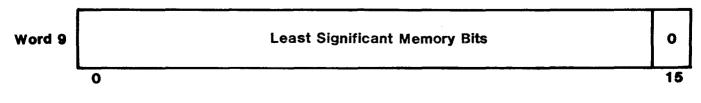

|    |            | 3.4.7 Words 8 and 9, Chain Address of Next Command List 3                                                                                                                                                             |                      |

|    | 3.5        | Communication through Interrupts 3                                                                                                                                                                                    |                      |

|    |            | 3.5.1 Command Completion Interrupt from Disk Controller to Host 3                                                                                                                                                     | 3-43                 |

|    |            | 3.5.2 Initiate Command Execution Interrupt from Host                                                                                                                                                                  |                      |

|    | 3.6        | to Disk Controller                                                                                                                                                                                                    |                      |

|    | 3.0        | Powerup Bootstrap Load Option                                                                                                                                                                                         |                      |

|    |            | 3.6.1 General                                                                                                                                                                                                         |                      |

|    |            | 3.6.3 Tests Performed at Bootload                                                                                                                                                                                     | 2_10                 |

|    |            | 3.6.4 Formats Supported for Bootload                                                                                                                                                                                  |                      |

|    |            | 3.6.5 Conditions That Can Lock Up System at Bootstrap Load 3                                                                                                                                                          |                      |

| 4. | HARD       | WARE DESCRIPTION                                                                                                                                                                                                      |                      |

|    | 4.1        | General                                                                                                                                                                                                               |                      |

|    | 4.2        | System Description 4                                                                                                                                                                                                  |                      |

|    | 4.3        | Controller Description                                                                                                                                                                                                |                      |

|    | 4.4        | Local Processor System                                                                                                                                                                                                |                      |

|    | 4.5<br>4.6 | Disk Drive Interface                                                                                                                                                                                                  | -                    |

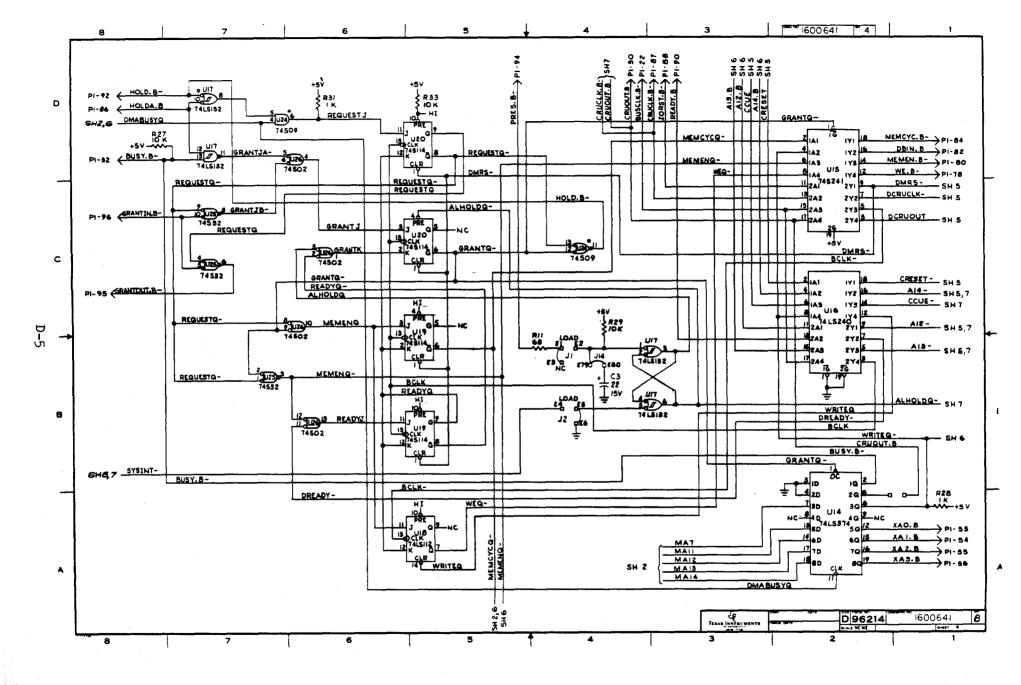

|    | 4.0        | Host System Interface                                                                                                                                                                                                 | +-0<br>+-8           |

|    |            | 4.6.2 Host System DMA Interface                                                                                                                                                                                       |                      |

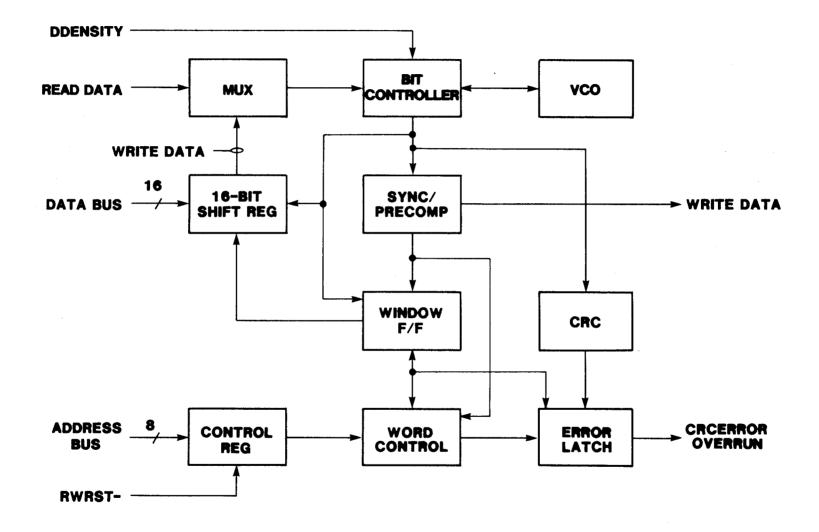

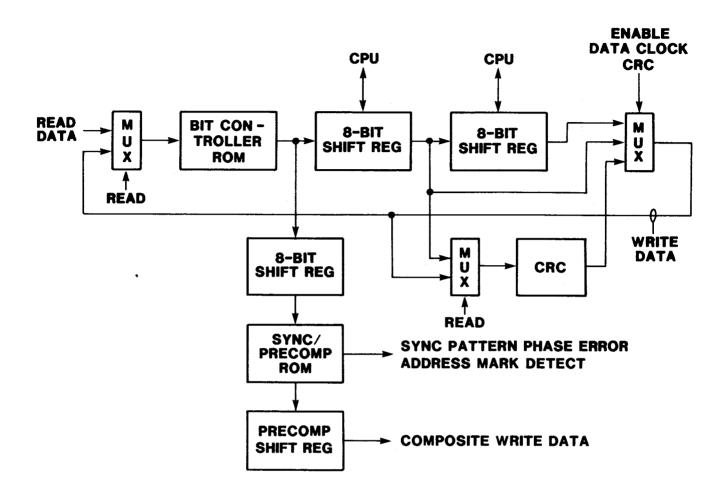

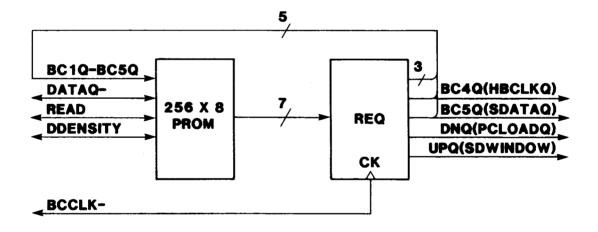

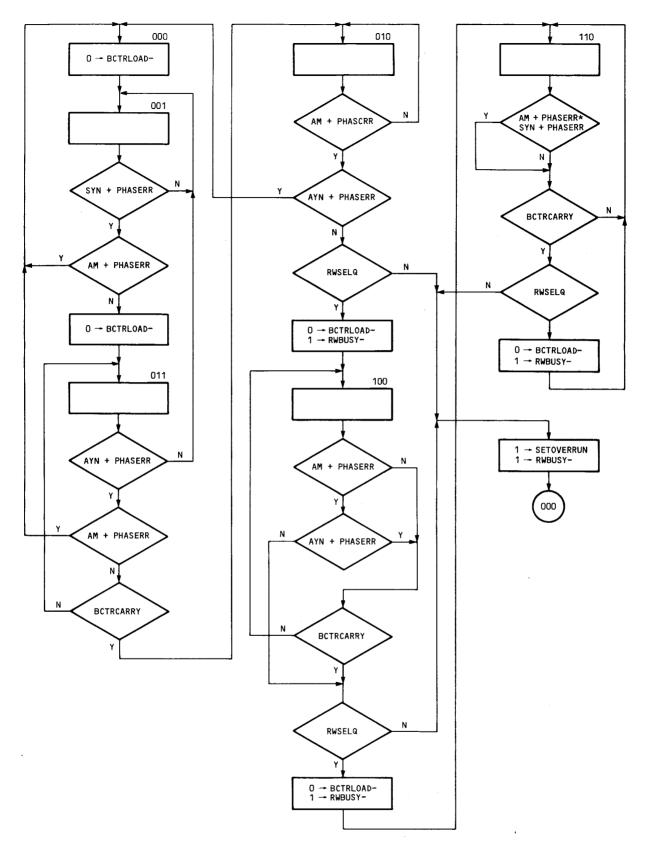

|    | 4.7        | Read/Write Controller                                                                                                                                                                                                 |                      |

|    |            | 4.7.1 Read/Write Data Path                                                                                                                                                                                            |                      |

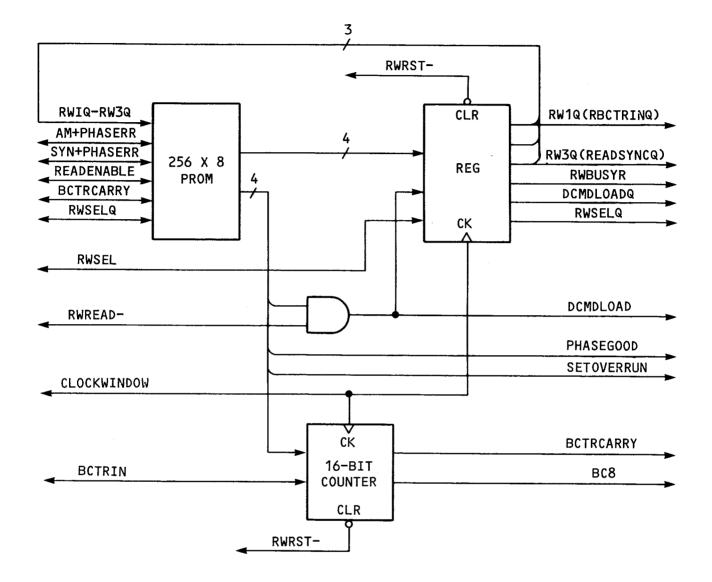

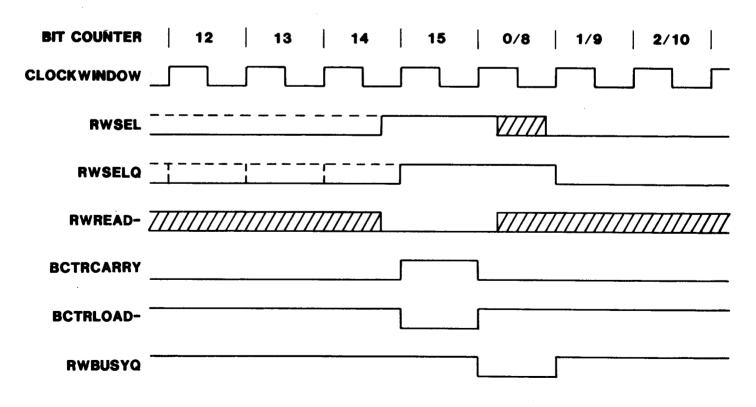

|    |            | 4.7.2 Bit Controller                                                                                                                                                                                                  |                      |

|    |            |                                                                                                                                                                                                                       | 1-29                 |

|    |            | 4.7.4 Precompensation 4                                                                                                                                                                                               | -                    |

|    |            | 4.7.5 Word Controller 4                                                                                                                                                                                               | <b>1-</b> 32         |

|    |            | 4.7.6 Control of Read and Write Operations 4                                                                                                                                                                          |                      |

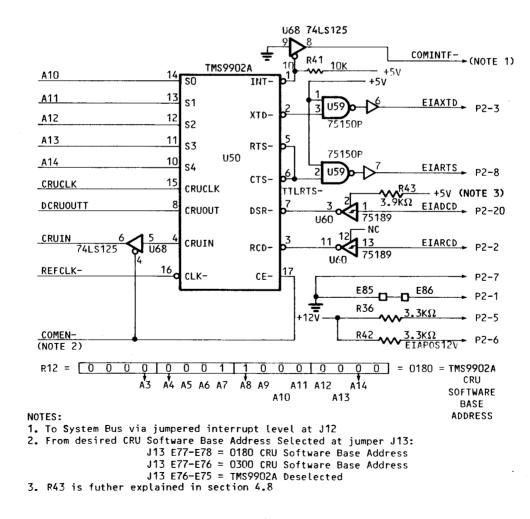

|    | 4.8        | EIA Port                                                                                                                                                                                                              |                      |

|    |            | 4.8.1 Changing the CRU Address of the EIA Port                                                                                                                                                                        |                      |

|    |            | 4.8.2 EIA Port DTR/DSR Signals Affected by R43 4                                                                                                                                                                      | 1-40                 |

#### SECTION

#### TITLE

| 5. | PROG | AMMING TMS 9902A EIA PORT CONTROLLER AT PORT P2               |

|----|------|---------------------------------------------------------------|

|    | 5.1  | General                                                       |

|    | 5.2  | Address Structure of the CRU 5-2                              |

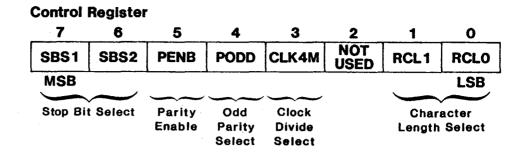

|    | 5.3  | Loading the Principal Internal Registers of the TMS 9902A 5-4 |

|    |      | 5.3.1 Principal Registers of the TMS 9902A 5-4                |

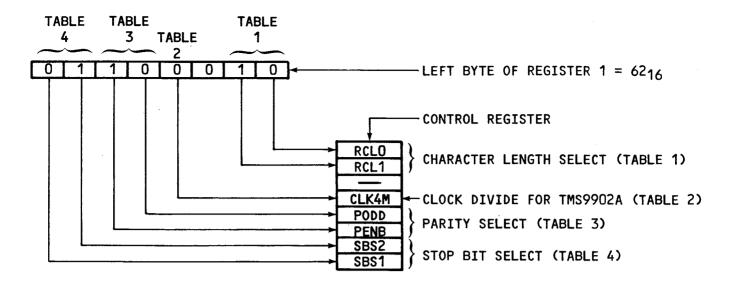

|    |      | 5.3.2 Programming the Control Register                        |

|    |      | 5.3.3 Programming the Interval Register                       |

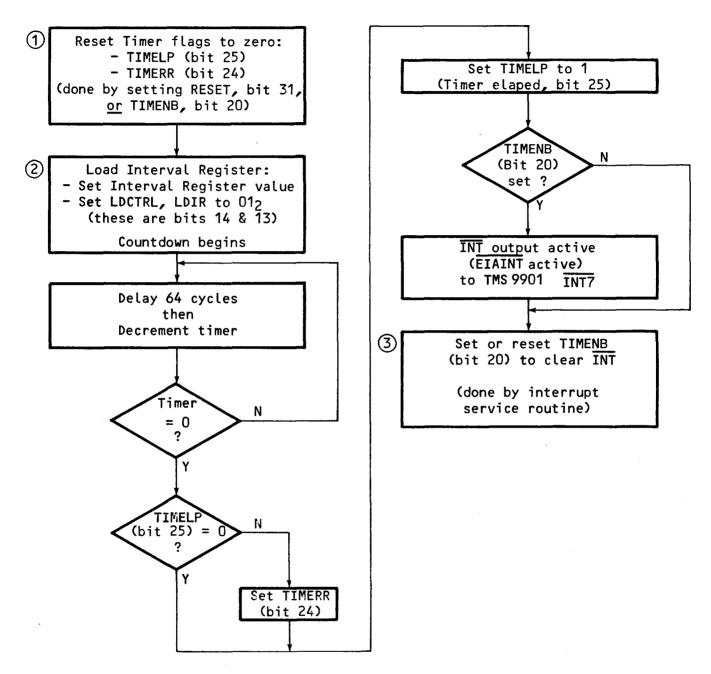

|     | 5.3.4   | Loading the Receive and Transmit Data Rate Registers | 5-9  |

|-----|---------|------------------------------------------------------|------|

|     | 5.3.5   | Ease in Sequentially Loading Several Registers       | 5-10 |

| 5.4 | Program | mming Examples                                       | 5-12 |

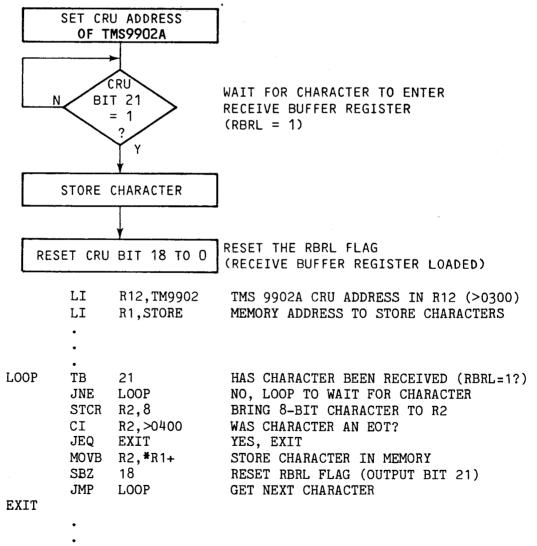

|     | 5.4.1   | Receive Character by Polling                         | 5-12 |

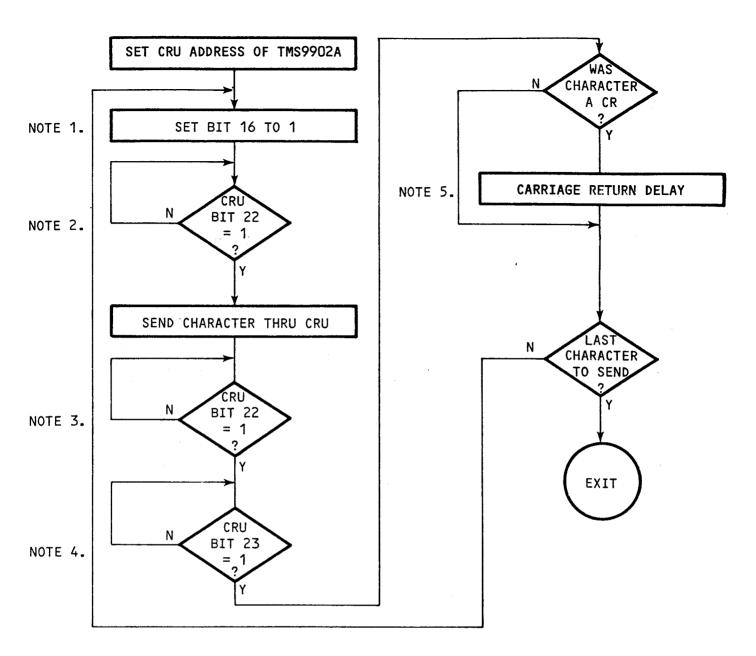

|     | 5.4.2   | Transmit Character(s) Through Port P2                | 5-13 |

|     | 5.4.3   | Programming the Interval Timer                       | 5-16 |

|     | 5.4.4   | Example Interrupt Operation to Receive Characters    | 5-18 |

|     | 5.4.5   | Program TMS 9902A, Then Echo Characters              | 5-21 |

|     |         |                                                      |      |

#### APPENDICES

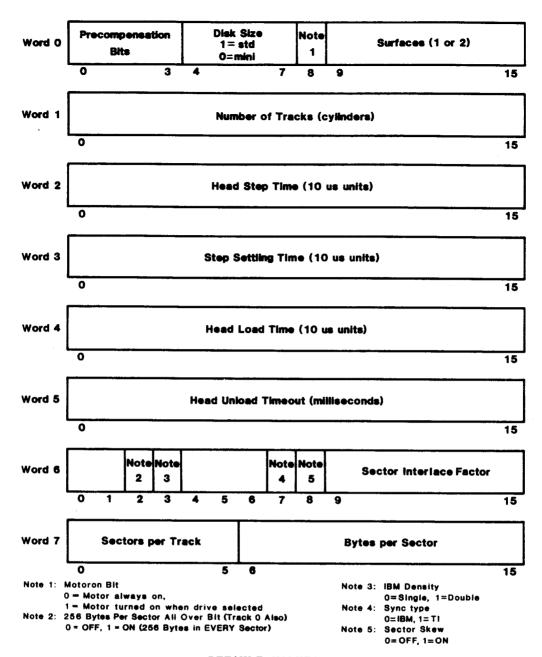

| A. DRIVE PARAMETER LIST ENTRIES AND DISK DRIVE JUMP |

|-----------------------------------------------------|

|-----------------------------------------------------|

| A.1  | Introduction                            | A-2         |

|------|-----------------------------------------|-------------|

| A.2  | CDC 9404B Eight Inch Disk Drive         | A-10        |

| A.3  | CDC 9406-4 Eight Inch Disk Drive        | A-13        |

| A.4  | Qume DT-8 Eight Inch Disk Drive         | <b>A-16</b> |

| A.5  | Shugart SA800 Eight Inch Disk Drive     | A-19        |

| A.6  | Shugart SA801 Eight Inch Disk Drive     | A-22        |

| Α.7  | Shugart SA851/850 Eight Inch Disk Drive | A-25        |

| A.8  | Siemens FDD100-8 Eight Inch Disk Drive  | A-28        |

| A.9  | Siemens FDD200-8 Eight Inch Disk Drive  | A-31        |

| A.10 | Tandon TM848-1 Eight Inch Disk Drive    | A-34        |

| A.11 | Tandon TM848-2 Eight Inch Disk Drive    | A-37        |

| A.12 | BASF 6106 Five Inch Disk Drive          | A-40        |

| A.13 | CDC 9408 Five Inch Disk Drive           | A-43        |

| A.14 | CDC 9409T Five Inch Disk Drive          | A-45        |

| A.15 | Qume DT-5 Five Inch Disk Drive          | A-47        |

| A.16 | Shugart SA400 Five Inch Disk Drive      | A-50        |

| A.17 | Shugart SA450 Five Inch Disk Drive      | A-53        |

| A.18 | Shugart SA410 Five Inch Disk Drive      | A-56        |

| A.19 | Shugart SA460 Five Inch Disk Drive      | A-59        |

| A.20 | Siemens FDD100-5 Five Inch Disk Drive   | A-62        |

| A.21 | Siemens FDD200-5 Five Inch Disk Drive   | A-65        |

| A.22 | Siemens FDD196-5 Five Inch Disk Drive   | A-68        |

| A.23 | Siemens FDD296-5 Five Inch Disk Drive   | A-71        |

|      | Tandon TM100-1 Five Inch Disk Drive     |             |

| A.25 | Tandon TM100-3 Five Inch Disk Drive     | A-76        |

| A.26 | Tandon TM100-4 Five Inch Disk Drive     | A-78        |

- B. DISK DRIVE SPECIFICATIONS

- C. DISKETTE TRACK FORMATS

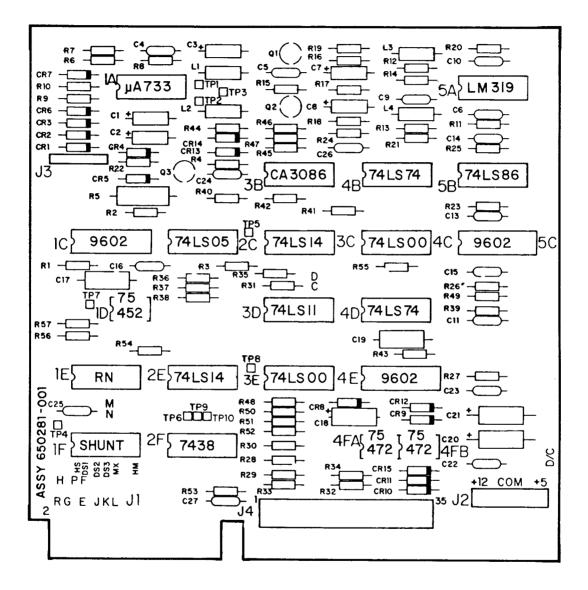

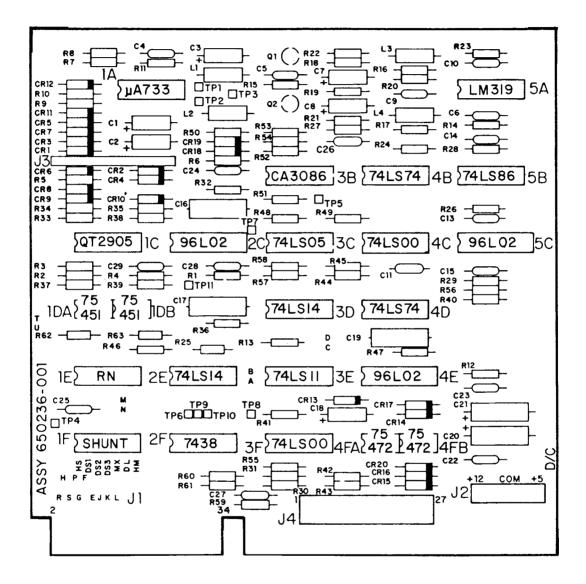

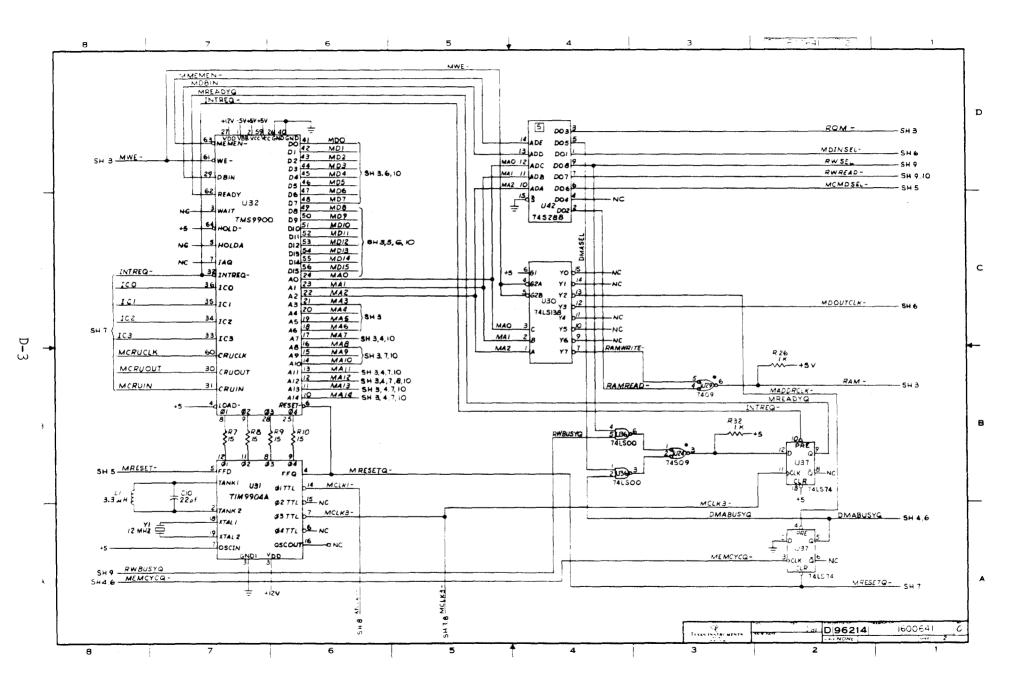

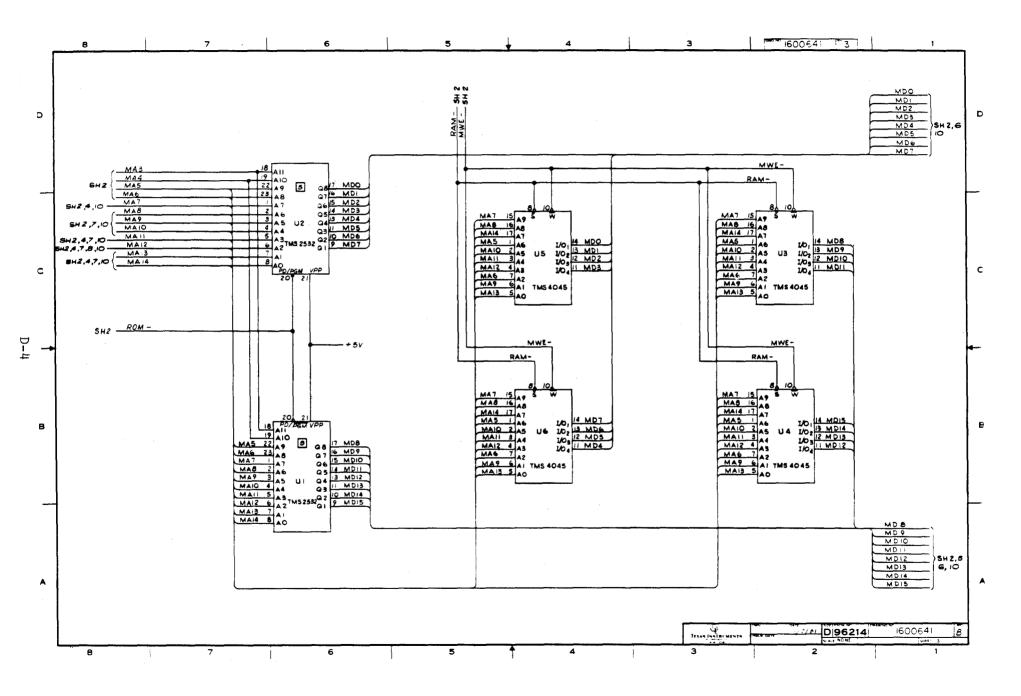

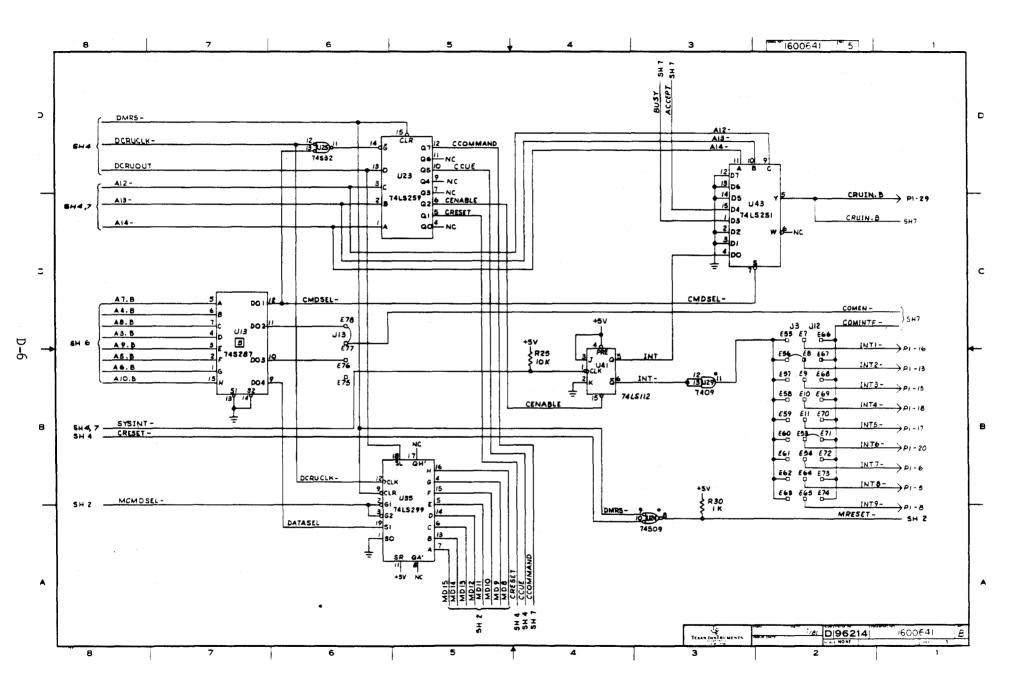

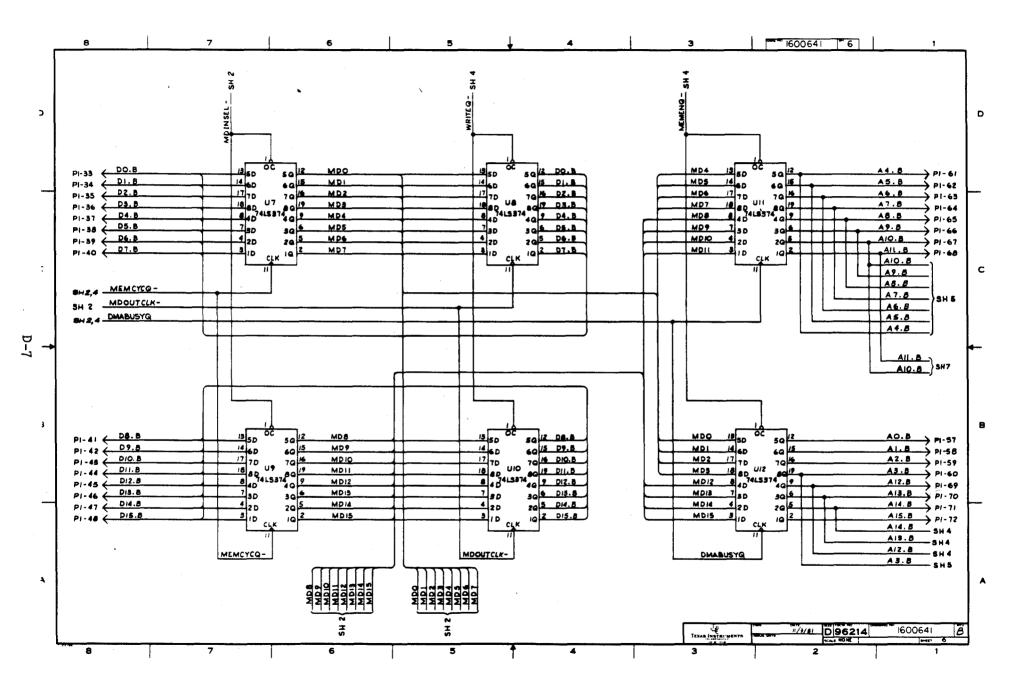

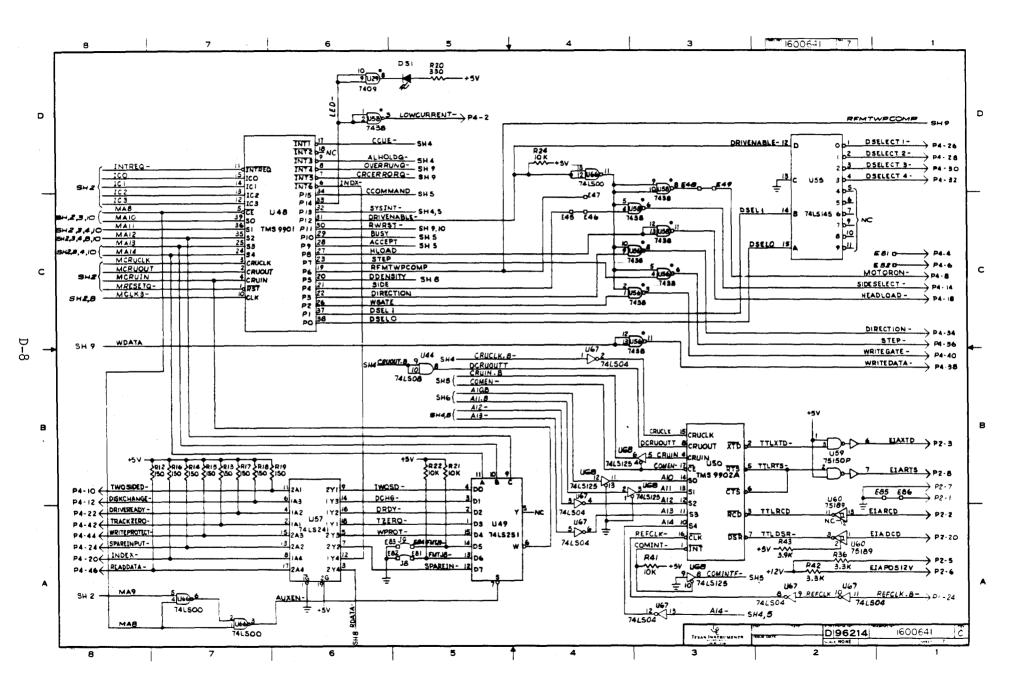

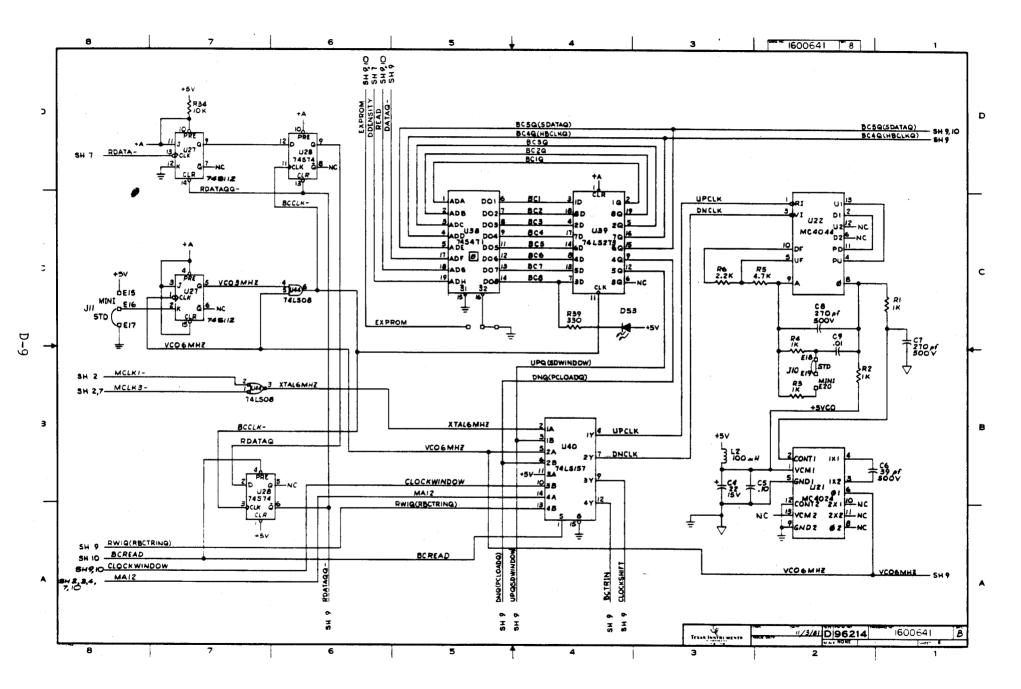

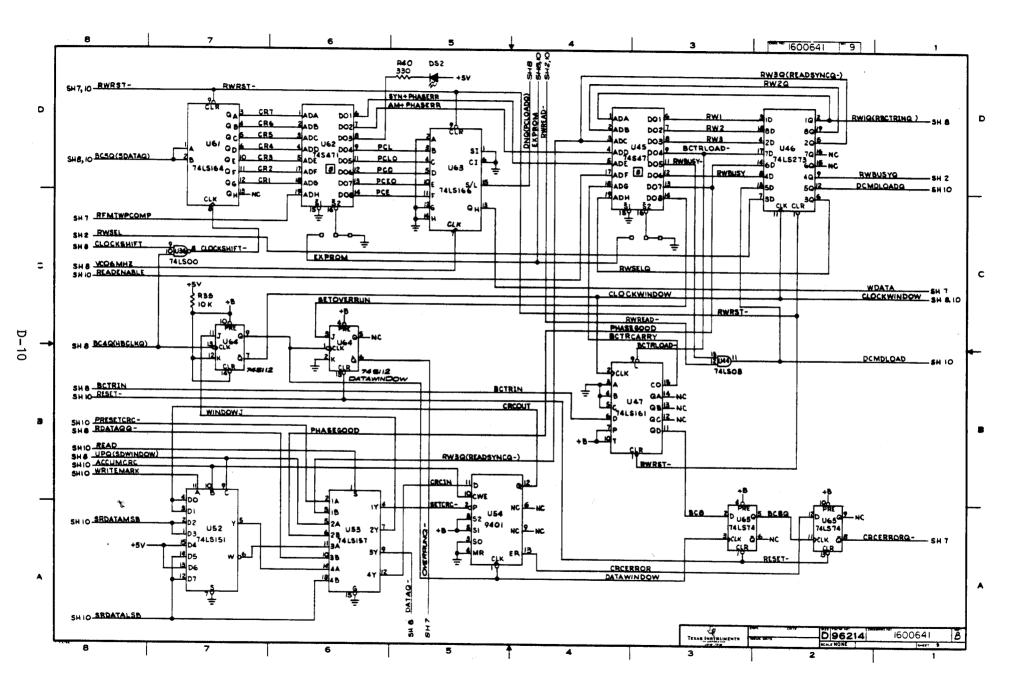

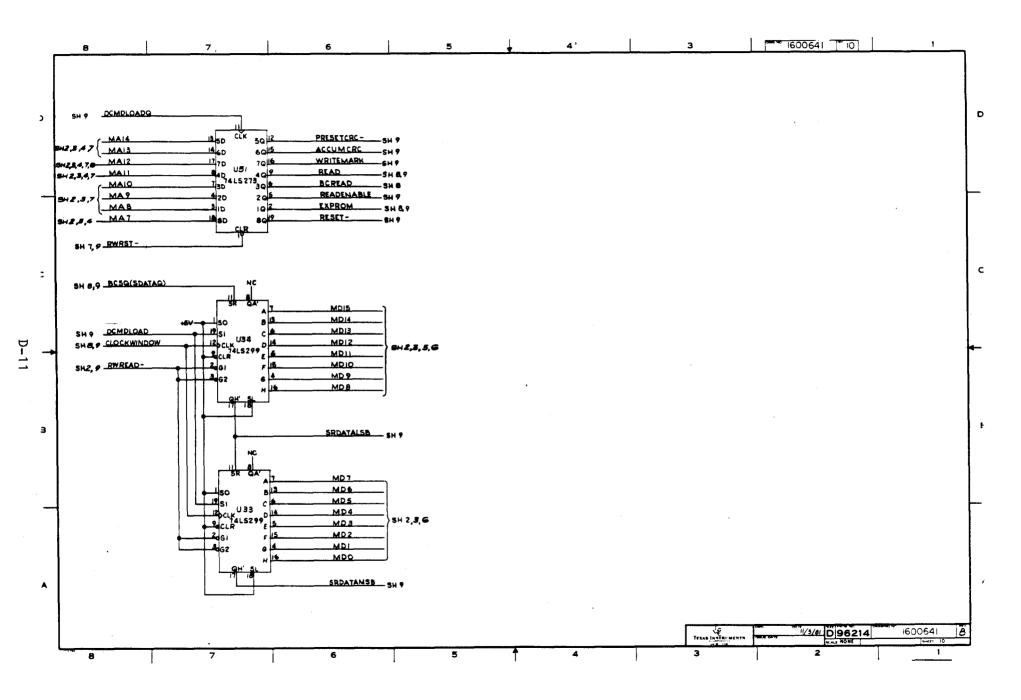

- D. SCHEMATICS

- E. PROGRAMMING PROM FOR UNIQUE CRU ADDRESS

- F. PIN LIST FOR CONTROLLER-TO-DRIVE CABLES

- G. PARTS LIST

#### LIST OF ILLUSTRATIONS

#### FIGURE

#### TITLE

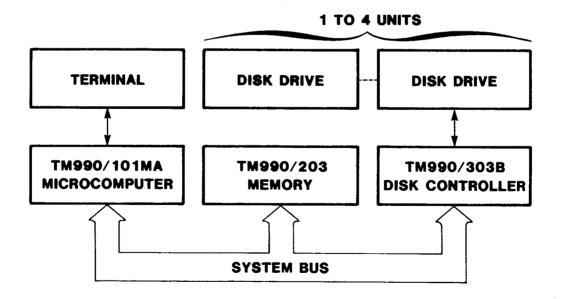

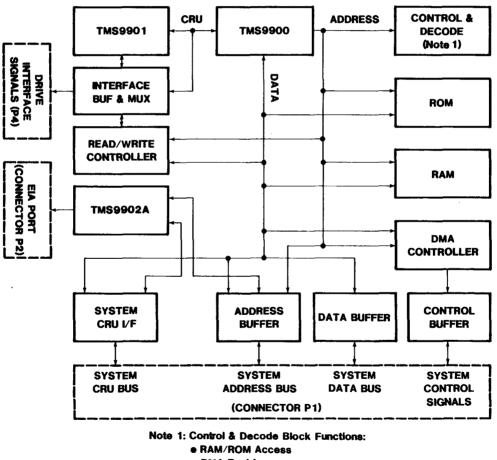

| 1-1<br>1-2<br>1-3                       | Principal Components of the TM 990/303B Module<br>TM 990/303B Block Diagram<br>Typical System Configuration Using Two Model 800 Disk Drives                                                                                                                                                           | 1-4                          |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 2-1<br>2-2<br>2-3<br>2-4                | TM 990/303B Jumper Locations<br>Location of Solder Bridge Between Pins 96 & 95 of Motherboard<br>System Interconnections Using TM 990/527 Cable<br>Connecting TM 990/527 Disk Drive Cable to P4 of TM 990/303B                                                                                        | 2-6<br>2-7                   |

| 2 <b>-</b> 5<br>2-6                     | Module.<br>TM 990/527 Cabling Between Controller and Eight-Inch Drives<br>Connecting TM 990/535B Disk Drive Cable to P4 of TM 990/303B                                                                                                                                                                | 2-8                          |

| 2-7<br>2-8<br>2-9                       | Module<br>TM 990/535B Cabling Between Controller and Mini Disk Drives<br>Substitute Code to Use a Mini Disk Drive<br>Demo Program to Read to/Write from Disk                                                                                                                                          | 2-9<br>2-14                  |

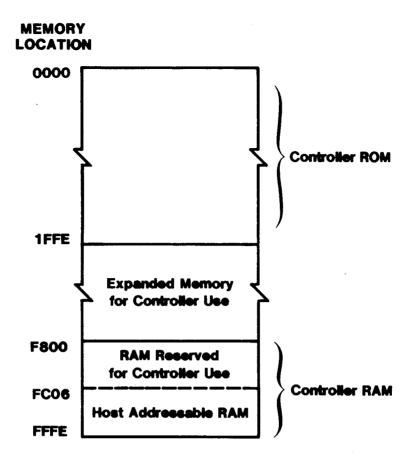

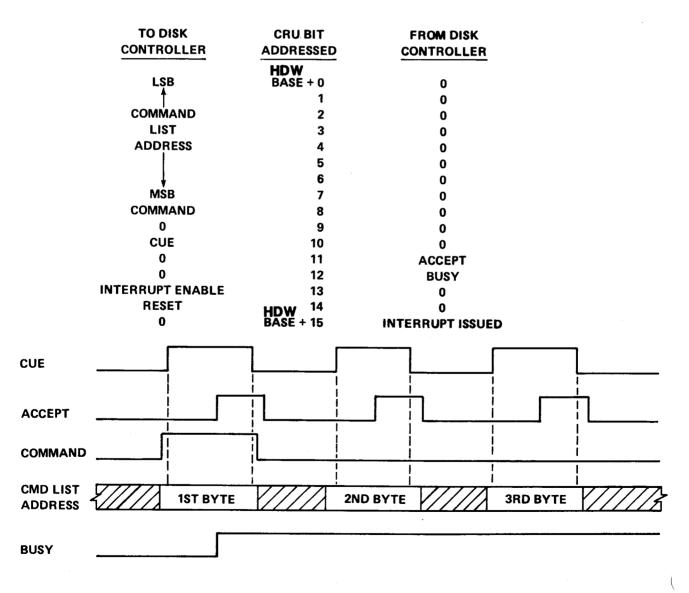

| 3-1<br>3-2<br>3-3<br>3-4                | Disk Controller Memory Map<br>CRU Interface and Timing<br>32-Bit CRU Interface Block as Shipped from Factory<br>Communication Between the Host and Disk Controller to Store                                                                                                                           | 3-6                          |

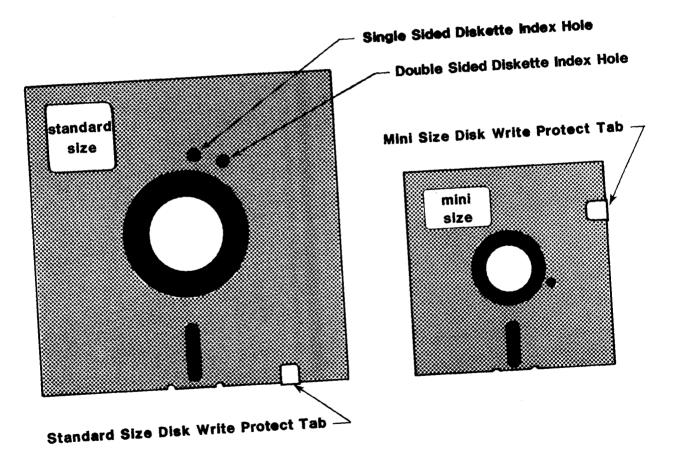

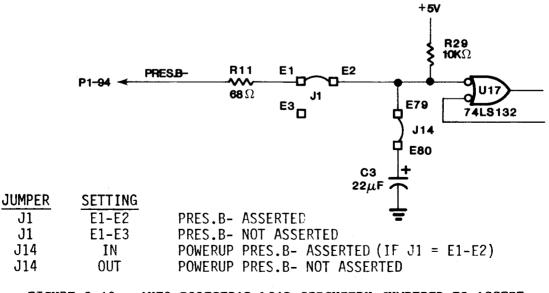

| 3-5<br>3-6<br>3-7<br>3-8<br>3-9<br>3-10 | Command List Address through the CRU.<br>Program to Pass Command List Address of OFE00 <sub>16</sub><br>Ten-Word Command List.<br>Write-Protect Tab on Diskette<br>Drive Parameter List.<br>Listing to Load Vectors for Interrupt Level 2<br>Auto Bootstrap Load Circuitry Jumpered to Assert PRES.B- | 3-10<br>3-15<br>3-19<br>3-38 |

|                                         | to Host CPU                                                                                                                                                                                                                                                                                           | 3-48                         |

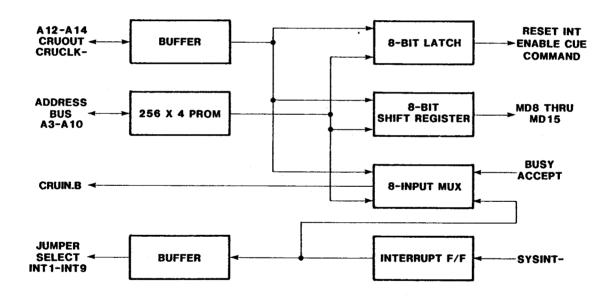

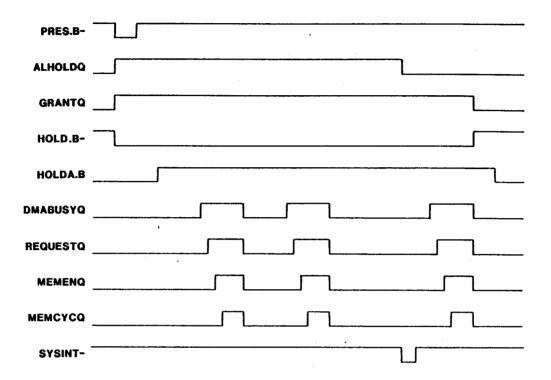

| 4-1<br>4-2<br>4-3<br>4-4<br>4-5         | Typical System Block Diagram.<br>Disk Controller Block Diagram.<br>System CRU Interface Block Diagram.<br>General-Purpose CRU Interface<br>DMA Memory Access Timing (1 Wait State).                                                                                                                   | 4-2<br>4-8<br>4-10<br>4-12   |

| 4-6<br>4-7<br>4-8<br>4-9                | DMA Timing - Automatic Bootload<br>Processor Memory Timing with Wait States<br>Read/Write Controller Block Diagram<br>Read/Write Data Path                                                                                                                                                            | 4-15<br>4-16<br>4-19         |

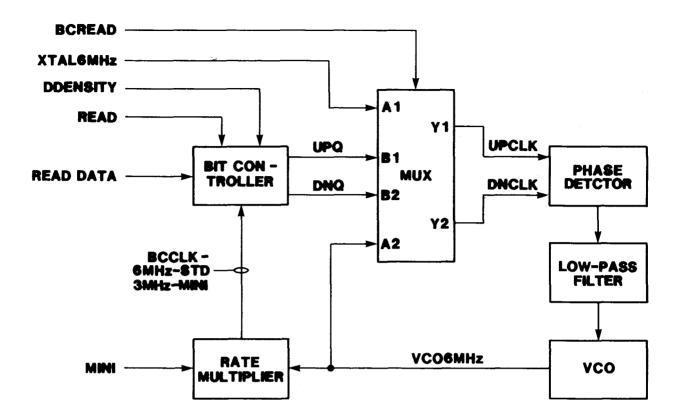

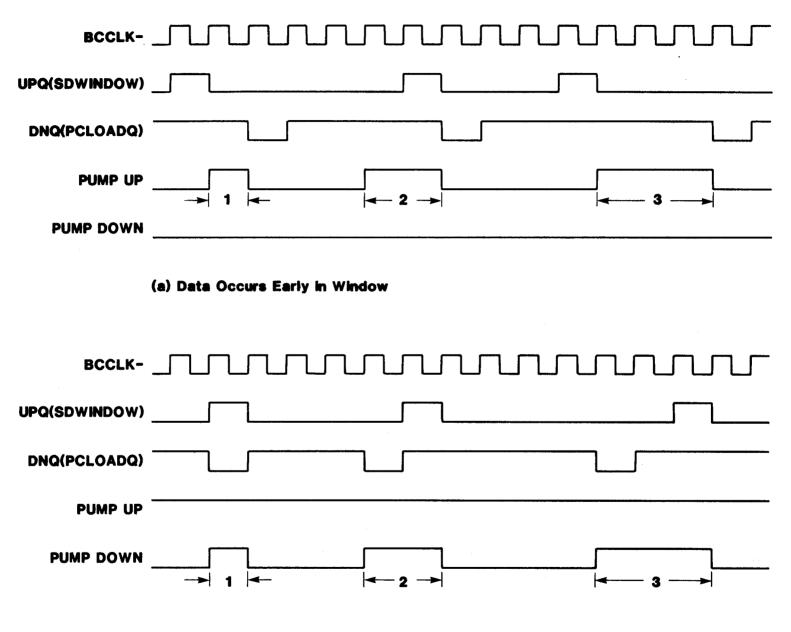

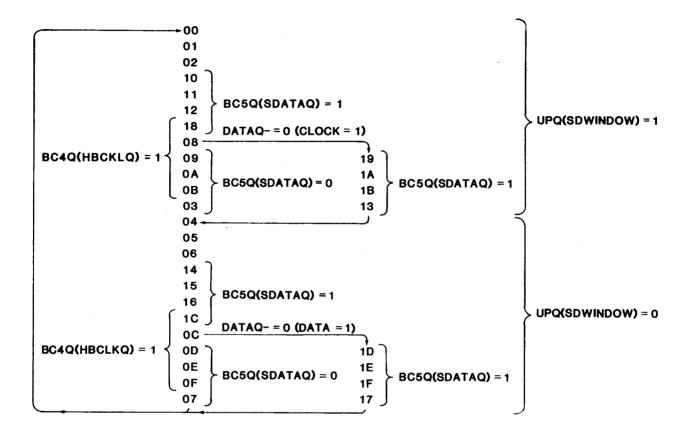

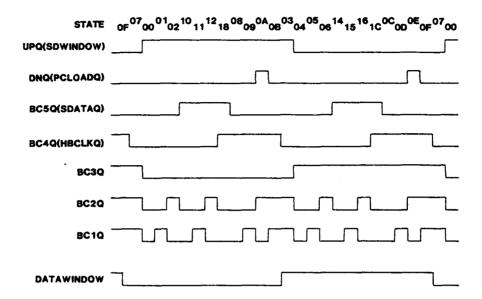

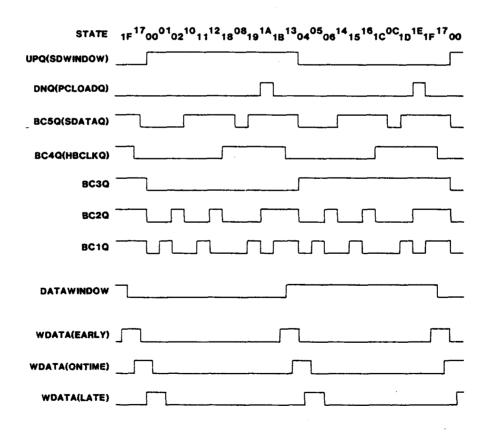

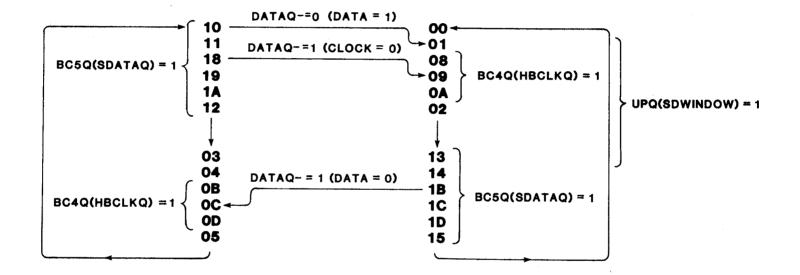

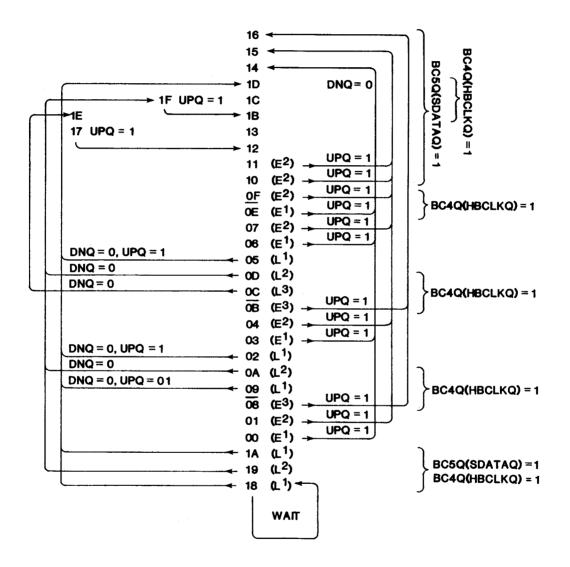

| 4-10<br>4-11<br>4-12<br>4-13            | Bit Controller Block Diagram<br>Phase-Locked Loop Block Diagram<br>Double Density Phase Detector Timing<br>Bit Controller Write FM State Diagram                                                                                                                                                      | 4-21<br>4-22                 |

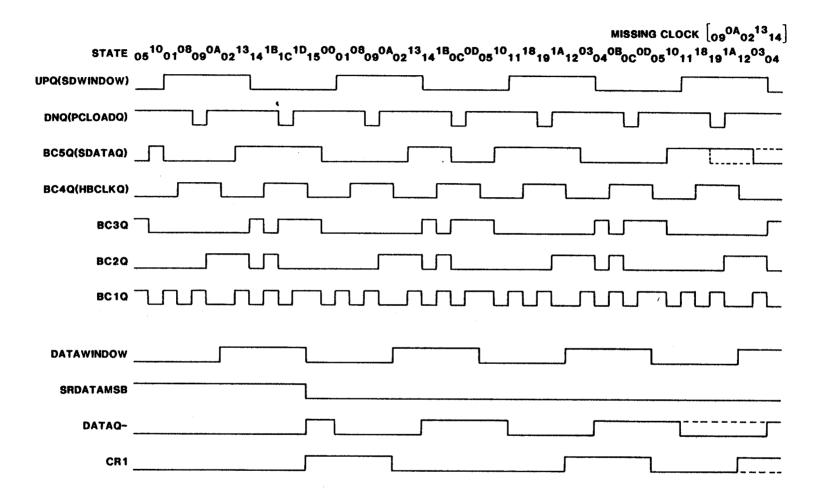

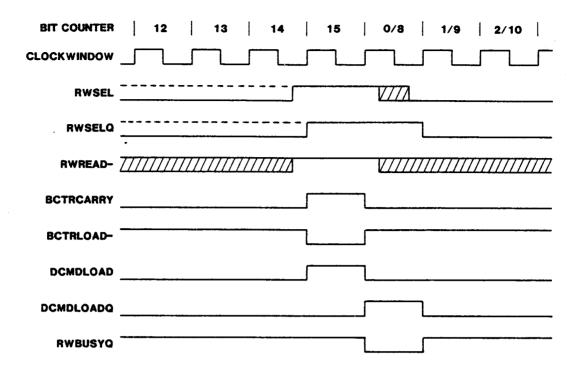

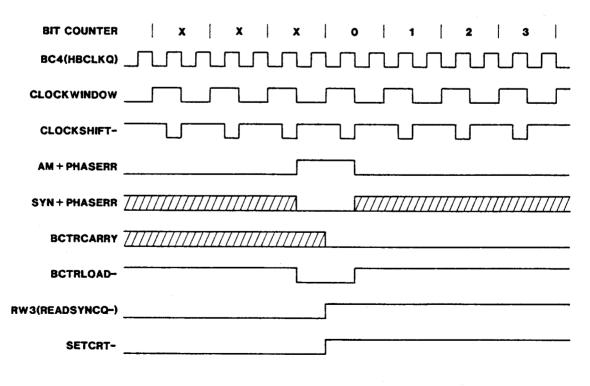

| 4-14<br>4-15<br>4-16<br>4-17            | Write FM Timing<br>Bit Controller Write MFM State Diagram<br>Write MFM<br>Bit Controller Read FM                                                                                                                                                                                                      | 4-25<br>4-26                 |

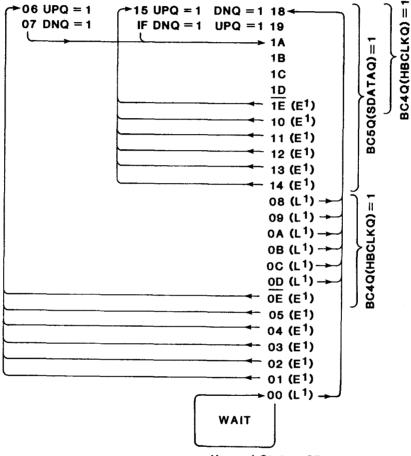

| 4-17<br>4-18<br>4-19<br>4-20            | Read MFM<br>Phase Error Recovery Timing Diagram<br>Precompensation Shift Register Timing                                                                                                                                                                                                              | 4–28<br>4–30                 |

| 4-21<br>4-22                            | Word Controller Read Mode Flowchart                                                                                                                                                                                                                                                                   | 4-33                         |

#### LIST OF ILLUSTRATIONS

#### FIGURE

#### TITLE

| 4-23 | Word Controller Read Timing                                    | 4-35          |

|------|----------------------------------------------------------------|---------------|

| 4-24 | Word Controller Write Timing                                   |               |

| 4-25 | Word Controller Read Timing-Address Mark Detect                | 4-36          |

| 4-26 | ID Field Write Timing - Single Density                         | 4-37          |

| 4-27 | ID Field Read Timing - Single Density                          |               |

| 4-28 | ID Field Write Timing - IBM Double Density                     | 4-38          |

| 4-29 | ID Field Read Timing - IBM Double Density                      | 4-39          |

| 4-30 | CRC Error Latch Timing                                         |               |

|      |                                                                |               |

| 5-1  | Interconnections to Port P2's TMS 9902A Controller             |               |

| 5-2  | TMS 9902A Programmable Registers                               |               |

| 5-3  | Loading the TMS 9902A Control Register                         |               |

| 5-4  | Coding to Load All Four TMS 9902A Registers                    |               |

| 5-5  | Receive Character(s) by Polling                                |               |

| 5-6  | Transmit Character(s) by Polling                               |               |

| 5-7  | Loading and Executing the Interval Timer Using Interrupts      |               |

| 5-8  | Example Program Using Interrupts to Receive Characters         |               |

| 5-9  | Coding to Set Up TMS 9902A and Echo Characters                 | 5 <b>-</b> 23 |

| A-1  | CDC 9404B Jumper Locations                                     | 4-11          |

| A-2  | CDC 9406-4 Jumper Locations.                                   |               |

| A-3  | Qume DT-8 Jumper Locations                                     |               |

| A-4  | Shugart SA800 Jumper Locations                                 |               |

| A-5  | Shugart SA801 Jumper Locations                                 |               |

| A-6  | Shugart SA851/850 Jumper Locations                             |               |

| A-7  | Siemens FDD100-8 Jumper Locations                              |               |

| A-8  | Siemens FDD200-8 Jumper Locations                              |               |

| A-9  | Tandon TM848-1 Jumper Locations                                |               |

| A-10 | Tandon TM848-2 Jumper Locations                                |               |

| A-11 | BASF 6106 Jumper Locations                                     | -             |

| A-12 | CDC 9408 Jumper Locations                                      |               |

| A-13 | CDC 9409T Jumper Locations                                     |               |

| A-14 | Qume DT-5 Jumper Locations                                     |               |

| A-15 | Shugart SA400 Jumper Locations                                 |               |

| A-16 | Shugart SA450 Jumper Locations                                 |               |

| A-17 | Shugart SA410 Jumper Locations                                 |               |

| A-18 | Shugart SA460 Jumper Locations                                 |               |

| A-19 | Siemens FDD100-5 Jumper Locations                              |               |

| A-20 | Siemens FDD200-5 Jumper Locations                              |               |

| A-21 | Siemens FDD196-5 Jumper Locations                              |               |

| A-22 | Siemens FDD296-5 Jumper Locations                              |               |

| A-23 | Tandon TM100-1 Jumper Locations                                |               |

| A-24 | Tandon TM100-3 Jumper Locations                                |               |

| A-25 | Tandon TM100-4 Jumper Locations                                |               |

|      |                                                                |               |

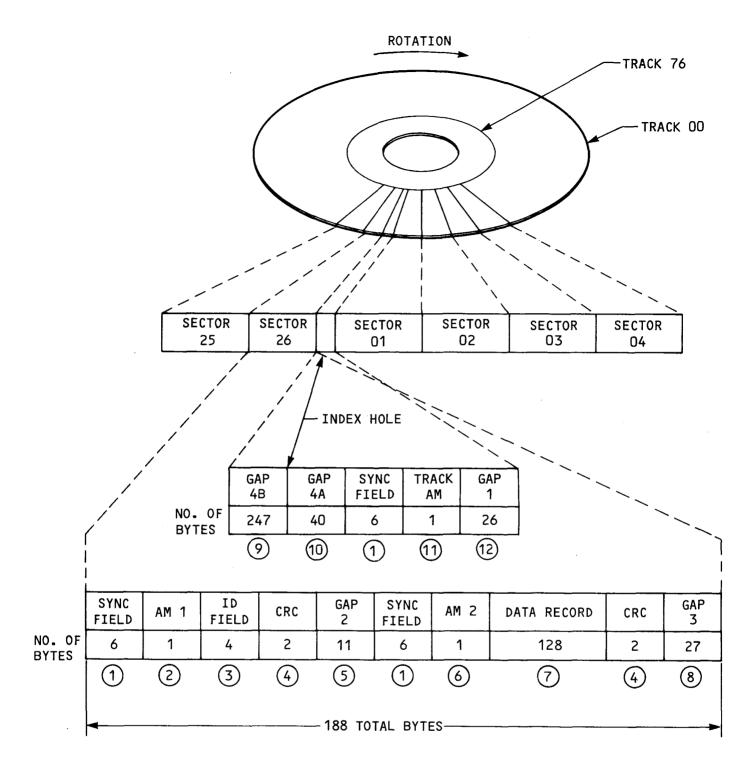

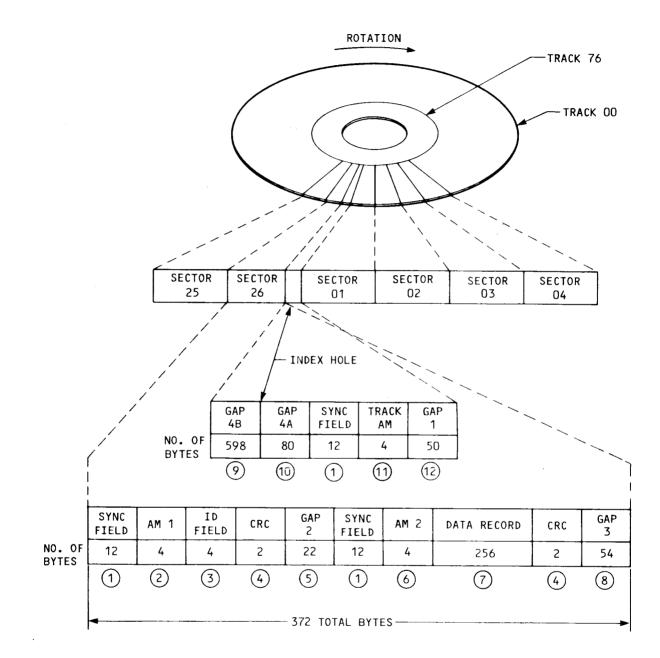

| C-1  | Standard-Size, Single-Density Track Format                     | C-3           |

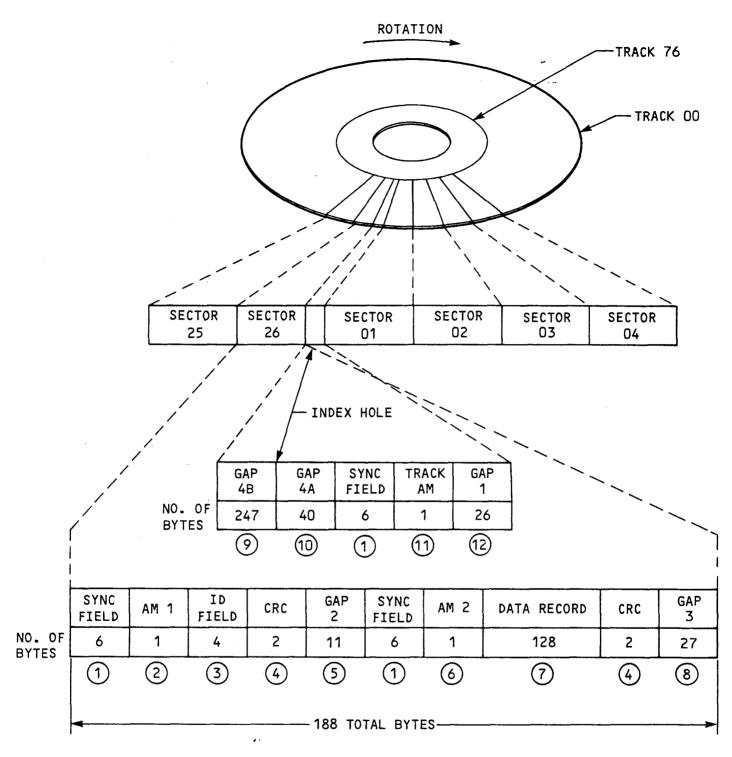

| C-2  | IBM-Compatible Standard-Size Double-Density Track Format       | C-4           |

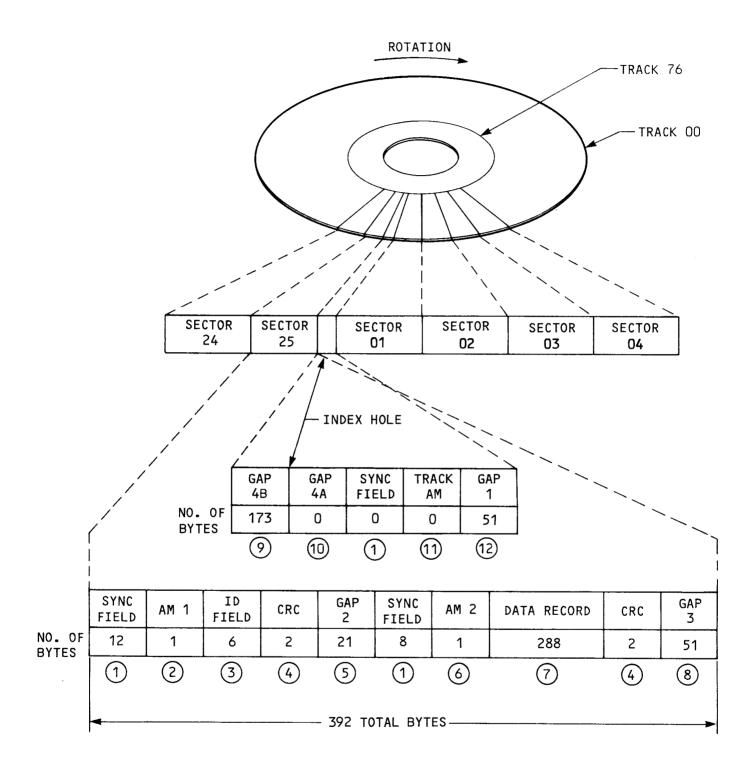

| C-3  | IBM-Compatible Standard Size Modified Double-Density Tk Format | C-6           |

| C-4  | TI-Compatible, Standard-Size, Double-Density Track Format      |               |

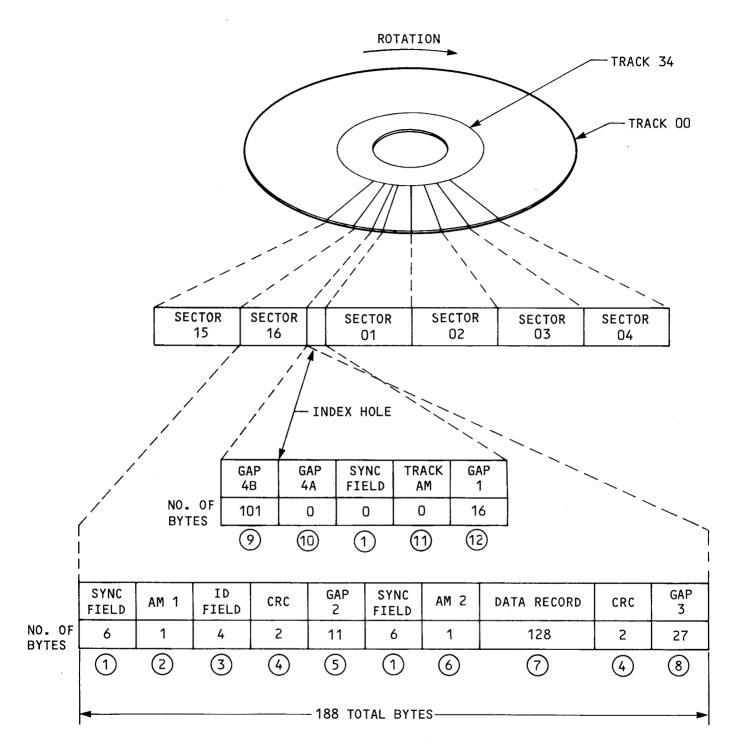

| C-5  | Mini-Size, Single-Density Track Format                         | C-8           |

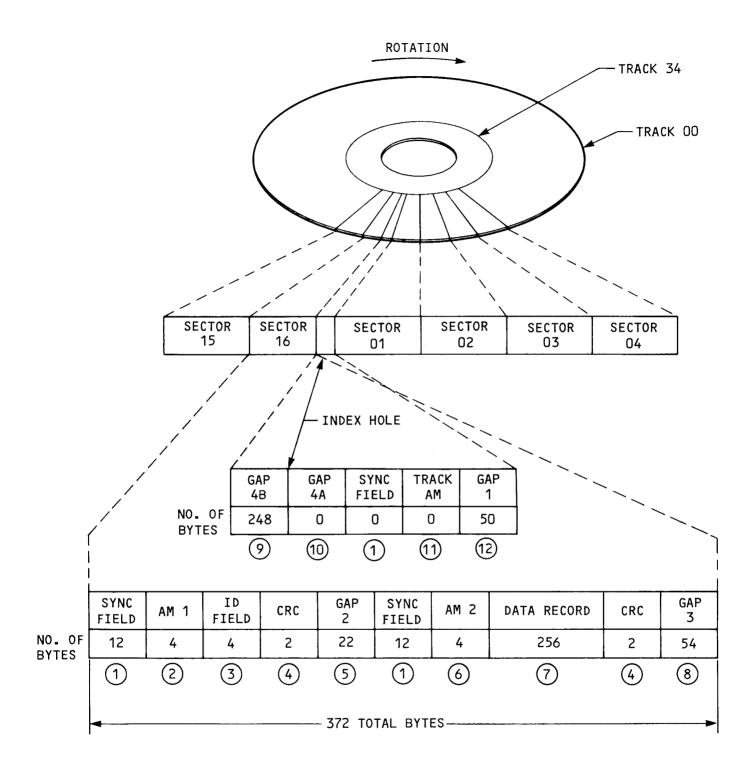

| C-6  | Mini-Size, Double-Density Track Format                         | C-9           |

#### LIST OF ILLUSTRATIONS

#### FIGURE

#### TITLE

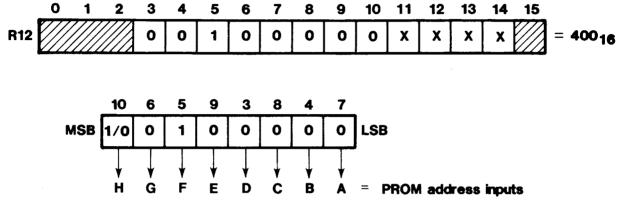

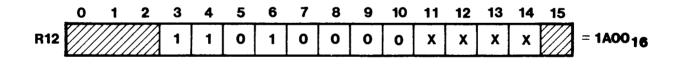

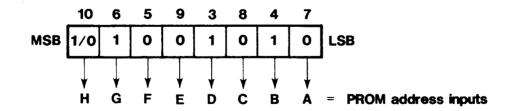

| E-1 | PROM U13 Address-Input Pins and Data-Output Pins                 | E-1 |

|-----|------------------------------------------------------------------|-----|

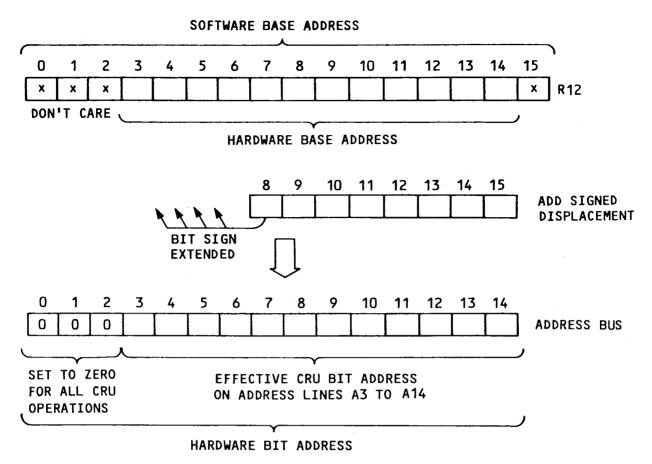

| E-2 | CRU Address Nomenclature                                         | E-2 |

| E-3 | CRU Address Scheme for Transferring Command List Address         | E-3 |

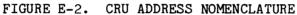

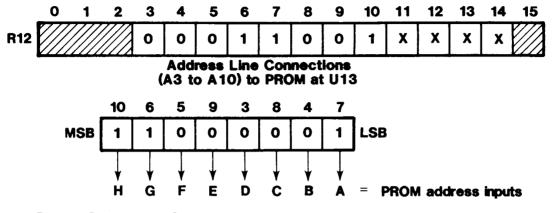

| E-4 | Interpreting Hardware Base Address as Address Input to PROM U13. |     |

| E-5 | Example 1 Results                                                |     |

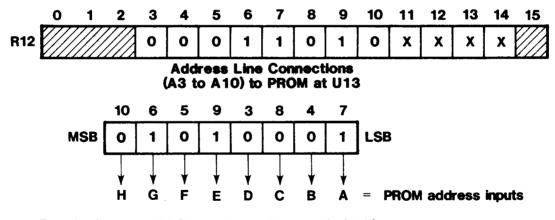

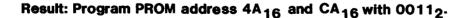

| Е-б | Example 2 Results                                                | E-7 |

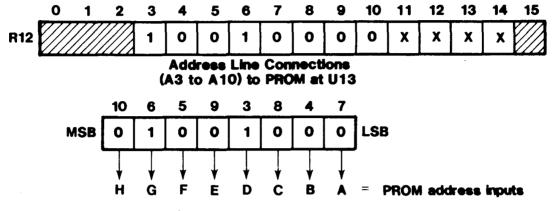

| E-7 | Example 3 Results                                                |     |

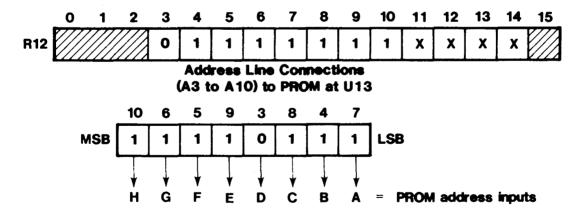

|     | Example 4 Results                                                |     |

#### LIST OF TABLES

| TABLE                                                                                                                                      | TITLE                                                                                                                                                                                  | PAGE                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| 1-1                                                                                                                                        | Disk Drives Supported by the TM 990/303B                                                                                                                                               | 1-1                                                                                              |

| 2–1<br>2–2                                                                                                                                 | TM 990/303B Jumper Settings<br>Error Interpretation on LEDs                                                                                                                            |                                                                                                  |

| 3-1<br>3-2<br>3-3                                                                                                                          | Summary of Commands to Disk Controller<br>Commands to Disk Controller in Word 2<br>Standard-Size Sector Placement According to Sector Interlace                                        |                                                                                                  |

|                                                                                                                                            | Factor                                                                                                                                                                                 | 3-39                                                                                             |

| $\begin{array}{r} 4-1 \\ 4-2 \\ 4-3 \\ 4-4 \\ 4-5 \\ 4-6 \\ 4-7 \\ 4-8 \\ 4-9 \\ 4-10 \\ 4-11 \\ 4-12 \\ 4-13 \\ 4-14 \\ 4-15 \end{array}$ | Read/Write Controller Bits                                                                                                                                                             | 4-4<br>4-6<br>4-7<br>4-9<br>4-11<br>4-13<br>4-17<br>4-18<br>4-19<br>4-19<br>4-29<br>4-29<br>4-31 |

| 5-1<br>5-2                                                                                                                                 | CRU Programmable Bits on the TMS 9902A<br>CRU-Bit Logic to Enable TMS 9902A Registers                                                                                                  |                                                                                                  |

| A-1<br>A-2<br>A-3<br>A-4<br>A-5                                                                                                            | Power Requirements for Disk Drives<br>IBM 8-Inch SS SD Drive Parameters<br>IBM 8-Inch DS SD Drive Parameters<br>IBM 8-Inch SS DD Drive Parameters<br>IBM 8-Inch DS DD Drive Parameters | A-4<br>A-4<br>A-5                                                                                |

#### TABLE

1

#### TITLE

| A-6<br>A-7<br>A-8<br>A-9<br>A-10<br>A-11<br>A-12<br>A-13 | TI 8-Inch SS DD Drive Parameters.<br>TI 8-Inch DS DD Drive Parameters.<br>IBM 8-Inch Modified SS DD Drive Parameters.<br>IBM 8-Inch Modified DS DD Drive Parameters.<br>IBM 5-Inch SS SD Drive Parameters.<br>IBM 5-Inch DS SD Drive Parameters.<br>IBM 5-Inch SS DD Drive Parameters.<br>IBM 5-Inch DS DD Drive Parameters.<br>IBM 5-Inch DS DD Drive Parameters. | A-6<br>A-7<br>A-7<br>A-8<br>A-8<br>A-8 |

|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| B-1<br>B-2                                               | Mini (5 <sup>1</sup> / <sub>4</sub> Inch) Floppy Drive Specifications<br>Standard (8 Inch) Floppy Drive Specifications                                                                                                                                                                                                                                             |                                        |

| F-1<br>F-2                                               | Pin List for TM 990/527 Cable for Model 800 Drive<br>Pin List for TM 990/535B Cable for Model 400 Drive                                                                                                                                                                                                                                                            |                                        |

#### SECTION 1

#### INTRODUCTION

#### 1.1 GENERAL

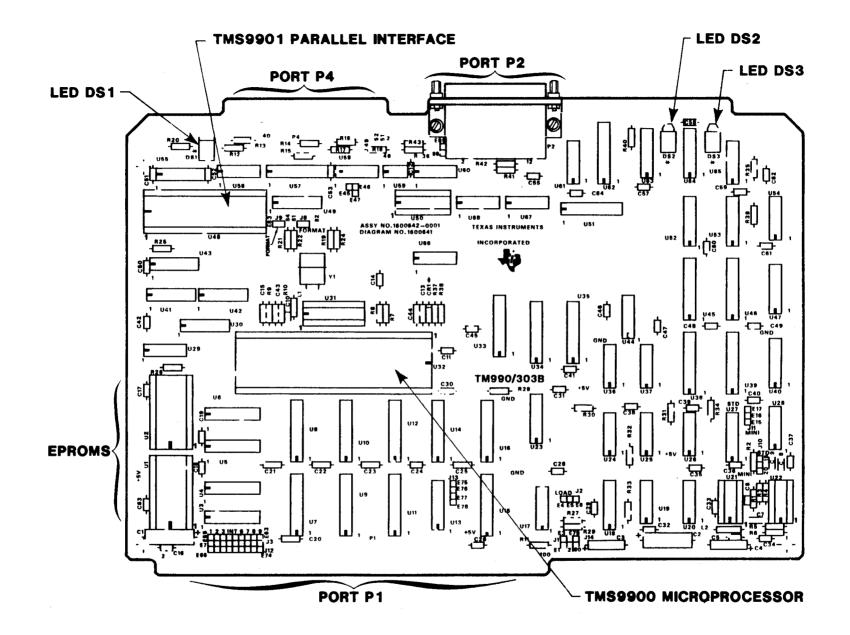

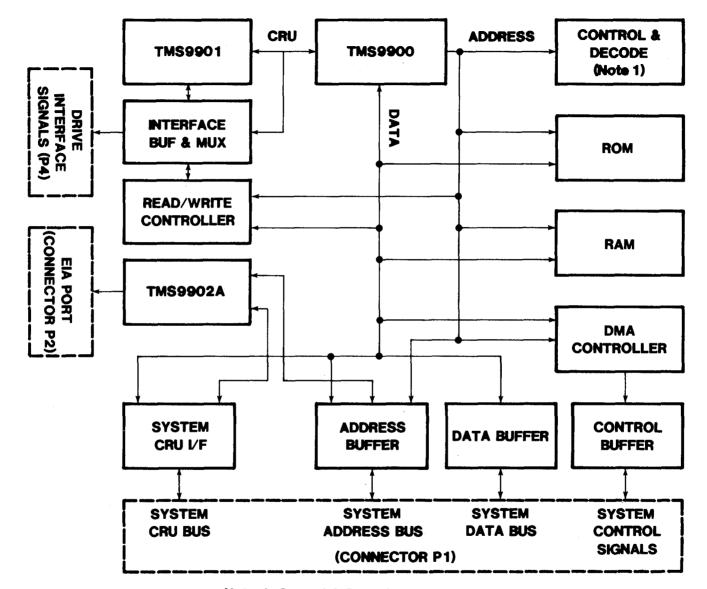

This manual covers the installation, operation, and theory of operation of the TM 990/303B floppy disk controller module, shown in Figure 1-1. Figure 1-2 is a block diagram of the module. This module provides a controlling interface between microcomputers such as the TM 990/101MA or the TM 990/102 and the disk drives listed in Table 1-1. It also features an I/O port addressable by the CPU module to provide an auxiliary interface to an RS-232-C device (not TTY).

|                                | TM 990/303B Supports:                  |                    |                    |                   |  |

|--------------------------------|----------------------------------------|--------------------|--------------------|-------------------|--|

| Company and Model              | No. of<br>Sides                        | IBM Sgl<br>Density | IBM Dbl<br>Density | TI Dbl<br>Density |  |

| Eight-In                       | ch Disk Dı                             | rives              |                    |                   |  |

| CDC 9404B                      | 1                                      | Ү <b>*</b>         | N                  | N                 |  |

| CDC 9406-4                     | 2                                      | Y*                 | <b>Ү*</b>          | Y <b>*</b>        |  |

| Qume DT-8 (Qumetrack 842       |                                        | Υ <b>*</b>         | Υ <b>*</b>         | Υ <b>*</b>        |  |

| Shugart SA800                  | 1                                      | Y*                 | <b>Ү*</b>          | Υ <b>*</b>        |  |

| Shugart SA801                  | 1                                      | Y <b>*</b>         | Υ <b>*</b>         | Y <b>*</b>        |  |

| Shugart SA850/851              | 2                                      | Y*                 | Y*                 | Y <b>*</b>        |  |

| Siemens FDD100-8               | 1                                      | Y                  | Y                  | Y                 |  |

| Siemens FDD200-8               | 2                                      | Y                  | Y                  | Ŷ                 |  |

| Tandon TM848-1                 | 1                                      | Y                  | Y                  | Y<br>Y            |  |

| Tandon TM848–2                 | 2                                      | Y                  | Y                  | I                 |  |

| Fi <b>ve</b> (5 <del>1</del> ) | Five $(5\frac{1}{4})$ Inch Disk Drives |                    |                    |                   |  |

| BASF 6106                      | 1                                      | Y <b>*</b>         | Y                  | N                 |  |

| CDC 9408                       | 1                                      | Y                  | Y                  | N                 |  |

| CDC 9409T                      | 2                                      | Y                  | Х <b>*</b>         | N                 |  |

| Qume DT-5                      | 2                                      | Х*                 | Y                  | N                 |  |

| Shugart SA400                  | 1                                      | Х <b>ж</b>         | Y                  | N                 |  |

| Shugart SA450                  | 2                                      | Ү <b>≭</b>         | Υ <b>*</b>         | N                 |  |

| Shugart SA410                  | 1                                      | Y                  | Y                  | Ν                 |  |

| Shugart SA460                  | 2                                      | Y                  | N                  | N                 |  |

| Siemens FDD100-5               | 1                                      | Х <b>*</b>         | Y                  | Ν                 |  |

| Siemens FDD200-5               | 2                                      | Y                  | Y                  | N                 |  |

| Siemens FDD196-5               | 1                                      | Y                  | N                  | Ν                 |  |

| Siemens FDD296-5               | 2                                      | <b>ү*</b>          | N                  | N                 |  |

| Tandon TM100-1                 | 1                                      | Y                  | Y                  | N                 |  |

| Tandon TM100-3                 | 1                                      | Y                  | Y                  | N                 |  |

| Tandon TM100-4                 | 2                                      | Y                  | Υ <b>*</b>         | N                 |  |

TABLE 1-1. DISK DRIVES SUPPORTED BY THE TM 990/303B

Y = supported; Y\* = supported for bootload also; N = not supported

1-1

The TM 990/303B can be used with microcomputer modules such as the TM 990/100MA, TM 990/101MA, or TM 990/102. However, because of buffering on the TM 990/100M and TM 990/100MA modules, the controller cannot do DMA (direct memory access) with the memory on these modules. To do DMA with a TM 990/100M or TM 990/100MA, an expansion memory module must be used.

If the TM 990/303B is to be used with the TM 990/101M module, the CPU module must be modified to the equivalent of the TM 990/101MA microcomputer module. All TM 990/101M modules returned to the factory for repair are automatically updated. The PCB board number will show if the module has been modified to the correct revision level. This board number is found on the lower left of the conductor side of the module. A board number of 994725-1 A B or 994725-1 (or later letter) indicates a PCB that has been modified to the proper revision level. A board number such as 994725-1 A indicates a PCB not modified to the proper revision level.

#### 1.2 FEATURES

The TM 990/303B floppy disk controller has the following features:

- Formats supported:

- IBM single density format,

- IBM double density format,

- IBM modified double density with 256 bytes/sector on all tracks,

- TI Digital Systems Group (DSG) double density format (TILINE floppy controller).

- Disk sizes: Standard or mini (8 or 51 inch).

- Number of disk sides supported: One or two (see Table 1-1).

- Number of disk drives (daisy chained): Four maximum (note that some mini drives can accommodate a maximum of only three drives in a daisy chain).

- Recording methods:

- Single density frequency modulation (FM),

- Double density modified frequency modulation (MFM).

- Data format:

- IBM 3740 compatible,

- TI FS 990 compatible.

- System interfaces:

- Controller initialization through the Communication Register Unit (CRU),

- Data and commands through DMA transfer,

- Interrupts.

- RS-232-C interface is addressable by the host CPU module (to provide an additional EIA interface for system).

- Three LEDs indicate controller status.

- Bootstrap load feature can be used to initialize system from diskette.

- Controller firmware is provided on two TMS 2532s (4 K words).

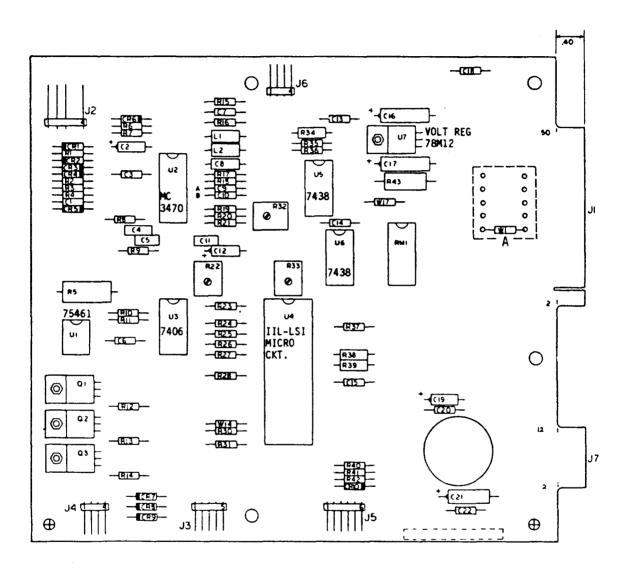

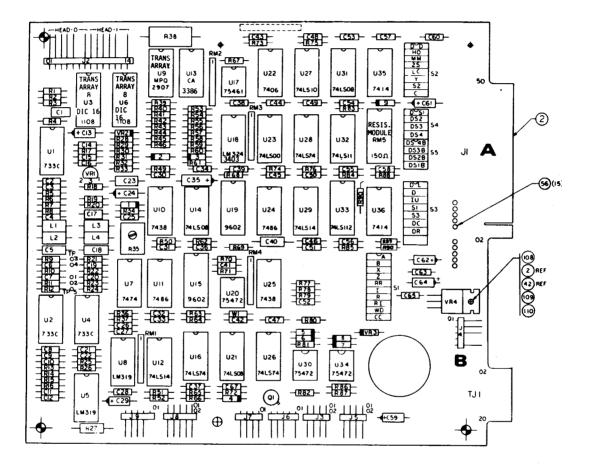

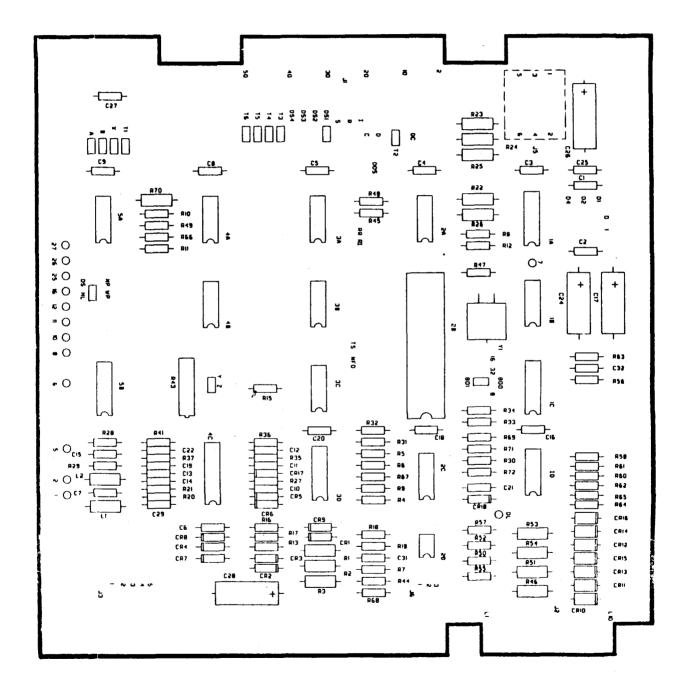

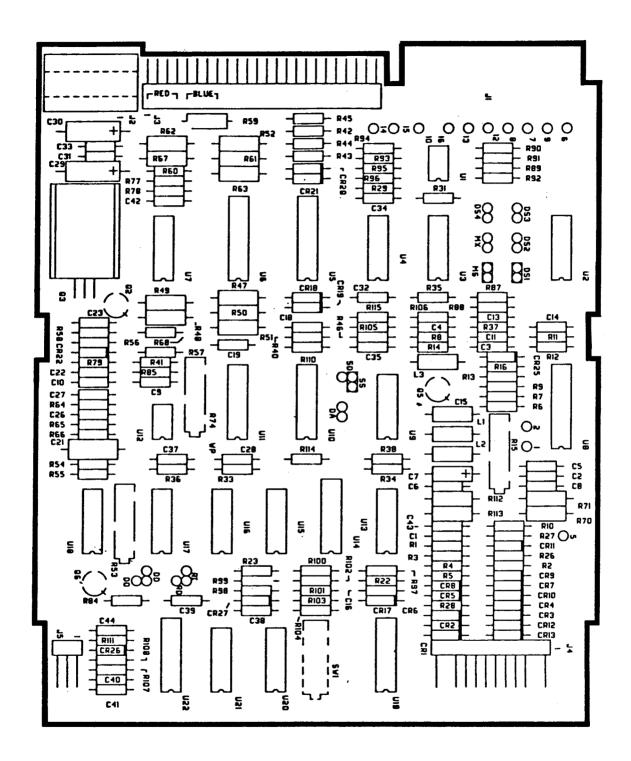

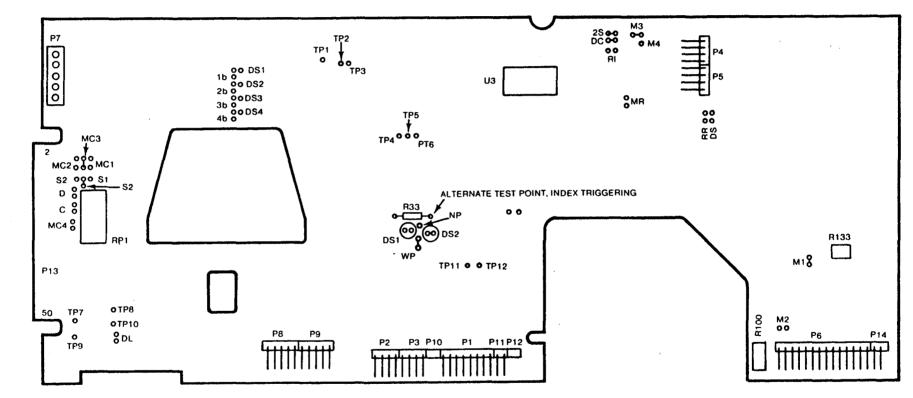

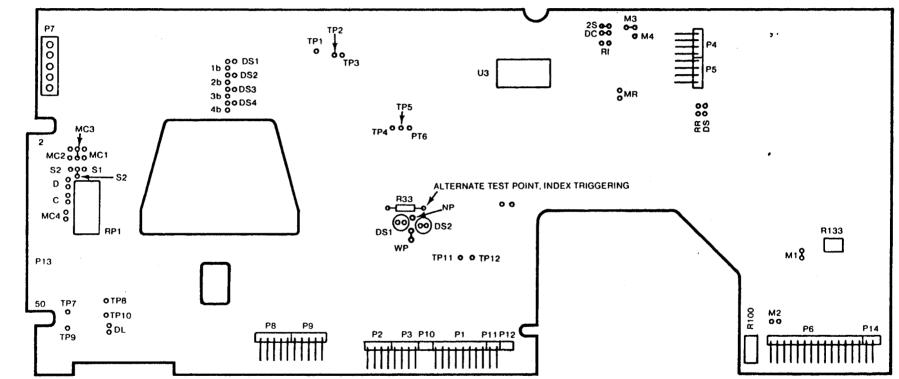

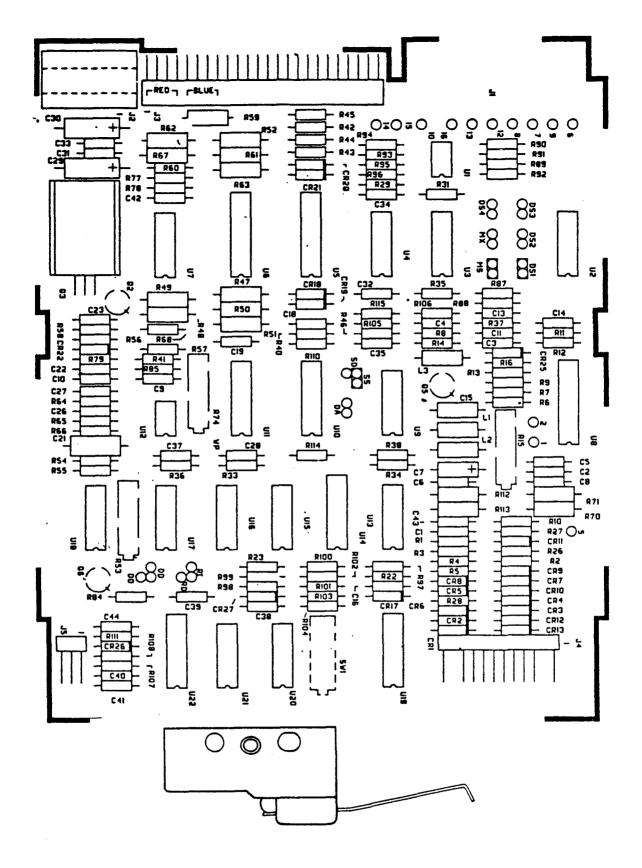

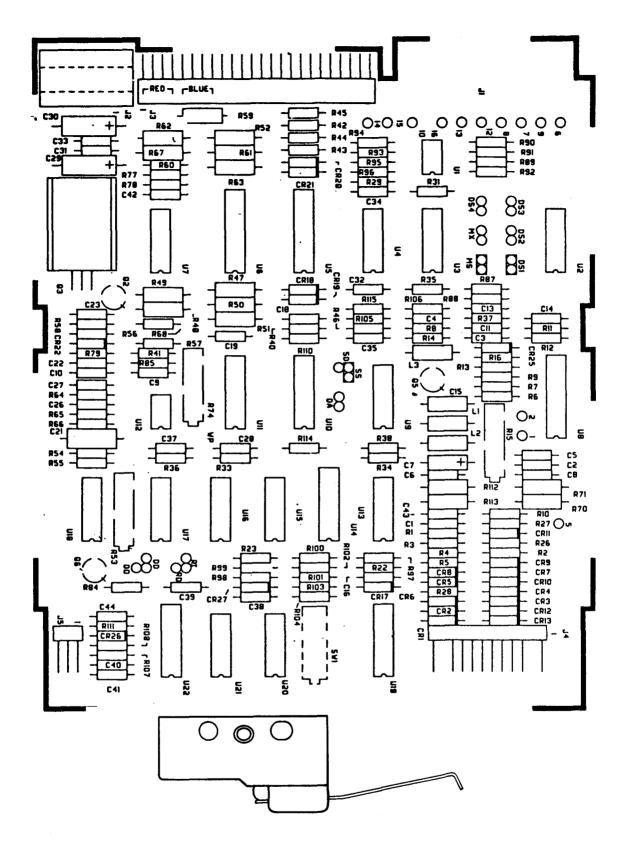

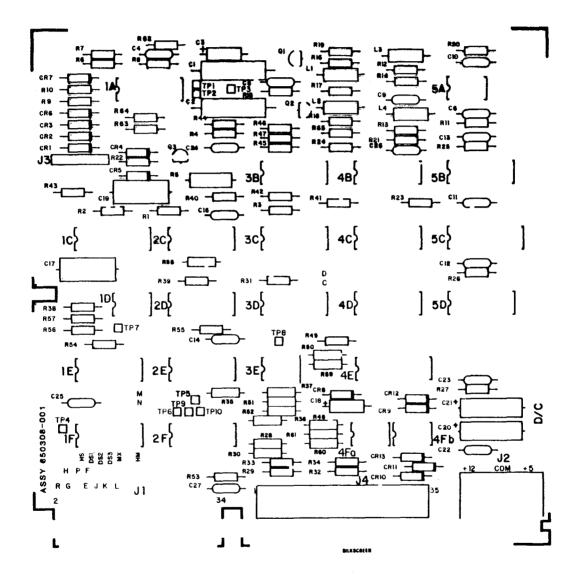

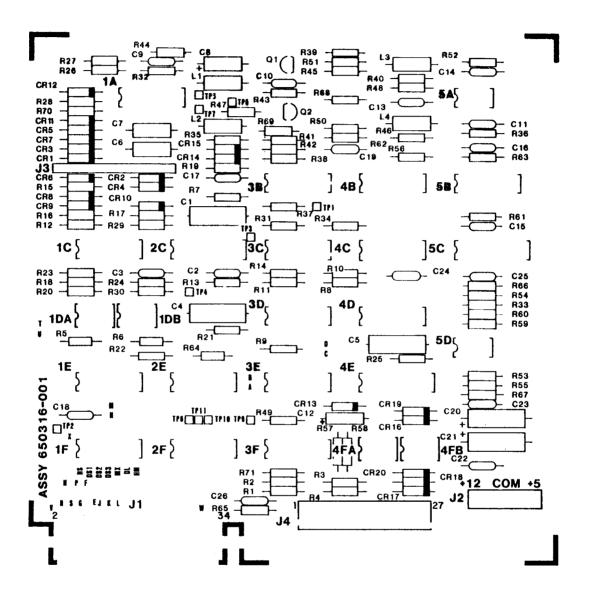

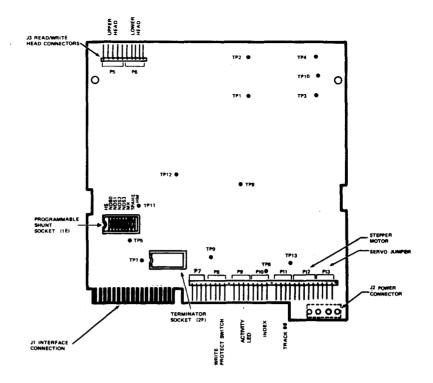

FIGURE 1-1. PRINCIPAL COMPONENTS OF THE TM 990/303B MODULE

Note 1: Control & Decode Block Functions:

- RAM/ROM Access

- DMA Enable

- e Read/Write Controller Enable

FIGURE 1-2. TM 990/303B BLOCK DIAGRAM

Software on the controller includes the following features:

- 19 commands including controller self test, read and write to/from diskette and host memory, read and write to/from controller and host RAM, bootstrap load from diskette software, format diskette, execute program in controller memory, read status of specified drive, store drive status, modify controller interface, read id, read deleted, write deleted, read unformatted, read drive interface line status,

- Command completion interrupt to host (interrupt level jumper selectable); completion status reported to host,

- Controller call through interrupt via CRU,

- Controller generated interrupt upon command completion.

#### 1.3 MANUAL ORGANIZATION

This manual is organized as follows:

- Section 1: General information and specifications of the TM 990/303B.

- Section 2: How to install the TM 990/303B module including required peripheral equipment, disk drive requirements, system configuration, cabling, example program.

- Section 3: Bringing up the system, example software, bootload at power up, command explanation, data formats, and disk drive parameters.

- Section 4: Theory of operation including circuit descriptions, timing diagrams.

- Section 5: Programming TMS 9902A EIA port controller at port P2.

- Appendices containing auxiliary data including disk drive installation details (jumper positions, etc.), logic diagrams, parts list, cable pinouts, disk format tables, etc.

#### 1.4 TYPICAL SYSTEM CONFIGURATION

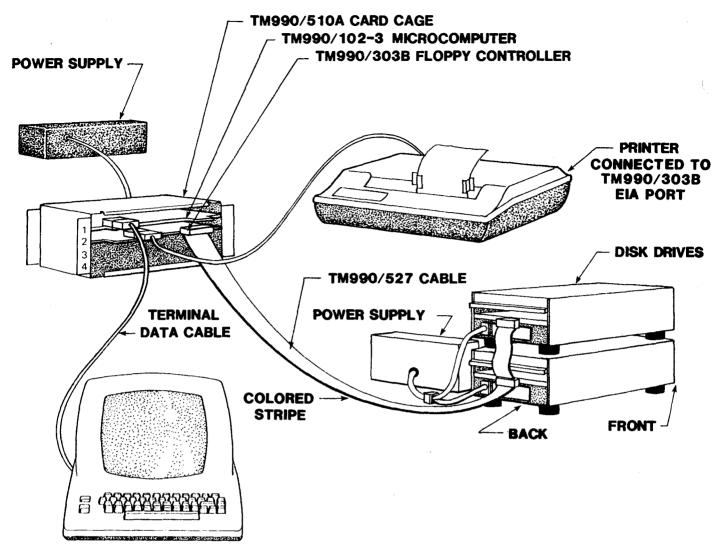

Figure 1-3 shows a typical system configuration with a TM 990/102-3 module, a TM 990/303B. a terminal connected to the CPU module's EIA port, and a printer connected to the controller module's EIA port. The same software run on a comparable TM 990/101MA, TM 990/203, and TM 990/303A system can also be used in this system shown in Figure 1-3 if the port on the TM 990/303B has a CRU software base address of 0180<sub>16</sub> (the same as the base address for the TM 990/101MA's auxilary port).

Figure 1-3 shows two standard-sized floppy disk drives connected to the floppy controller by a TM 990/527 cable; if a four-drive standard-size capability is desired, the user can provide his own cable using the data in Appendix F.

Note that the disk drives are "daisy-chained"; that is, they are connected by a single cable containing connectors for each disk unit.

In a typical system, the bootstrap load feature of the TM 990/303B would be used to load the routines to initialize the system into host RAM. An initial load routine would be used to bring in other system tasks from the diskette to host RAM. These routines could include a file manager, device service routines to drive peripherals, as well as other system software requirements. The disk controller could then cause execution of a task in host memory that would start dedicated system functions.

FIGURE 1-3. TYPICAL SYSTEM CONFIGURATION USING TWO MODEL 800 DISK DRIVES

### CAUTION

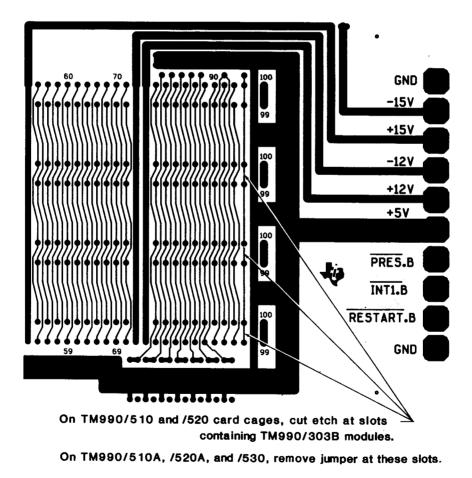

Before applying power to the system carefully follow the installation procedures specified in Section 2 of this manual. When using a TM 990/510 or TM 990/520 card cage, the etch on the backplane between lines 95 and 96 must be open (cut) in each slot that the TM 990/303B module is installed. On TM 990/510A, /520A, and /530 chassis, remove the jumper corresponding to the slot containing the TM 990/303B module. Follow the procedures in section 2.6 and Figure 2-2. This applies to all TM 990/303B modules installed.

#### 1.5 POWER

1.5.1 TM 990/303B Power Requirements

The following are dc power requirements for the TM 990/303B module:

|             | _   | Vdc<br><u>Max</u> |     |     |      |     | (voltage tol-<br>erance <u>+</u> 3%) | <u>Unit</u> |

|-------------|-----|-------------------|-----|-----|------|-----|--------------------------------------|-------------|

| TM 990/303B | 2.1 | 3.0               | 0.1 | 0.2 | 0.04 | 0.2 |                                      | Amps        |

During a powerup or a powerdown of either the disk controller or the disk drive (or both), data previously recorded on the diskette will not be destroyed due to controller action. Any operation in progress during a power sequence will not be completed.

1.5.2 Disk Drive DC Power Requirements

Individual disk drive power requirements are shown in Appendix A, section A.1.

Usually, mini disk drives function best when the peak-to-peak ripple for +5 Vdc is 50 mV or less, and the ripple for +12 Vdc is 100 mV or less.

If power is being supplied from separate power supplies, the system requires that -12V be turned on first and be turned off last. There is no required sequence in turning on the remaining voltages. This does not apply if the system uses only one power supply.

#### 1.6 ENVIRONMENT

Ambient Temperature:

Operating: 0 to 70 degrees C (32 to 158 degrees F) at sea level Storage: -40 to +100 degrees C (-40 to +212 degrees F)

#### Shock:

Shipping: 15 g applied to shipping container

Ambient Humidity:

Operating: 5 to 85 percent relative humidity without condensation Storage: 5 to 95 percent without condensation

#### 1.7 APPLICABLE DOCUMENTS

- TM 990/100MA Microcomputer User's Guide

- TM 990/101MA Microcomputer User's Guide

- TM 990/102 Microcomputer User's Guide

- TMS 9900 Microprocessor Data Manual

- TMS 9901 Programmable Systems Interface Data Manual

- TMS 9902A Asynchronous Communication Controller Data Manual

- TM 990/201/206 Expansion Memory Modules

- TM 990/202 EPROM/RAM Module

- TM 990/203 Dynamic RAM Memory Expansion Module

- TM 990/204 Memory Module with Battery Backup

- TM 990/425B Demonstration Software for TM 990/303B

- TM 990/527 Cable for Standard Disk Drives User's Guide

- TM 990/535B Cable for Mini Disk Drives User's Guide

#### SECTION 2

#### INSTALLATION AND OPERATION

#### 2.1 GENERAL

This section covers the installation of the TM 990/303B Floppy Disk Controller and has some example software to illustrate controller operation.

CAUTION

- 1. Before applying power to your TM 990/303B module, properly set jumper plugs and connectors as described in the following:

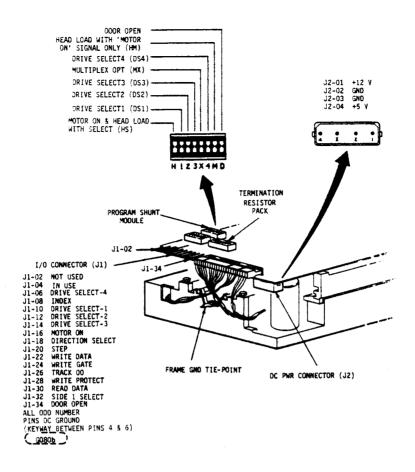

- jumpers at TM 990/303B module (section 2.4, Figure 2-1, Table 2-1),

- jumpers on the disk drive (Appendix A or in drive user's guide),

- cable attachment to standard drive (section 2.7, Figures 2-4, 2-5), or cable attachment to mini drive (section 2.7, Figures 2-6, 2-7),

- cut backplane etch in chassis slot where controller module is installed (see section 2.6) or remove the jumpers between line 95 and 96 on the backplane of chassis.

- 2. When using a TM 990/510 or /520 card cage, the etch on the backplane between lines 95 and 96 must be open (cut) in each slot that the TM 990/303B module is installed. Follow the procedures in section 2.6 and Figure 2-2. This applies to all TM 990/303B modules installed. For TM 990/510A, TM 990/520A, and TM 990/530 card cages, remove the jumpers provided for this purpose.

- 3. Verify the system configuration using the check list in section 2.8 before applying power. Improper switch or jumper settings may harm equipment.

#### 2.2 UNPACKING

Find the following:

- TM 990/303B Floppy Disk Controller Module

- TM 990/303B Floppy Disk Controller User's Guide

- Warranty Card

- Factory Repair and Exchange Policy

Remove the TM 990/303B module from its protective packing. Report any discrepancies to your supplier.

#### 2.3 REQUIRED EQUIPMENT

This floppy disk controller module is recommended for use <u>only</u> with the disk drives listed in Table 1-1.

A power supply must be provided to meet the total power requirements of the system, including, for example:

- disk drive(s),

- TM 990/303B module as specified in section 1.5,

- microcomputer module,

- if installed, an expansion memory module (necessary for TM 990/100M or TM 990/100MA system) or other auxiliary module.

A TM 990/510A (four slots), TM 990/520A (eight slots), TM 990/530 (16 slots) or equivalent card cage should be used to provide signal and power busing to the microcomputer, disk controller, and (if used) expansion memory module. The microcomputer should be placed in the top of the cage with other modules below it.

A terminal (and proper terminal cabling), such as the Texas Instruments 743 is required for user interaction.

A connecting cable such as the TM 990/527 (two standard disk drives) or TM 990/535B (three mini drives) is needed between disk controller port P4 and the floppy disk drive(s). Cables to accomodate four drives (either 8 or  $5\frac{1}{4}$  inch drives) are easily made and are usually available from a distributor. Appendix F lists disk drive pinouts.

An expansion RAM memory module can provide additional storage and workspace for the host system. Suggested expansion memory modules include the TM 990/202 EPROM/RAM module, the TM 990/203 dynamic memory module or the TM 990/206 static RAM module. Because memory on the TM 990/100M and the TM 990/100MA modules is buffered, they cannot be used for DMA.

#### 2.4 JUMPERS ON TM 990/303B MODULE

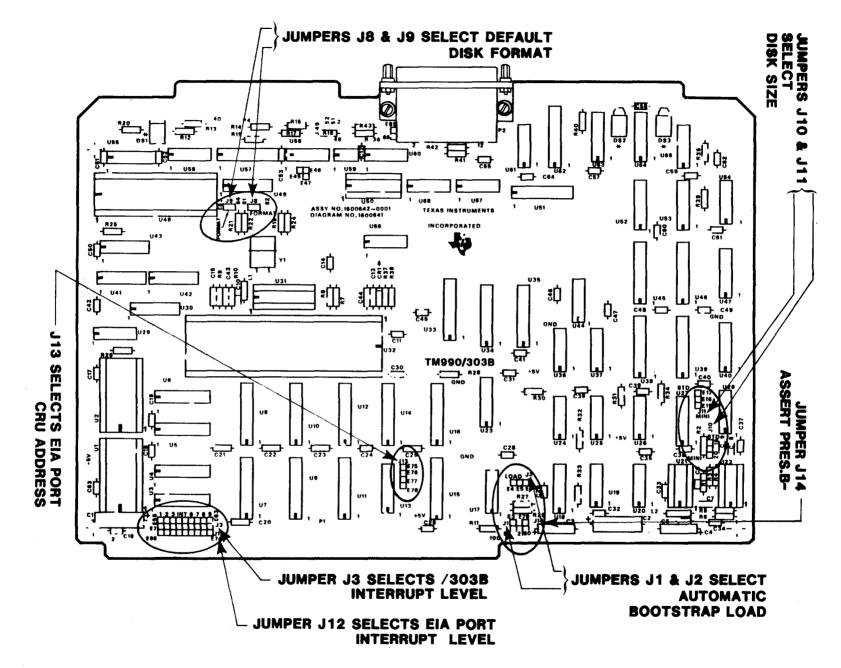

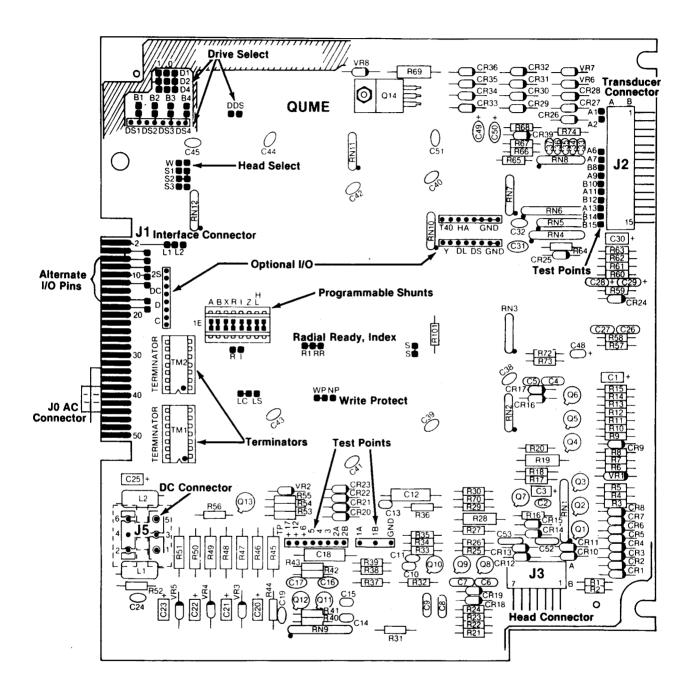

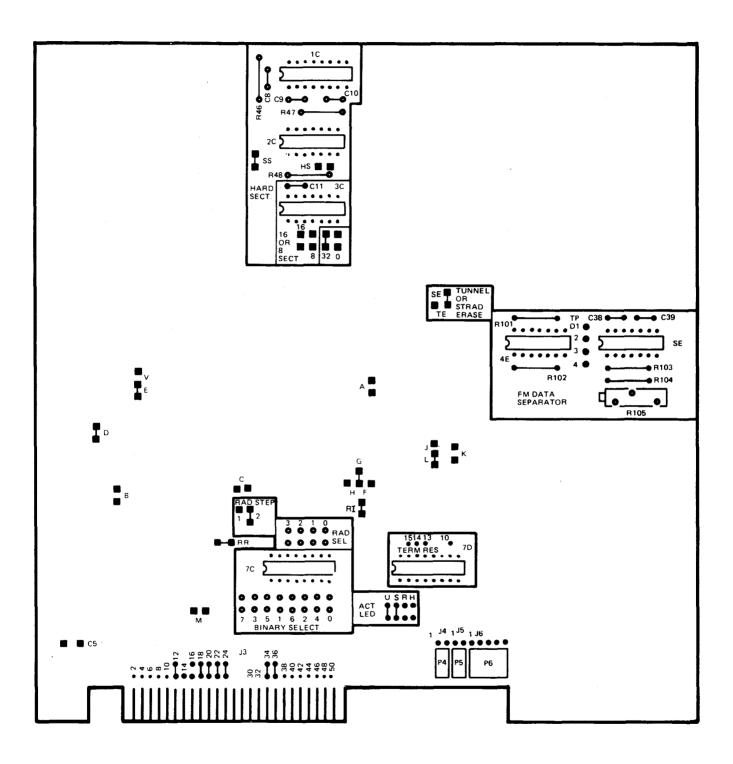

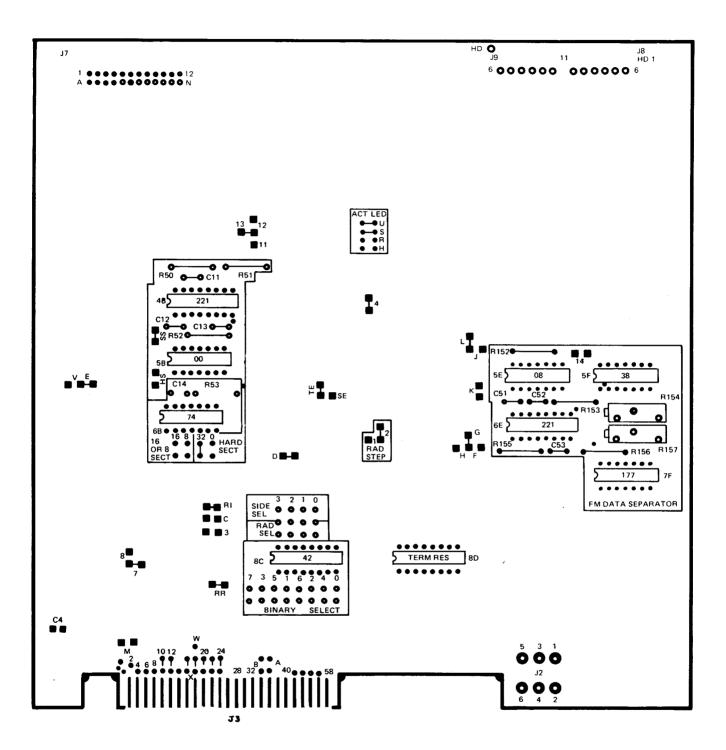

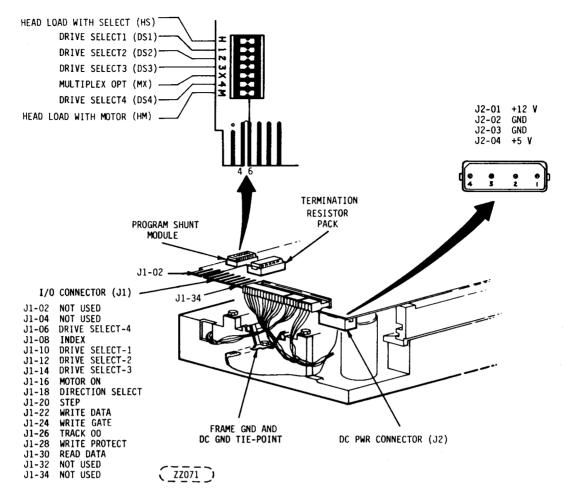

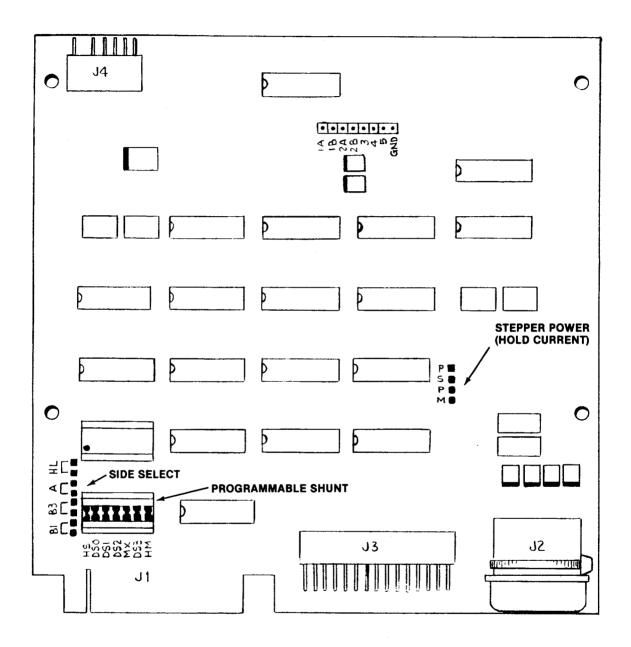

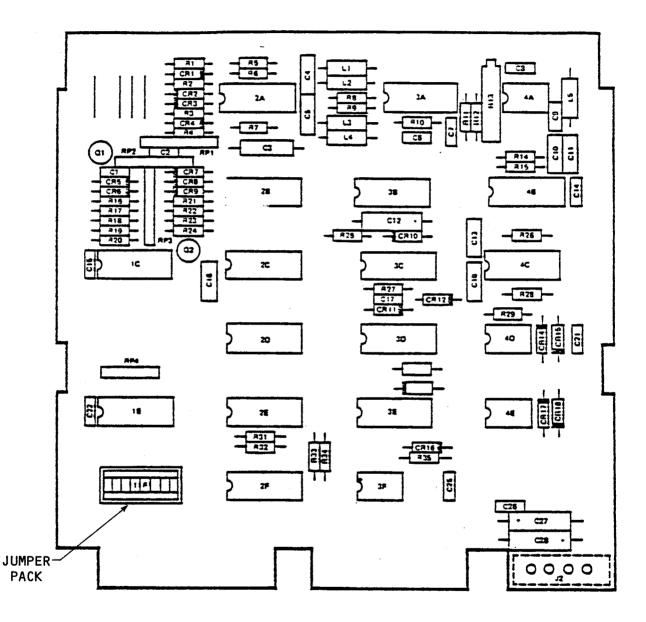

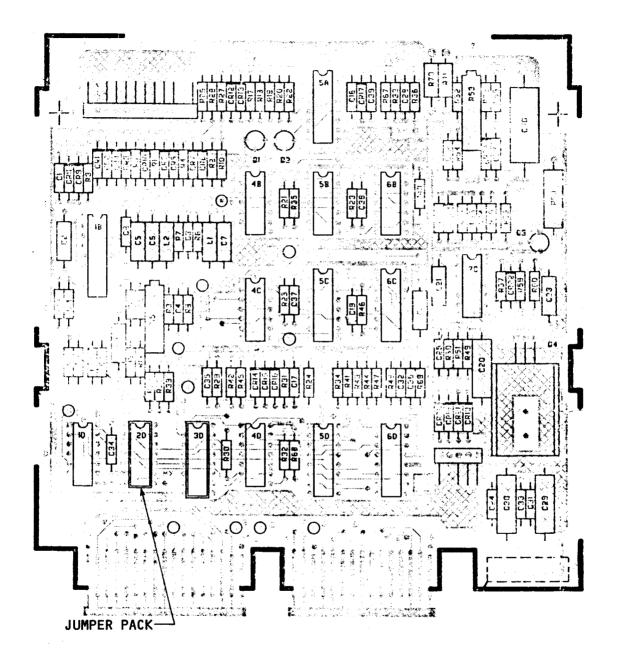

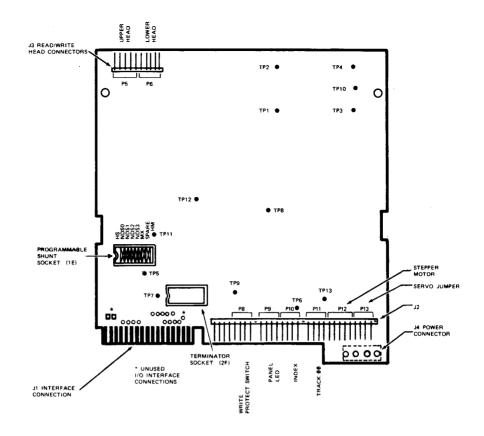

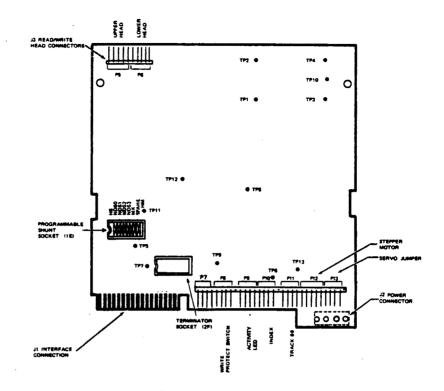

Module jumper locations are shown in Figure 2-1; module jumper settings are listed in Table 2-1. Note that jumpers J4, J5, J6, and J7 are not used.

#### NOTE

The Define Drive command (command  $10_{16}$  in Table 3-2) must specify the same disk size (standard or mini) as specified by jumpers J10 and J11. Failure to match the software designation (via the Define Drive command) and the hardware settings at J10 and J11 will result in incorrect performance. This command does not have to conform to the settings of jumpers J8 and J9 which set the default value only at a powerup or bootload; this default can be changed by the Define Drive command.

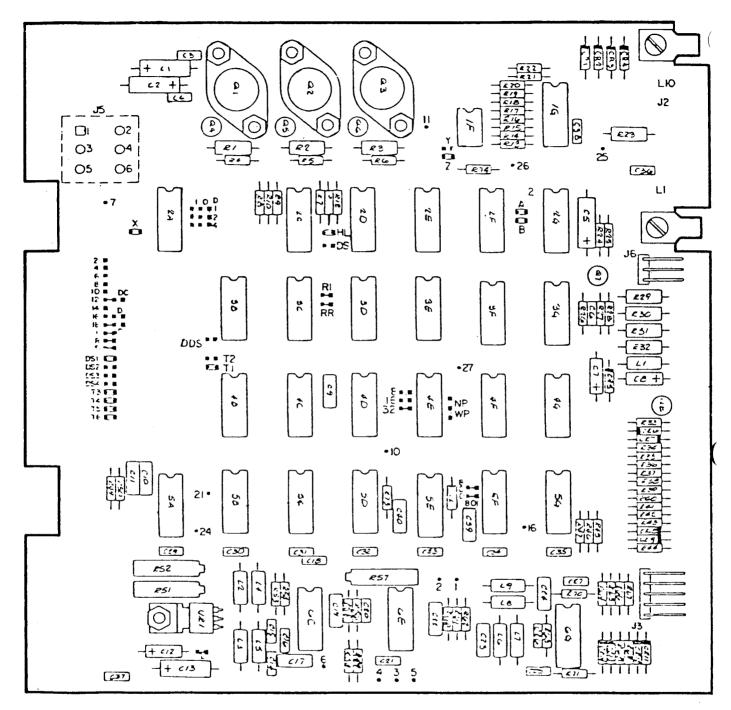

#### 2.5 JUMPERS ON DISK DRIVES

Follow the manufacturer's instructions for setting jumpers on the respective disk drive printed circuit boards. Suggested disk drive jumper settings are listed in Appendix A.

NOTE: There are no jumpers J4, J5, J6, and J7.

FIGURE 2-1. TM 990/303B JUMPER LOCATIONS

2-3

TABLE 2-1. TM 990/303B JUMPER SETTINGS (page 1 of 2)

| Function                                                                                                                                                                                                                                                      | Jumper Setting<br>* = As Shipped                                                                                                  | Comments                                                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. Bootstrap Load Selection                                                                                                                                                                                                                                   |                                                                                                                                   | · · · · · · · · · · · · · · · · · · ·                                                                                                                                           |

| - Automatic Bootstrap Load<br>- No Automatic Bootstrap Load                                                                                                                                                                                                   | J1 E1-E2<br>J2 E4-E5<br>*J1 E1-E3<br>*J2 E5-E6                                                                                    |                                                                                                                                                                                 |

| 2. Controller Interrupt Level to Host C                                                                                                                                                                                                                       | PU                                                                                                                                |                                                                                                                                                                                 |

| <ul> <li>Interrupt Level 1</li> <li>Interrupt Level 2</li> <li>Interrupt Level 3</li> <li>Interrupt Level 4</li> <li>Interrupt Level 5</li> <li>Interrupt Level 6</li> <li>Interrupt Level 7</li> <li>Interrupt Level 8</li> <li>Interrupt Level 9</li> </ul> | J3 E55-E7<br>*J3 E56-E8<br>J3 E57-E9<br>J3 E58-E10<br>J3 E59-E11<br>J3 E60-E53<br>J3 E61-E54<br>J3 E62-E64<br>J3 E63-E65          |                                                                                                                                                                                 |

| 3. EIA Port Interrupt Level to Host CPU                                                                                                                                                                                                                       | • ······                                                                                                                          | TMS 9902A can be programmed to issue                                                                                                                                            |

| <ul> <li>Interrupt Level 1</li> <li>Interrupt Level 2</li> <li>Interrupt Level 3</li> <li>Interrupt Level 4</li> <li>Interrupt Level 5</li> <li>Interrupt Level 6</li> <li>Interrupt Level 7</li> <li>Interrupt Level 8</li> <li>Interrupt Level 9</li> </ul> | J12 E7-E66<br>J12 E8-E67<br>J12 E9-E68<br>J12 E10-E69<br>J12 E11-E70<br>*J12 E53-E71<br>J12 E54-E72<br>J12 E64-E73<br>J12 E65-E74 | interrupts for four<br>different conditions<br>For no interrupts,<br>remove the jumper.<br>See CAUTION below.                                                                   |

| <ul> <li>4. Reset Host CPU at Powerup Bootload</li> <li>- Assert PRES- to host CPU at<br/>powerup bootload (J1 jumpered<br/>for automatic bootload also)</li> <li>- Do not assert PRES- to host<br/>CPU at powerup bootload</li> </ul>                        | *J14 In<br>J14 Out                                                                                                                | J14 (E79-E80) must b<br>jumpered when used<br>with CPUs such as th<br>TM 990/100 or /101<br>(but unjumpered when<br>used with /102 which<br>which asserts PRES-<br>at powerup). |

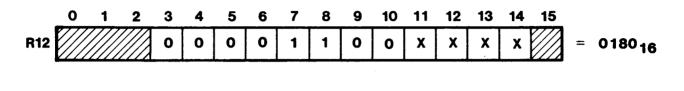

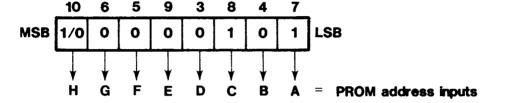

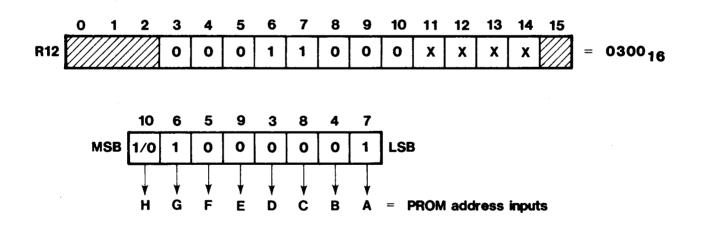

| 5. EIA Port: CRU Software Base Address<br>(R12 Contents) & Port Deselect                                                                                                                                                                                      |                                                                                                                                   |                                                                                                                                                                                 |

| - 0180 <sub>16</sub> Base Address<br>- 0300 <sub>16</sub> Base Address<br>- Deselect EIA Port                                                                                                                                                                 | *J13 E78-E77<br>J13 E77-E76<br>J13 E76-E75                                                                                        | Port inoperable; Se                                                                                                                                                             |

If J13 is set to deselect the EIA port (P2) with E76-E75 jumpered, DO NOT select an EIA interrupt: leave J12 unjumpered. Follow this precaution to prevent unwanted interrupts if the TMS 9902A is not in the reset state.

| TABLE 2-1. TM 990/303B JUMPER SETTINGS (page 2 of | TABLE 2-1. | TM 990/303B | JUMPER SETTINGS | (page 2 of 2) |

|---------------------------------------------------|------------|-------------|-----------------|---------------|

|---------------------------------------------------|------------|-------------|-----------------|---------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | r                                                                                                                                    |                                                                                                                                          |                                                                          |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--|--|--|

| Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Jumper Setting<br>* = As Shipped                                                                                                     | Comments                                                                                                                                 | TWOSIDED-                                                                |  |  |  |

| 6. Select Default Diskette Format for:                                                                                                                                                                                                                                                                                                                                                                                                                                        | Note: S = S                                                                                                                          | ingle, D =                                                                                                                               | Double                                                                   |  |  |  |

| a. Powerup Bootload (J1/J2 set for a                                                                                                                                                                                                                                                                                                                                                                                                                                          | automatic bootload                                                                                                                   | )                                                                                                                                        |                                                                          |  |  |  |

| IBM S Density, S Sided<br>IBM S Density, D Sided<br>IBM D Density, S Sided<br>IBM D Density, D Sided<br>IBM Modified D Density, S Sided<br>IBM Modified D Density, D Sided<br>TI D Density, S Sided<br>TI D Density, D Sided<br>Mini S Density, S Sided<br>Mini D Density, D Sided                                                                                                                                                                                            | J8 In, J9 In<br>J8 In, J9 Out<br>J8 In, J9 Out<br>J8 In, J9 Out<br>J8 In, J9 Out<br>J8 Out, J9 In<br>J8 Out, J9 In<br>J8 Out, J9 Out | See Note 1<br>See Note 1 |                                                                          |  |  |  |

| b. Powerup Reset only (J1/J2 not se                                                                                                                                                                                                                                                                                                                                                                                                                                           | t for automatic bo                                                                                                                   | otload)                                                                                                                                  |                                                                          |  |  |  |

| IBM S Density, S Sided<br>IBM S Density, D Sided<br>IBM D Density, S Sided<br>IBM D Density, D Sided<br>TI D Density, S Sided<br>TI D Density, D Sided<br>Mini S Density, S Sided                                                                                                                                                                                                                                                                                             | J8 In, J9 In<br>J8 In, J9 Out<br>J8 In, J9 Out<br>J8 Out, J9 In<br>J8 Out, J9 In                                                     | See Note 1<br>See Note 1<br>See Note 1<br>See Note 1<br>See Note 1<br>See Note 1<br>See Note 1                                           | Not Active<br>Active<br>Not Active<br>Active<br>Not Active<br>Active<br> |  |  |  |

| Note 1: J8 = E81-E82, J9 = E84-E83. A powerup bootload or powerup reset<br>requires the correct sided diskette in the drive. The correct<br>diskette will result in pin P4-10 being a "0" for two-sided diskettes<br>and a "1" for one-sided diskettes correctly placed in the drive.<br>This signal is inverted at U49 and is valid only when the drive is<br>selected for access. P4-10 is not used for mini drives because mini<br>drives do not have this interface line. |                                                                                                                                      |                                                                                                                                          |                                                                          |  |  |  |

| 7. Select Disk Size                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                      |                                                                                                                                          |                                                                          |  |  |  |

| - Standard Size                                                                                                                                                                                                                                                                                                                                                                                                                                                               | *J10 E41-E42<br>*J11 E44-E45                                                                                                         |                                                                                                                                          |                                                                          |  |  |  |

| - Mini Size                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | J10 E40-E41<br>J11 E43-E49                                                                                                           |                                                                                                                                          |                                                                          |  |  |  |

#### NOTE

•

Jumpers J4, J5, J6, and J7 are not used.

#### 2.6 MODULE INSTALLATION

Turn power off before installation of modules into the card cage. Install the microcomputer module at the top of the cage with other modules beneath, with any blank slots being at the bottom of the card cage. Where the TM 990/303B modules are installed in a TM 990/510 or /520 card cage, cut the connection on the card cage backplane between lines 95 and 96 as shown in Figure 2-2. This break is made at the slot containing the TM 990/303B module:

- on TM 990/510A, /520A, and 530 card cages, remove the jumper at the slot, or

- on TM 990/510 and 520 card cages, cut the etch as shown in Figure 2-2.

This is the same as for multicontroller systems as explained in section 2.10. Properly install the modules and connect cables as specified in section 2.7. All modules should be close together in the card cage with empty slots at the bottom. Next, conduct a system check and apply power as described in section 2.8.

FIGURE 2-2. LOCATION OF SOLDER BRIDGE BETWEEN PINS 96 AND 95 OF MOTHERBOARD

#### 2.7 CABLING

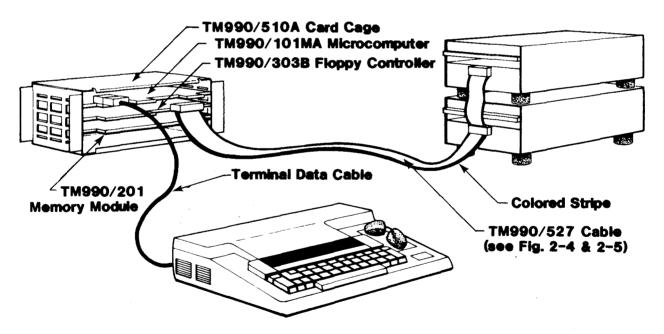

Figure 2-3 shows a typical system configuration using a TM 990/527 cable which connects one or two eight-inch drives to the controller module. Detail connections using this cable are shown in Figures 2-4 and 2-5. To connect an eight-inch disk drive system:

- Connect the EIA data cable from the terminal to connector P2 of either the microcomputer module or the controller module.

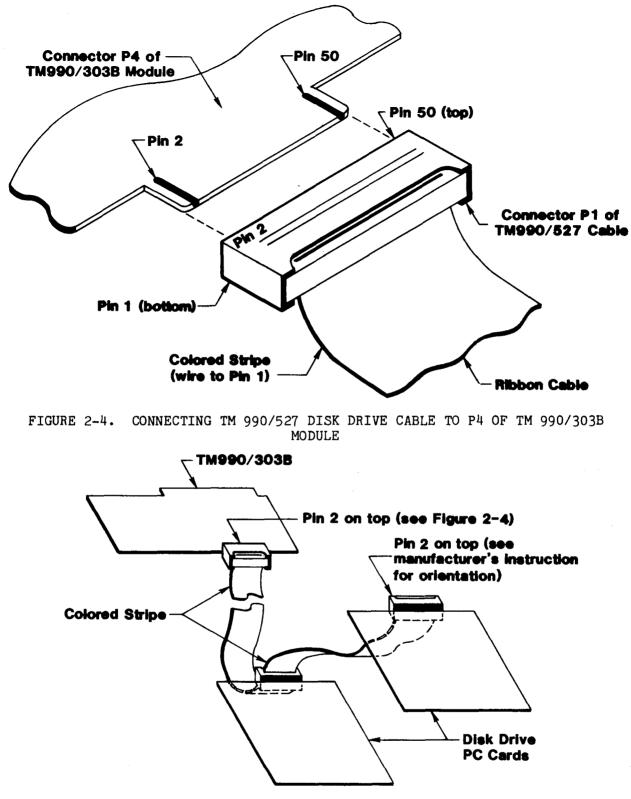

- The TM 990/527 cable has three connectors on it. The end with the two connectors closest together attaches to the two disk drives. The single connector at the other end goes to the controller module, and is attached with the colored stripe to the left of connector P4 as shown in Figure 2-4. As seen in the figure, pin 2 and the colored stripe are at the left of the connector when properly installed. The colored stripe encloses the wire to pin 1.

- Connect one or both of the disk drive cable connectors to the back of the disk drive(s). See the manufacturer's installation instructions for proper orientation of pin 1 on the disk drive connector. Pin 1 on the TM 990/527 cable is denoted by a diamond engraved in the connector on the side near the colored stripe. See Figure 2-5 for orientation. If pin 1 is on top of the edge connector at the disk drive, the diamond on the connector must also be on top, oriented with that pin.

FIGURE 2-3. SYSTEM INTERCONNECTIONS USING TM 990/527 CABLE (STANDARD SIZE)

#### NOTE

If you want to make your own cable, be aware that the connector plugs of various vendors, including TI, do not necessarily use the numbering schemes on the module edge connector. ALWAYS refer to the board edge connector configuration when wiring a connector. Connector pinouts are listed in Appendix F.

FIGURE 2-5. TM 990/527 CABLING BETWEEN CONTROLLER AND EIGHT-INCH DRIVES

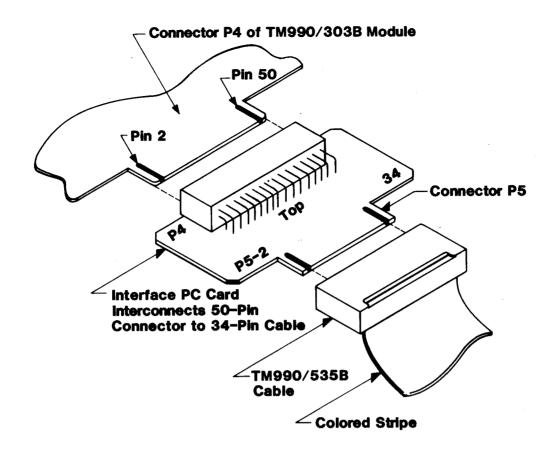

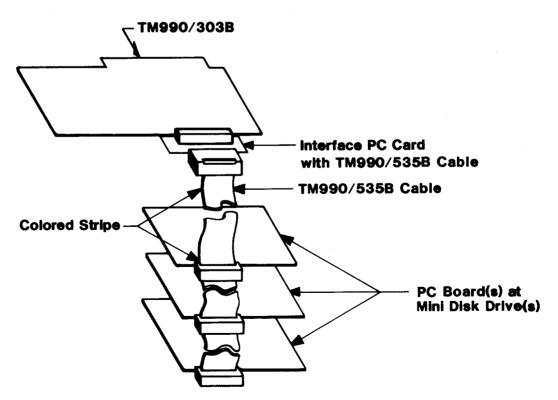

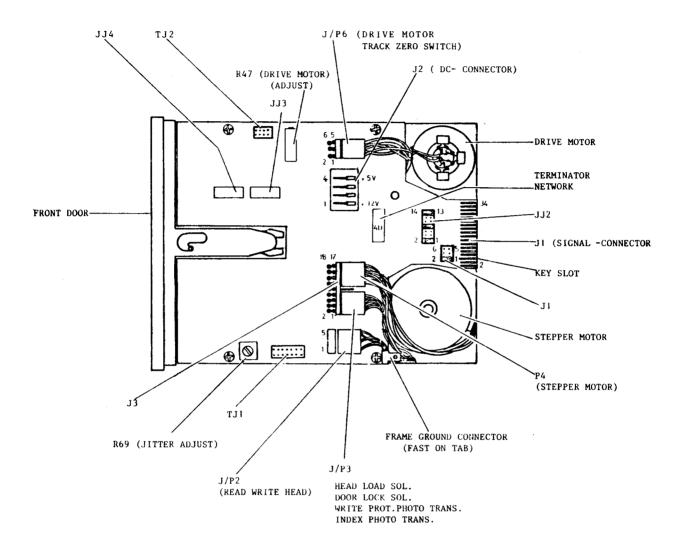

Figures 2-6 and 2-7 show similar cabling for five-inch mini drives using the TM 990/535B cable and its interface card. The card acts as the interface between the 50-pin connector P4 on the TM 990/303B module and the 34-wire cable.

Appendix F contains pin designations of both cables.

FIGURE 2-6. CONNECTING TM 990/535B DISK DRIVE CABLE TO P4 OF TM 990/303B MODULE

FIGURE 2-7. TM 990/535B CABLING BETWEEN CONTROLLER AND MINI DISK DRIVES

#### 2.8 SYSTEM CHECK AND POWER APPLICATION

Do not apply power until the PC cards (TM 990/303B as well as the disk drive) are properly jumpered and installed and cables are connected as specified in section 2.7. Before applying power, use the following checklist to verify proper installation according to applicable sections, figures, and tables: