As you are now the owner of this document which should have come to you for free, please consider making a donation of £1 or more for the upkeep of the (Radar) website which holds this document. I give my time for free, but it costs me around £300 a year to bring this document to you. You can donate here <a href="https://blunham.com/Radar">https://blunham.com/Radar</a>, thank you.

Do not upload this copyright pdf document to any other website. Breaching copyright may result in a criminal conviction and large payment for Royalties.

This document was generated by me, Colin Hinson, from a document held at R.A.F. Henlow Signals Museum which is believed to be out of copyright or Crown Copyright. It is presented here (for free) under the Open Government Licence (O.G.L.) if under Crown Copyright and this version of the document is my copyright (along with the Crown Copyright) in much the same way as a photograph would be. It should be noted that most of the pages are identifiable as having been processed by me. If you believe the original document to be under copyright, please contact me.

The document should have been downloaded from my website <a href="https://blunham.com/Radar">https://blunham.com/Radar</a>, or any mirror site named on that site. If you downloaded it from elsewhere, please let me know (particularly if you were charged for it). You can contact me via my Genuki email page: <a href="https://www.genuki.org.uk/big/eng/YKS/various?recipient=colin">https://www.genuki.org.uk/big/eng/YKS/various?recipient=colin</a>

You may not copy the file for onward transmission of the data nor attempt to make monetary gain by the use of these files. If you want someone else to have a copy of the file, point them at the website (<a href="https://blunham.com/Radar">https://blunham.com/Radar</a>). Please do not point them at the file itself as it may move or the site may be updated.

\_\_\_\_\_

I put a lot of time into producing these files which is why you are met with this page when you open the file.

In order to generate this file, I need to scan the pages, split the double pages and remove any edge marks such as punch holes, clean up the pages, set the relevant pages to be all the same size and alignment. I then run Omnipage (OCR) to generate the searchable text and then generate the pdf file.

Hopefully after all that, I end up with a presentable file. If you find missing pages, pages in the wrong order, anything else wrong with the file or simply want to make a comment, please drop me a line (see above).

If you find the file(s) of use to you, you might like to make a donation for the upkeep of the website – see <a href="https://blunham.com/Radar">https://blunham.com/Radar</a> for a link to do so.

Colin Hinson

In the village of Blunham, Bedfordshire, UK.

# Proposed new No Break Trigger system designed by

# Chief Technician Colin Hinson

## and

# Sergeant Tony Mellor

After some 6 years of operation it became apparent that the original No Break Trigger system was a cause of many hours of the station being "off the air". Tony and I therefore decided that we would have a go at designing a semiconductor version of the (then) current valved system.

We designed what you see in this document between us and solved the problems that cropped up between us so that we both knew how the whole thing worked. The printed circuit boards were designed and made by us using copper plated boards from Vero Electronics who also supplied the 19 inch rack assembly.

Having got the "box" working, we obtained permission to connect it as the trigger source for the Type 85 radar, along with its ancilliary equipments (such as IFF etc). To my knowledge this ran for at least 5 years with no problems.

This document is the original scanned version. A modernised version of the document are available on this site. Colin Hinson, Oct. 2017.

# PROPOSED NEW NO-BREAK TRIGGER SYSTEM

## SECTION 1 - NEW NET SYSTEM

#### General Introduction

1. This paper discusses a design for a No-Break Trigger System thich could be utilised at R.F radar stations where a high standard of timing precision and reliability is required. The equipment is capable of working in a wide range of environments and over the temperature range 0.0 to 50.0 requires no forced air cooling.

#### NBT System

- 2. ADRS's are triggered from an NBT equipment developed from early synchronising systems. This equipment has since its introduction been considerably modified in an effort to increase its reliability. However its serviceability still falls short of a working ideal.

- 3. The new NBT system is introduced in order to improve reliability and service-ability of the trigger system.

#### General Equipment Description

- 4. The equipment is mounted on 5 basic types of printed circuit board which are housed in a "Verorack", 19" rack assembly. This rack will mount directly into a 7' Sainsbury cabinet.

- 5. Power supplies are mounted in the same cabinet and are fed from the A.C. nains supply. Bulk D.C. power supplies are not required.

#### System Description

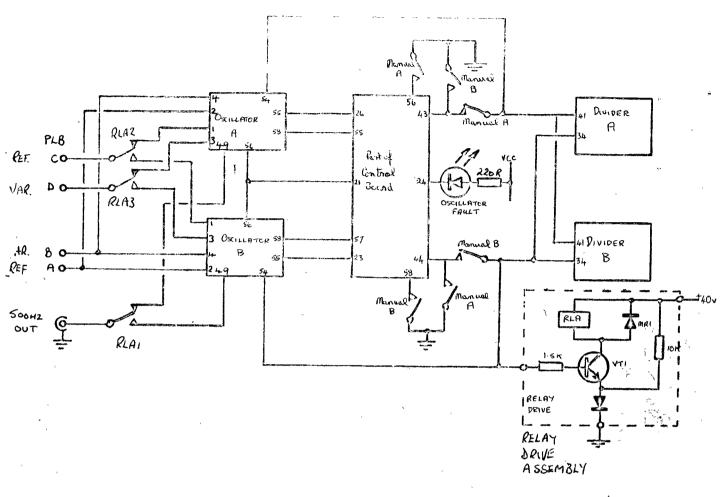

- 6. The equipment contains duplicated crystal oscillators, dividers and trigger output circuits. Each major sub-division of the equipment is mounted on its own printed circuit board. All active auto-changeover components are mounted together on one board, the system may be run manually with all automatic fault detection circuitry disabled on removal.

- 7. The input to the system is designed to interface with the PRF control system in the Radar Type 84 MTI equipment.

- 8. The output triggers are compatible with the trigger inputs to all the equipments currently in use at ADRS's.

- 9. The existing underfloor mounted pulse distribution unit and the wall mounted pulse indicator panel are not required with the proposed system.

#### SECTION 3 - BRIEF TECHNIC L DESCRIPTION OF SYSTEM

Refer to innex

#### Oscillator Poard

- 1. The 4Mhz oscillator is similar to the one used in the present MBT system, this is so that compatibility between the unit and the external PRF control system may be maintained. The 4Maz nominal crystal frequency is converted to TTL levels and divided by 16 before leaving the board. The 250 kHz output is routed to both divider boards, the switching between main and standby oscillators is accomplished electronically on the divider boards.

- 2. A 500 Hz square to sine convertor is also housed on this board, this accepts a 500 Hz legic level square wave from the in use divider. The 500 Hz sine wave output is routed to the PRF central system.

- 3. Both the 250 kHz and the 500 Hz signals are checked to ensure correct operation by the fault detection eigenst on the board. The output of the fault detector is fed to the central board where it is used to initiate auto changeover in the event of a failure.

- 4. LEDs indicating "In Use" and "Fault" conditions are mounted on the front panel.

#### Divider Board

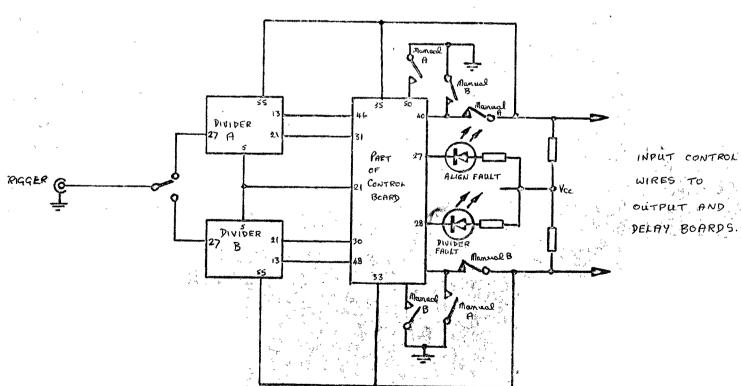

- 5. The 250 kHz signal from the in use escillator is divided by a series of bistables down to 250 Hz. Gating circuits accept outputs from individual bistables and generate the six timing pulses.

- 6. In align facility is provided so that the divider which is not currently in use may be kept exactly in step with the in use divider. This ensures that the output pulses from each board are precisely in line with each other and no timing errors will occur if changeover of divider boards takes place.

- 7. Each output from the board is monitored and a fault signal is sent to the control board should any output become unserviceable. In addition to the pulse outputs a 500 Hz square wave is sent from the in use board to the oscillator.

- 8. The front panel carries "In Use" and "Fault" indicators.

#### Output Board

- 9. Two boards are used simultaneously to provide the output triggers, however the output circuit configuration is such that if one driver fails the other will continue to function and no loss of triggers will occur.

- 10. Both dividers feed the boards, selection of a particular divider is performed by the input sating on the output boards.

- 11. Each board has 6 outputs of 35 volt, 4ms wide positive going pulses.

Additional triggers are catered for by providing extra pairs of boards. The front panel carries monitor sockets and trigger presence indicators.

#### SECTION 2 - SYSTEM SPECIFIC TION

PRF Controlled by crystal stabilised oscillator, fine control

by T84 MTI system.

Basic PRF = Crystal frequency (kHz) pps.

PULSE TIDTH 4us.

500 Hz REFIRENCE Subdivision of oscillator frequency.

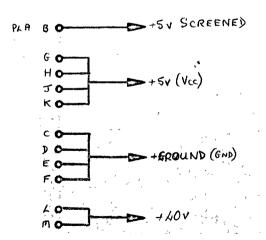

POWER REQUIREMENTS 5 volts at 3 amperes + 5%

40 volts at 1 ampere ± 5,3

OUTPUT TIMINGS Fixed triggers, referenced to "Zero" trigger.

(1) Zero

(2) -8us.

(3) -125us.

(4) -25**Q**us.

$(5) -75 \cos$ .

Delayed triggers, delayed by from 2us to 15 Ous on any of the fixed triggers.

TRIGGERS AVAILABLE Each delay board gives 4 outputs and each output board

gives 6 outputs. The basic system may be extended in

multiples of these figures by adding additional pairs of boards.

TRIGGER OUTPUT Both the delay and the output boards use the same

output circuit configuration. The output is capable of producing 100ns rise time triggers at the remote end of 100 metres of UR70 cable. The rise time is only degraded to 25 Ons when driving 800 meters of low loss cable.

The output is open and short circuit proof.

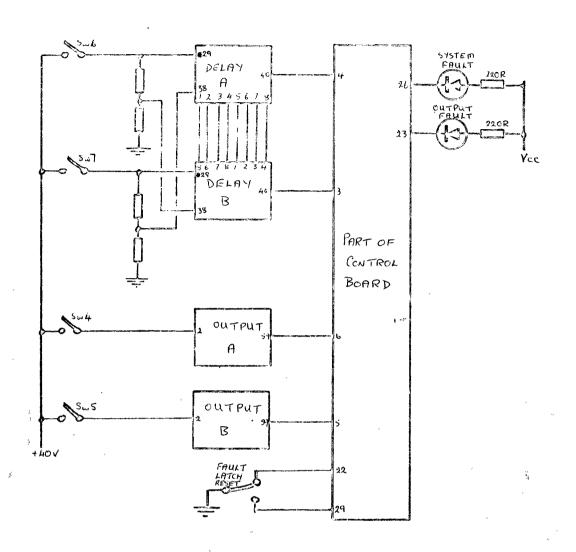

#### Delay Board

- 12. This board accepts the outputs from the dividers and produces delayed triggers 35 volts amplitude and 4us wide.

- 13. Each pair of delay boards have their delay circuits cross coupled, this ensures that both boards produce outputs at the same time even if one delay has been incorrectly set.

- 14. The front panel carries monitor sockets, trigger presence indicators and delay controls.

#### Control Board

- 15. The control board monitors the sutputs of every other board within the system and controls the automatic changeover between boards. The power supplies are monitored but since they operate in parallel no switching is necessary.

- 16. When any fault is detected an alarm signal is generated and a record of the part of the equipment which failed is kept. This record is in the form of a LED display on the control panel which is kept lit until reset manually.

Power Supplies

- 17. Supplies of 5 volts and 40 volts are used within the system. Small modular units are used fed from the 240 volt mains supply. Duplicate supplies are paralleled together, this ensures operation without break in the event of supply failure and eliminates the need for switching.

# SECTION 4 - DETILED TECHNICAL DESCRIPTION

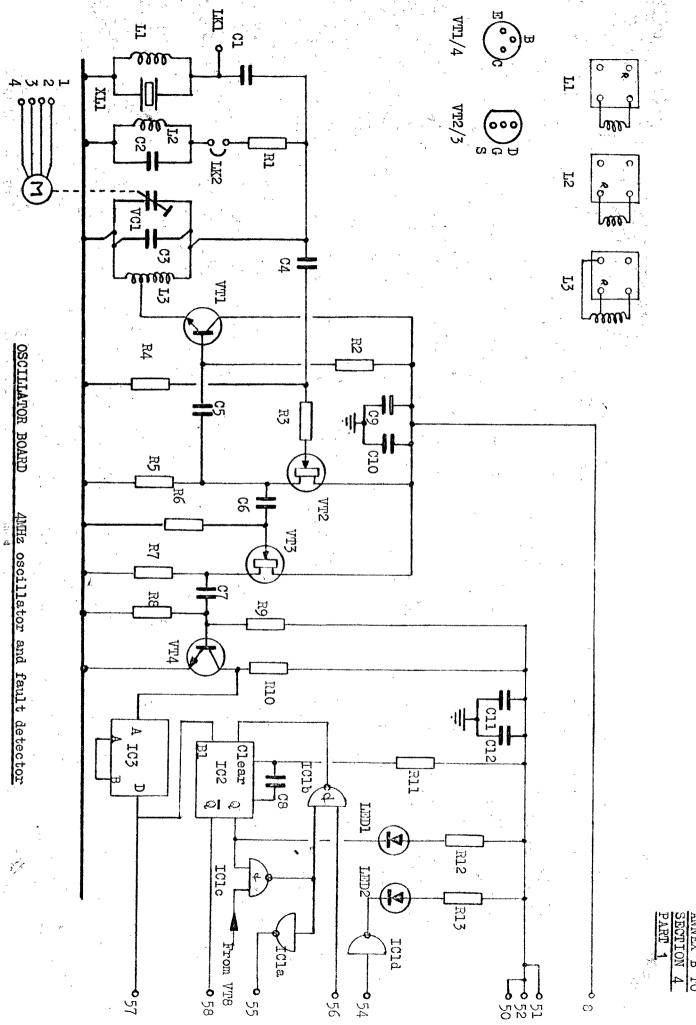

Part 1 - Oscillator board

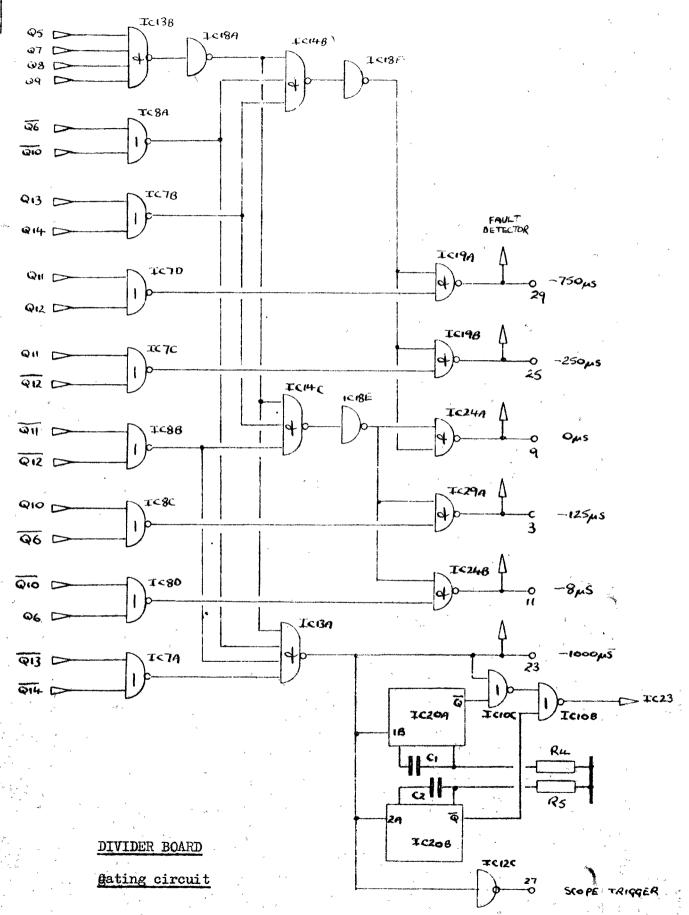

Part 2 - Divider board

Part 3 - Output board

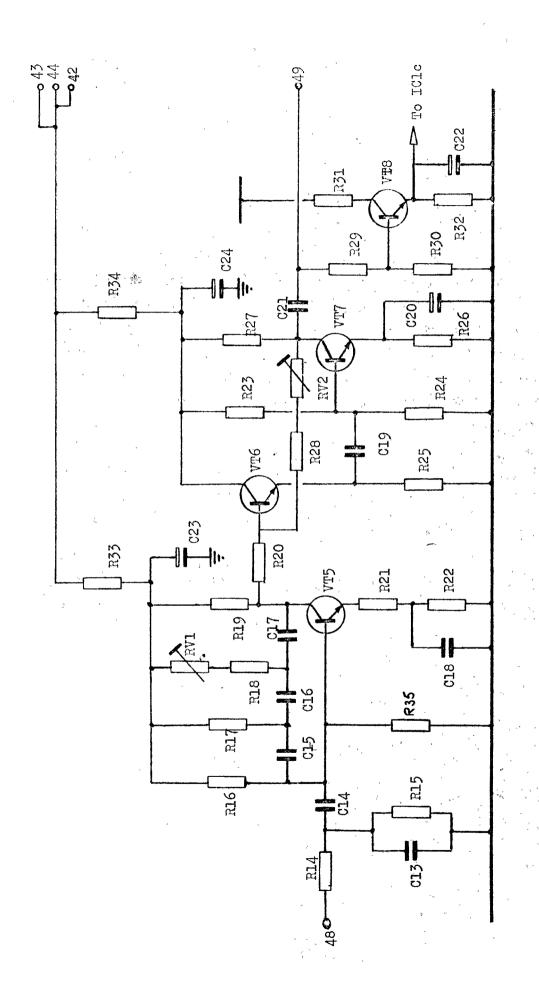

Part 4 - Delay board

Part 5 - Control board and control panel

Part 6 - Rack wiring

#### SECTION 4 - PART 1 - OSCILLATOR BOLD

#### General Description

1. The oscillator board provides the highly stable frequency used to feed the divider boards. It also accepts a 500 hz square vave from the in use divider will converts this into a sine wave for use in the T84 signal processing system.

The oscillator is of the inverted Hartley type with VT2 source following

2. The board is powered from the 5 volts and 40 volts supply.

#### Oscillator

3.

- into TT1, thus providing a high impedance input and a low impedance feedback path to the tap of L3. The main resonant circuit consists of L3, C3 and variable canacitur VCI. The oscillator is stabilized by crystal XLI and is eapable of boild swung +20 kHz about the crystal frequency of 4.008 or 4.078 MHz by VC1. L1, L2, Cl. C2 and R1 form the network required to breaden the basic crystal response. A second source follower, WI, is fed from VI2, this isolates the oscillator from the waveform shaper VT4. Capacitor VC1 is motor driven and is controlled by the P.R.F. controller in the cancellation cabinet of the T84 signal processing. VT4 squares the output from the oscillator and feeds directly into IC3. a four bit binary counter. The 250 KBz output from IC3 is taken from the board and feeds the two divider beards. The 250 KHz output also feeds IC2 which is a retriggerable monostable. The timing cycle of IC2 is set by C8 and R11 to be 5uS. Since the periodic time of the input is 4uS, the monostable will be retriggered before the completion of the timing cycle and therefore the 2 output will remain at logical 1 and the 2 at logical 6. Should the oscillator/4 bit counter fail then the monostable will revert to its stable state within SuS. The Q will go to logical O and be inverted trice by IClc and IClb and present a logical 0 at the clear input of BC2. This will hold the Q at logical 0 and

- therefore the monostable will latch in its stable state. The fault output from the  $\overline{Q}$  is fed to the control board fault circuitry. The Q output going to logical Q grounds the cathode of LED1, the fault indicator causing it to light.

- The logical O output of ICLA is fed from the board to light the Oscillator fault LED on the centrel panel. The reset line for the monostable comes from the

- pulse generator on the control board to IClb. When this line goes to logical 0 it allows the clear line to go to logical 1. If the fault is cleared, the monostable will be retriggered by the 250 KHz and allow the clear to remain at

- logical 1 when the reset pulse ends and both fault LEDs will go out.

- 5. If the fault persists, the monostable will not retrigger and the fault output from the  $\bar{\mathbf{Q}}$  will remain at logical 1.

#### 500Hz Generator

6. A square wave at 500Hz is taken from the in use divider and fed to VT5 via the shaping network R14, R15, C13, and C14. VT5 is arranged as a phase shift oscillator but with insufficient gain to sustain oscillation independently due to the undecoupled emitter resistor R21. The application of the shaped square

## 500Hz Generator (Continued)

wave to VT5 causes it to oscillate, locked in phase to the 50CHz sub-multiple of the crystal frequency. RV1 sets the gain of VT5 to a maximum over the required range and only requires adjustment when the crystal frequency is changed.

- 7. The sine wave output of VT5 is buffered by emitter follower VT6 and fed to amplifier VT7. Negative feedback is taken from VT7 collector to VT6 base, the amount of feedback being set by RV2. Thus RV2 adjusts the gain of VT6 and VT7 and so sets the amplitude of the output sine wave.

- 8. A sample of the output is taken to VTS through R29. The positive peaks of the sinewave cause VTS to conduct allowing C22 to charge up through VTS and R31.

C22 is normally charged to approximately 4 welts, holding the input to IC1c at logical 1. If the 500Hz fails, VTS is cut off and C22 discharges through R32.

R32 is sufficiently low in value to pull down the input to IC1c to logical 0 and the monostable will latch as before. The time taken for C22 to discharge through R32 to below the threshold of IC1c introduces a short delay in the time taken for the 500Hz fault circuit to trip. This ensures that in the event of a divider failure causing loss of 500Hz, the divider changeover will operate before the loss of 500Hz is detected.

- 9. To indicate the in use oscillator eard, an in use signal is fed from the oscillator selection switch to ICld. When the in use signal is at logical 1 the output of ICld goes to logical 0 causing the in use light LED2 to come on.

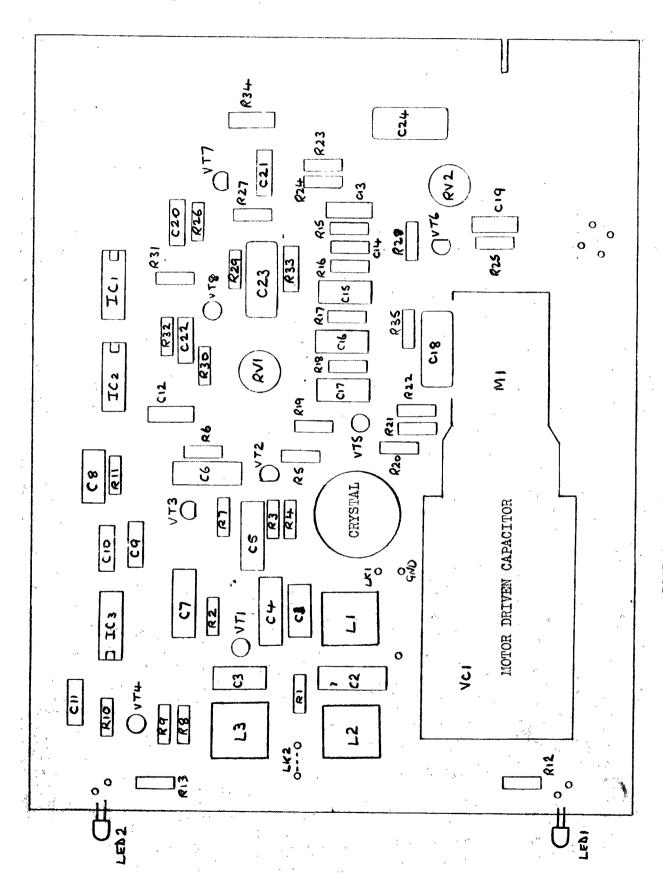

OSCILLATOR BOARD Layout

# OSCILLATOR BOARD - LIST OF COMPONENTS

| ANNEX  | D  | TO |

|--------|----|----|

| SECTIO | MC | 4  |

| PART : | Ĺ  |    |

|       |               |             | • |                  | Fil            | <u> </u> |           |

|-------|---------------|-------------|---|------------------|----------------|----------|-----------|

| R1    | 470R          | LOW 0136108 |   | Cl               | 10p.c          | 10C      | 0126774   |

| R2    | 56k           | 9136158     |   | C2               | lnF            |          |           |

| R3    | 390R          | 0136106     |   | C3               | 10pF           |          | 0126774   |

| R4    | 100k          | 0136164     |   | 04               | 100pF          |          |           |

| RĴ    | 1k0           | 0136116     |   | C5               | 12 pm          |          |           |

| R6    | 390k          | 0136057     |   | <b>c</b> 6       | 12pF           |          |           |

| R7    | 1k2           | 0136118     |   |                  | 150pF          |          |           |

| R8    | 18k           | 0136146     |   | C7<br>C8         | 199 <u>5</u> 1 |          |           |

| R9    | 10k<br>56k    |             |   |                  |                |          | 07.30 100 |

| R10   | -             | 0136158     |   | C9               | 15uF           |          | 0130 ;98  |

|       | 1k8           | 0124709     |   | C10              | 220nF          |          | 1953299   |

| R11   | 15k           | 0136144     |   | C11              | 220nF          |          | 1953299   |

| R12   | 270R          |             |   | C12              | 220nF          |          | 1953299   |

| R13   | 270R          |             |   | C13              | 100nF          |          |           |

| R14   |               |             |   | C14              | 100pF          |          | 9467456   |

| R15   | 6k8           | 0136136     |   | C15              | 10nF           |          | 9521641   |

| R16   | 56k           | 0136158     |   | C16              | 10nF           |          | 95216.41  |

| R17   | 15k           | 0136144     |   | C17              | 10nF           |          | 95216.‡1  |

| R18   | 12k           | 01361.2     |   | C18              | +7uF           |          | 0131425   |

| R19   | 12k           | 0136142     |   | C19              | 470nF          |          | #31 J     |

| R20   | 100k          | 0136164     |   | 020              | 15uF           |          | 0130498   |

| R21   | 27R           | 013010      |   | C21              | 470nF          |          | 0130-730  |

| R22   | 82 <b>0</b> R | 0136114     |   | 022              | 15uF           |          | 0130498   |

| R23   | 10k           | 0136140     |   | C23              | 56 <b>uF</b>   |          | 1021722   |

| R24   | 1k8           | 0124709     |   | C24              | 56uF           |          | 1021722   |

| R25   | 4k7           |             |   | V24              | Joan           |          | TOSTICS   |

| R26   |               | 0124739     |   |                  |                |          |           |

|       | 330R          | 0136104     |   | 77/73            | . 01⊞          |          | 07 (7 000 |

| R27   | 1k2           | 0136118     |   | VCl              | <b>8-</b> 81pF |          | 0161008   |

| R28   |               |             |   |                  |                |          |           |

| R29   | - 000         |             |   |                  |                |          |           |

| R30   | 100k          | 0136164     |   | Ll               |                |          | 9132586   |

| R31   | 100R          | 01          |   | $\mathbf{r}_{S}$ |                |          | 91 32 581 |

| R32   | 68 <b>0</b> R | 0136114     |   | L3               |                |          | 9132584   |

| R33   | 22k (1W)      |             |   |                  |                |          |           |

| R34   | 1k5 (17)      | 0135750     |   |                  |                |          |           |

| R35   | 4k7           | 0124739     |   | VTl              | 2N916          |          |           |

|       |               |             |   | VT2              | 2N3319         |          |           |

|       |               |             |   | VI3              | 2N3319         |          |           |

|       |               |             |   | VT4              | 2N916          |          |           |

|       |               |             |   | VT5              | 2N916          |          |           |

| RV1   | 4k7           |             |   | VT6              | 2N3705         |          |           |

| RV2   | 1MO           |             |   | VT7              | 2N 3705        |          |           |

| 111 ~ | Time          |             |   | VI8              | BC107          |          |           |

|       |               |             |   | 110              | DOTO           |          |           |

|       |               |             |   | ICl              | SM7493N        |          |           |

|       |               |             |   | IC2              | SN74122N       |          |           |

|       |               |             |   | IC3              | SN7400N        |          |           |

| •     |               |             |   |                  |                |          |           |

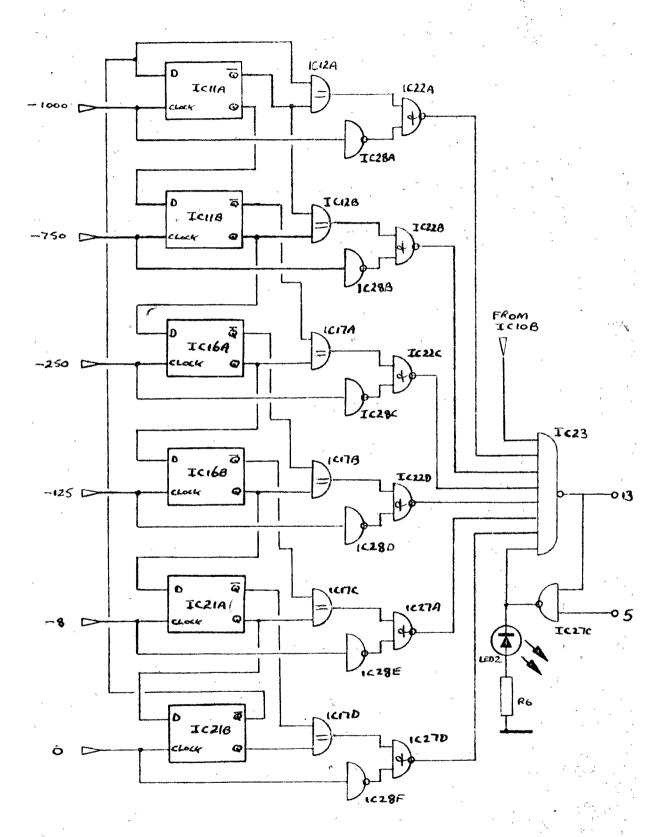

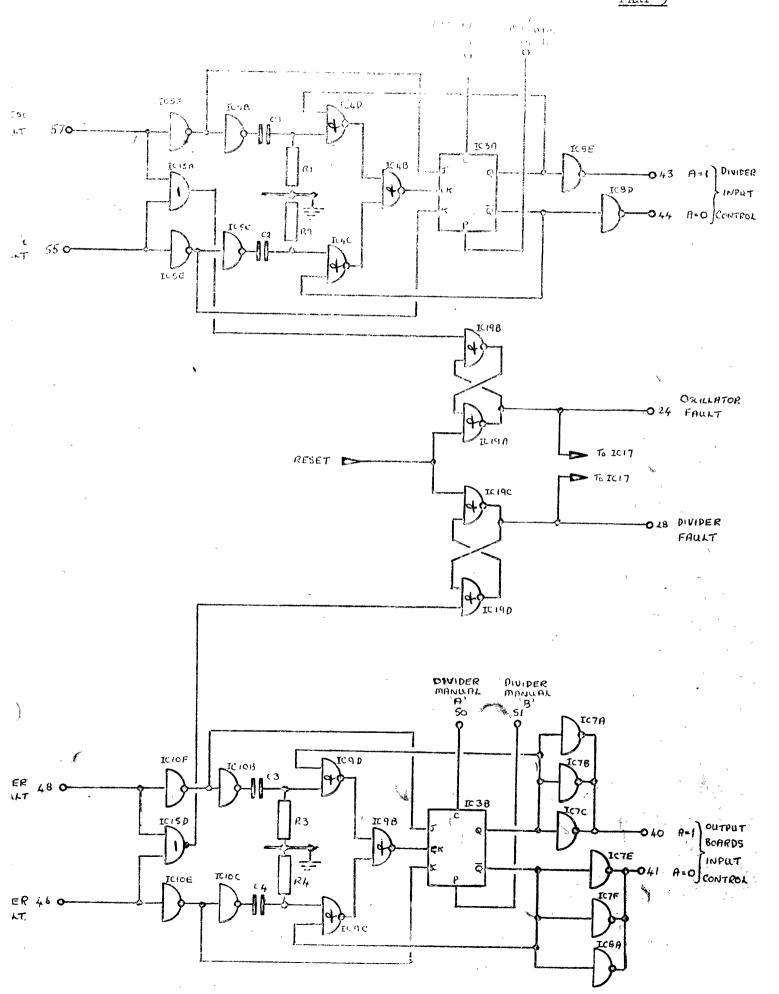

#### SECTION 4 P.RT 2 - DIVIDER BOARD

- 1. This board accepts 3 250KHz inputs, one from each of the two oscillators and one from an external signal source. One of these inputs is selected for use and then divided down to 250Hz by a ten stage binary counter.

- 2. 6 pulses each 4uS wide are obtained by gating the binary counter outputs, their timings are (with respect to zero, and assuming a P.A.2. of 250pps), -1000uS, -750uS, -250uS, -125uS, -8uS, and zero. 5 of these pulses are fed to the Output boards and the Delay boards, the -1000uS pulse is used on the control board. The 6 pulses are checked both for presence and correct sequence. In additional check performed on the -1000uS pulse ensures that the P.R.F. of the outputs is of the correct order.

- 3. The TTL counter has an 'Align' facility, this enables the standby divider to be run in exact synchronism with the in use divider.

#### Circuit Description

- 4. The input gating from the Control Panel is used to set bistable IC30c & d. The bistable outputs enable IC15a and allow the oscillator signal through, or enable IC15b allowing the B oscillator through. If SWIa is in the Ext position both IC15a and IC15b are disabled, IC14a is enabled allowing an external signal to be applied to the divider.

- 5. The selected input is fed via ICl5c to the ripple counter chain which consists of 4 bit binary counter IC9 followed by 6 JK flip flops IC2, 3, and 4. These flip flops are used in the \*2 mode, with their J inputs connected to their Q outputs and K inputs connected to 4 outputs to avoid having to connect them to VCC.

- 6. The align input is applied to all flip flops and inverted by IC18C before being applied to IC9. A logical 0 on this line will clear the flip flops and the logical 1 from IC18c will clear IC9. SW16 inhibits the align when an external signal is used to drive the divider.

#### Output Gating Circuit

7. The output gating circuit provides the 4uS wide pulses at the required timings. The Q and  $\frac{1}{2}$  outputs of the counter are the inputs to the gating circuit, To minimise the effects of propagation delay through the counter chain  $\frac{1}{2}6$  is delayed by passing it through successive stages of inversion in IC5a, b and c. The various triggers are produced in accordance with the truth table belows-

|         | <b>Q</b> 5 | <b>Q6</b> | <b>Q7</b> | <b>ą</b> 8 | <b>Q</b> 9 | 210 | ગુ11 | ગ્ર12 | <b>Q13</b> | 114 |

|---------|------------|-----------|-----------|------------|------------|-----|------|-------|------------|-----|

| -1000uS | 1          | 1         | 1         | 1          | 1          | 1   | 1    | 1     | 1          | 1   |

| -750uS  | 1          | 1         | 1         | 1          | 1          | 1   | 0    | 0     | 0          | Q   |

| -250uS  | 1          | 1         | 1         | 1          | 1          | 1   | 0    | 1     | 0          | 0   |

| -125uS  | 1          | 1         | 1         | 1          | 1          | O   | 1    | 1     | 0          | 0   |

| -8uS    | 1          | 0         | 1         | 1          | 1          | 1   | 1    | - 1   | 0          | 0   |

| OuS     | 1          | 1         | 1         | 1          | 1          | 1   | 1    | 1     | 0          | 0   |

MAVIDER BOARD Fault detector

DIVIDER BOARD Layout

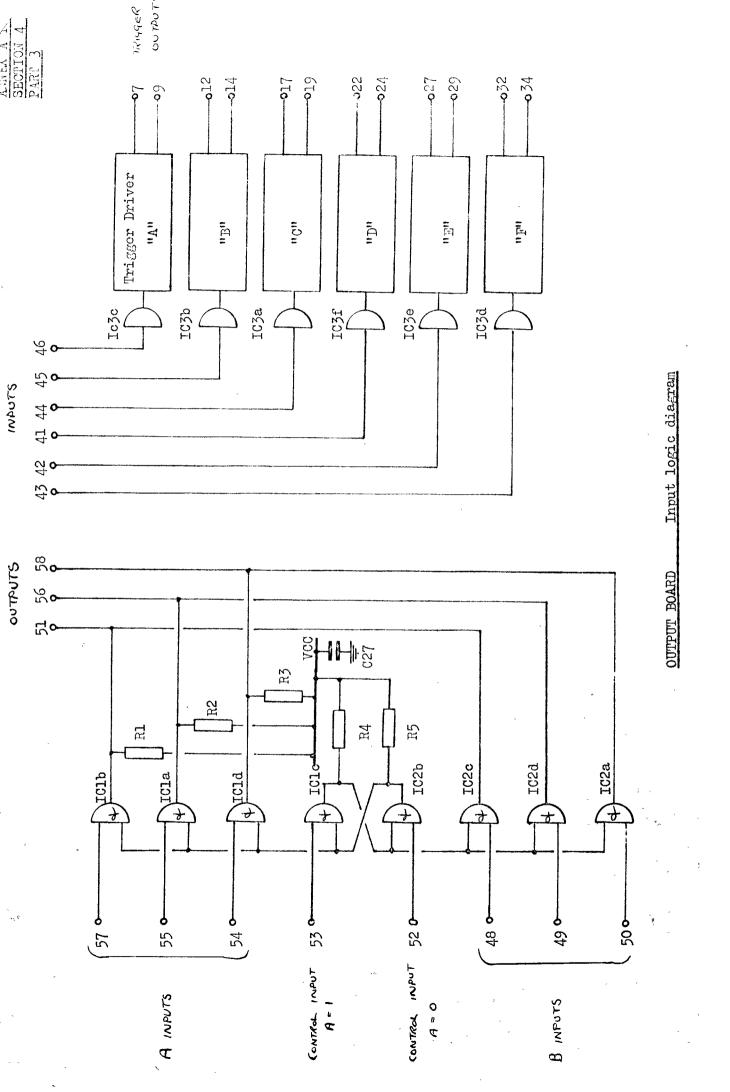

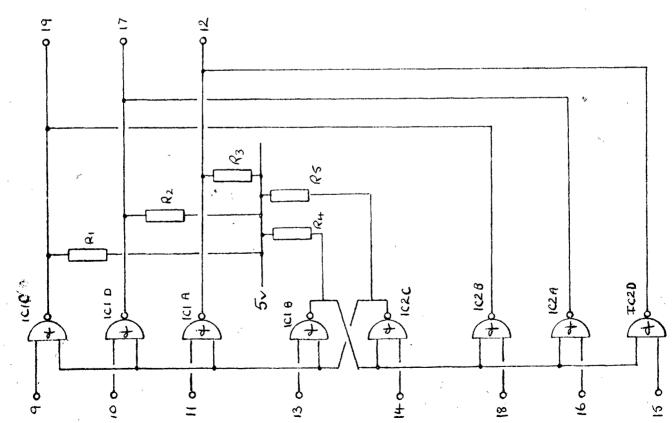

#### SECTION 4 - PART 3 - OUTPUT BOARD

#### General Description

1. This board accepts three inputs from each divider board at TTL logic levels. Each board produces six 35 volt, 4uS positive going triggers. The board is powered from the 5 volt and the 4 0 volt power supplies.

#### Circuit Description

- 2. Input gating The divider A or B selection is carried out on the output bound by ICl and IC2. IClc and IC2b form a cross coupled MAND bistable whose state depends on the control signal coming from the selector switch S<sup>N</sup> on the Control Panel. The purpose of this bistable is to ensure that only one divider is selected at one time. When the bistable is in the 'A' position due to a logical O at pin 52, a logical 1 is applied to the gating inputs of ICla, b and d, allowing the input from divider A to pass through the gates. A logical O is applied to the gating inputs of IC2a, c and d thereby inhibiting the inputs from divider B. When a logical O is applied to pin 53 the gating is reversed, B inputs being allowed through and A inputs inhibited.

- 3. The three outputs of the gating circuit are fed out from the board on pins 51, 56 and 58 and externally wired to the six inputs on pins 41 to 46. Each trigger is buffered and inverted by one element of IC3 and fed to the discrete component trigger driver.

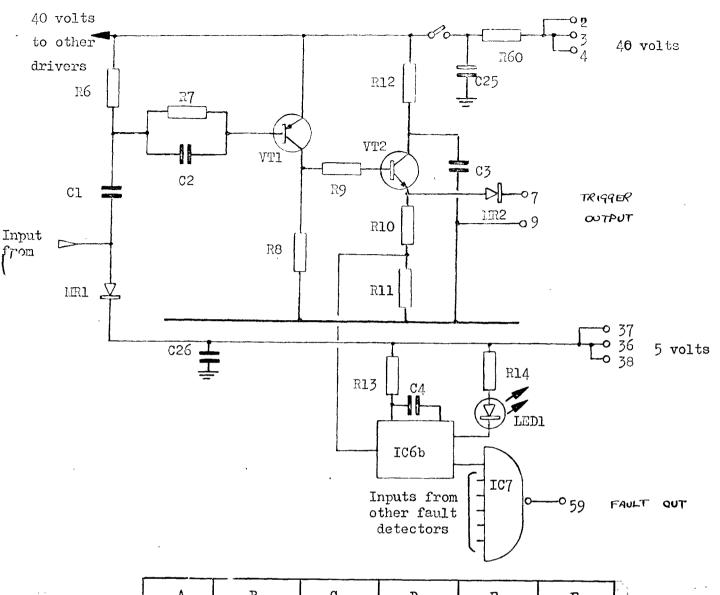

#### Trigger Driver

- Note: Description is given for trigger driver A, see table for other driver component references.

- 4. The trigger is fed from IC3a through C1 and R7, C2 to the base of WT1. Diode MR1 prevents the output of IC3c being pulled above 5 volts by C1 charging during switch on.

- 5. VTl is normally non-conducting and is driven into conduction by the trigger input. When VTl conducts, the junction of R8 and R9 is pulled up to the 40 volt rail. Base current to turn on VT2 is supplied through R9. C3 and VT2 form a capacitive discharge circuit into the load. C3 is kept charged by current through R12.

- 6. Isolating diode MR2 enables the outputs from two boards to be paralleled to provide back-up should one driver fail.

- 7. A portion of the output is tapped from potential divider R10, R11 and fed to the fault detector IC6b.

#### Fault Detector

8. The output trigger sample is fed to the retrigger ble monostable multivibrator IC6b which timing period is set by R13 and C4 to be 5nSecs. As the pulse spacing is approximately 4nS the monostable will be retriggered before the completion of its timing cycle. The Q output of IC6b will therefore remain at a logical 1 and the  $\overline{Q}$  at logical 0, lighting the trigger presence indicator LED1.

## Fault detector (continued)

- 9. Should any trigger fail, the appropriate LED will extinguish and the 2 of the fault detector will go to logical 0. The presence of a logical 0 at any input of IC7 will cause its output to go to logical 1 signalling a fault to the control board circuitry.

- 10. Since two separate drivers are simultaneously providing each trigger, no change-over need take place if one trigger driver output fails.

1k5 1k5 1k5 680R 220R 18R 5k6 33k 270R 4.7nF 100pF 0.47uF 0.47uF CV 7676 CV 7725 CV7128 CV 7368 TIL 209 SN74123N Output pin Output ground

| A                                                                                                                                             | В                                                                                                                                                   | С                                                                                          | D                                                                                                                                                | E                                                                                                                                                         | F                                                                                                                                           |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|

| R6<br>R7<br>R8<br>R9<br>R10<br>R11<br>R12<br>R13<br>R14<br>C1<br>C2<br>C3<br>C4<br>VT1<br>VT2<br>MR1<br>MR2<br>LED1<br>166b<br>pin 7<br>pin 9 | R15<br>R16<br>R17<br>R18<br>R19<br>R20<br>R21<br>R22<br>R23<br>C5<br>C6<br>C7<br>C8<br>VT3<br>VT4<br>MR3<br>MR4<br>LED2<br>IC6a<br>pin 12<br>pin 14 | R24 R25 R26 R27 R28 R29 R30 R31 R32 C9 C10 C11 C12 VT5 VT6 MR5 MR6 LED3 IC5b pin 17 pin 19 | R33<br>R34<br>R35<br>R36<br>R37<br>R38<br>R39<br>R40<br>R41<br>C13<br>C14<br>C15<br>C16<br>VT7<br>VT8<br>MR8<br>LED4<br>IC5a<br>pin 22<br>pin 24 | R42<br>R43<br>R44<br>R45<br>R46<br>R47<br>R48<br>R49<br>R50<br>C17<br>C18<br>C19<br>C20<br>VT9<br>VT10<br>MR9<br>MR10<br>LED5<br>IC4b<br>pin 27<br>pin 29 | R51<br>R52<br>R53<br>R54<br>R55<br>R56<br>R57<br>R58<br>R59<br>C21<br>C22<br>C23<br>C24<br>VT11<br>VT12<br>LED6<br>IC4a<br>pin 32<br>pin 34 |  |

COUTPUT BOARD - LAYOUT DIAGRAM

| OTHER THE  | 2010 TES | T OF COMPONENTS       |           |                   | ANNEX D TO<br>SECTION 4<br>PART 3 |

|------------|----------|-----------------------|-----------|-------------------|-----------------------------------|

| R1         | 1k5      | 107 0136120           | Cl        | <sub>4</sub> 700p | 100 9548817                       |

| R2         | 1k5      |                       | C2        | 100p              | 100 9467456                       |

| R3         | 1k5      |                       | <b>C3</b> | 0.47uF            | polycurbonate 100v.               |

| R4         | 1k5      |                       | 04        | 0.47 <b>u</b> F   |                                   |

| R5         | lkj      |                       | C25       | 10uF              | electrolytic 100v.                |

| R6         | 1k5      |                       | C26       | 0.22uF            | 100 1953299                       |

| R <b>7</b> | 1k5      |                       | C27       | 0.22uF            |                                   |

| R9         | 680R     | 1077 136112           | •         |                   |                                   |

| R10        | 220R     | 10\ 136100            |           |                   |                                   |

| 211        | 18R      |                       |           |                   |                                   |

| R12        | 5k6      | 107 136134            |           |                   |                                   |

| R13        | 33k      | 107 136152            |           |                   |                                   |

| R14        | 270R     |                       |           |                   |                                   |

|            |          |                       |           |                   |                                   |

|            |          |                       |           |                   |                                   |

| VTl        | cv 7676  | 10CV 0374448          |           |                   |                                   |

| A.I.S      | CV 7725  | 100V 03745 <b>7</b> 2 |           |                   |                                   |

| MRl        | CV 7128  | 10CV 0373140          |           |                   |                                   |

| IIR2       | CV 7128  | 1007 0373140          |           |                   |                                   |

|            |          |                       | •         |                   |                                   |

| ICl        | SN7.403  |                       |           |                   |                                   |

| IC2        | SN7403   |                       |           |                   |                                   |

| IC3        | SN7.404  | 10CY 1181748          |           |                   |                                   |

LED1/6 TIL209

SN74123

Sn74123

SN74123

SN7430

JOCA

IC4

IC5

IC6

IC7

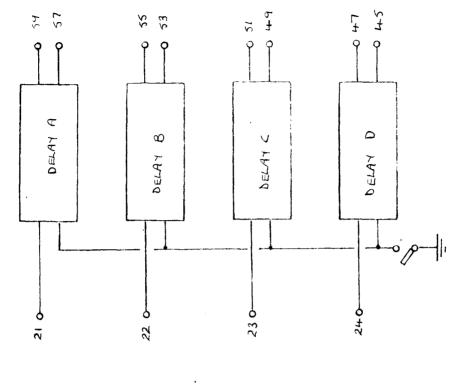

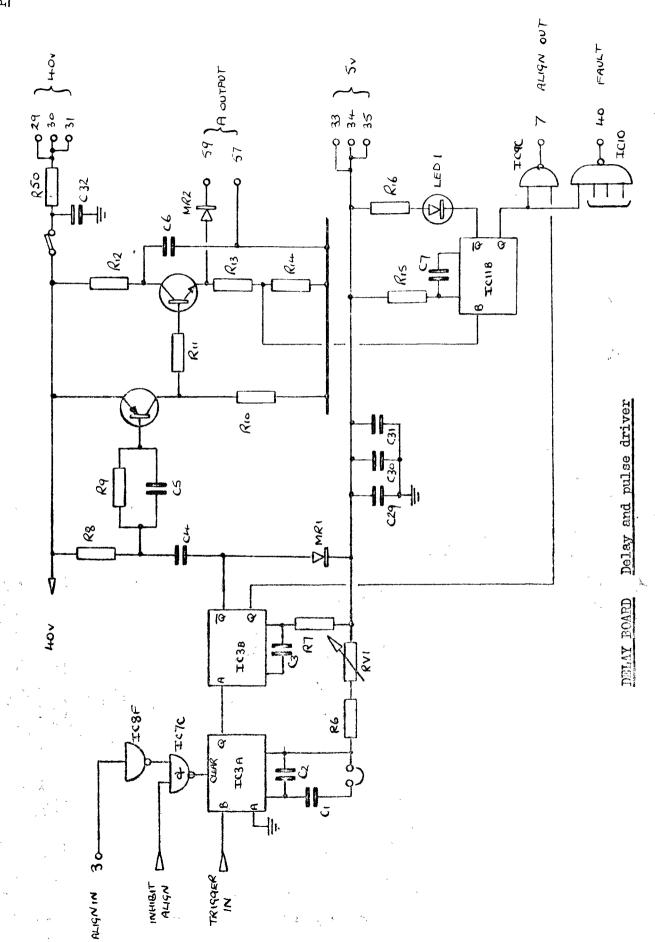

#### SECTION 4 - P.RT 4 - DILLAY BOARD

1. The delay boards are operated in tandem in the same way as the buffer boards. If both delays on paired boards are not set exactly the same it is possible to produce two output triggers on the same line. To prevent this double pulsing an align circuit is used to start the lagging trigger at the same time as the leading edge of the early trigger.

#### Input Gating

2. The input gating is identical to that used in the buffer board and is not described in detail here.

#### Delay Circuit (Considering trigger one circuit)

- 3. The positive edge of the input to IC3A B starts its timing cycle which period is set by C1, C2, R6 and RV1. When the timing cycle is completed the Q output of IC3A returns to logical O. This falling edge triggers IC3B which starts its timing cycle which is set to AuS by R7, C3.

- 4. The 4uS pulse at the 3 of IC3B is fed to the trigger drive amplifier and fault detector circuit identical to that used on the buffer boards.

#### Align Circuit

- 5. The 4uS pulse at IC3B Q is fed to IC9C. This pulse is allowed to pass through IC9C and leave the board only if the trigger is serviceable. If the trigger is not present them IC11B Q will be at logical O and the align pulse will be inhibited at IC9C.

- 6. When the align pulse arrives at board B, it is inverted by ICSF and is passed to IC7C. Providing the align is not inhibited the align pulse is fed to the clear input of IC3A. Consider the circuit action then the delay on board B is set longer than that of board A. The align pulse which starts at the leading edge of the trigger from board A clears IC3A on board B. IC3A Q goes low and initiates the trigger pulse from board B. The align facility is inhibited on one board of the pair when the second is turned off on time control panel.

- 6. The two fixed ranges of each delay are set by a prowince link adjacent to the timing capacitors Cl and C2.

- 7. The fault outputs from each delay are cormoned in IC10 and fed on the control board.

DELAY BOARD Layout

| Component index, Tr | rigger Driver | and dela                        | Y     |        |

|---------------------|---------------|---------------------------------|-------|--------|

| Circuit             | $\Lambda$     | В                               | C     | D      |

|                     | R6            | R17                             | R28   | R39    |

|                     | R7            | R18                             | R29   | R.O    |

|                     | R8            | R19                             | R30   | R41    |

|                     | R9            | R20                             | R31   | R.12   |

|                     | R10           | R21                             | R32   | R43    |

|                     | R11           | R22                             | R33   | R44    |

|                     | R12           | R23                             | R34   | R45    |

|                     | R13           | R24                             | R35   | R46    |

|                     | R14           | R25                             | R36   | R47    |

|                     | R15           | R26                             | R37   | R48    |

|                     | R16           | R27                             | R38   | R49    |

|                     |               |                                 |       |        |

|                     | RVl           | RV2                             | RV3   | RV4    |

|                     |               |                                 |       |        |

|                     | Cl            | C8                              | C15   | C22    |

|                     | C2            | C9                              | C16   | C23    |

|                     | 03            | C10                             | C17   | C24    |

|                     | <b>C</b> 4    | C11                             | C18   | C25    |

|                     | C5            | C12                             | C19   | C26    |

|                     | c6            | C13                             | C20   | C27    |

|                     | <b>C7</b>     | C14                             | C21   | C28    |

|                     |               |                                 |       |        |

|                     | MR1           | MR3                             | MR5   | MR7    |

|                     | MR2           | MR4                             | MR6   | LR8    |

|                     |               |                                 |       |        |

|                     | IC7c          | IC7b                            | IC73  | IC7d   |

|                     | IC3           | $\mathtt{IC}_{\sigma}^{\wedge}$ | 105   | IC6    |

|                     | IC8f          | IC8a                            | IC3b  | IC8e   |

|                     | IC9c          | 1C9b                            | 109a  | IC9d   |

|                     | ICllb         | IClla                           | IC12b | IC12a  |

|                     |               |                                 |       |        |

|                     | LED1          | LED2                            | LED3  | LIED.4 |

| •          |              |               |             |                   | SECTION 4          |

|------------|--------------|---------------|-------------|-------------------|--------------------|

| DELAY BOA  | RD - LIST    | OF COLPONENTS |             |                   | PART 4             |

| R1         | 1k5          | 10W 0136120   | Cl          | 0.0luF            |                    |

| <b>R</b> 2 | 1k5          |               | C2          |                   |                    |

| R3         | 1k5          |               | C3          | $680 \mathrm{pF}$ |                    |

| R4         | 1k5          |               | C4          | 4700pF            | 100 9548817        |

| R5         | 1k5          |               | C5          | 100pF             | 100 9 167456       |

| R6         | 4k7          | 10W 0124739   | ¢6          | 0.47uF            | 100v polycarbonate |

| R7         | 18k          | 10W 0136146   | C7          | 0.47uF            |                    |

| R3         | 1k5          |               | C29         | 0.22uF            | 100 1953299        |

| R9         | lk5          |               | C30         | 0.22uF            |                    |

| R10        | 1k5          |               | C31         | 0.22uF            |                    |

| Rll        | 680R         | 10W 0136112   | C32,        | 10uF              | 100v electrolytic  |

| R12        | 5k6          | 10W 0136134   |             |                   |                    |

| R13        | 220R         | 100 0136100   |             |                   |                    |

| R14        | 18R          |               | ICl         | SN7403            |                    |

| R15        | 3 <b>3</b> k | 107 0136152   | IC2         | SN7403            |                    |

| R16        | 270R         |               | IC3         | SN74123           |                    |

| R50        | 220R         | 10W 0136100   | IC4         | SN74123           |                    |

|            |              | •             | <b>I</b> C5 | SN74123           |                    |

| RVl        | 50k          | 107 9567027   | IC6         | SN74123           |                    |

|            |              |               | IC7         | SN7400            | 10AD 5204489       |

| VT1        | CV7676       | 10CV 0374448  | IC8         | SN7404            | 10CV 1181748       |

| VI2        | CV7725       | 10CV 0374572  | IC9         | 3N7400            | 10AD 5204489       |

| MR1        | CV7128       | 10CV 0373140  | ICL         | OSN7420           |                    |

| MR2        | CV7128       | 10CV 0373140  | ICL         | 1 SN74123         |                    |

|            |              |               | ICL         | 2 SN7;123         |                    |

| LED1/6     | TIL209       | .•            |             |                   |                    |

ANNIEX E TO

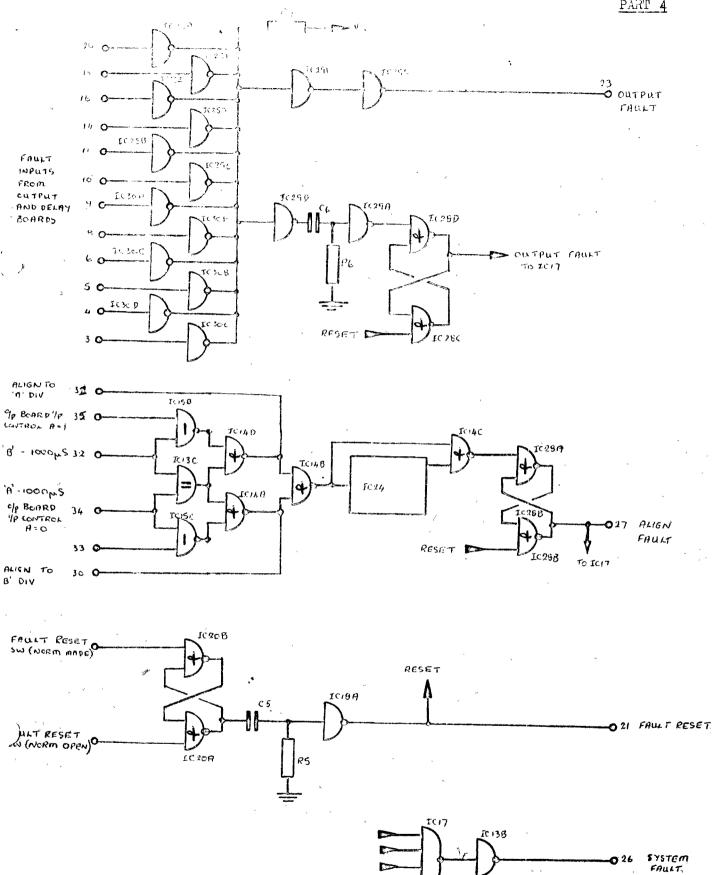

#### SECTION 4 - PART 5 - CONTROL BOARD

#### General Description

- 1. The Control board contains the logic required to decide which part of the trigger system is serviceable, and in the case of the dividers and oscillators ensures that the in use boards are serviceable. Should an output board not be serviceable, the control board will indicate this, but do nothing about it.

- 2. This board also contains the logic required to align the dividers, and the pulse generator required to reset its own fault latches and those of the dividers and oscillators.

- 3. The conditions set by the control board may be manually over-radden by the switches on the control panel.

#### Circuit Description

- 4. Oscillator Control The fault lines from Oscillators A and B are fad into the Board on pins 55 and 57 respectively to IC15a. These lines are at logical O for no fault and logical 1 for fault. When an oscillator fault occurs IC15a output goes to logical O and sets the fault latch formed by IC19a and b which in turn lights the oscillator fault LED and via IC17 the overall fault LED (and rings the bell).

- The fault input lines also feed IC5e and IC5f which invert the logic to give a logical O as a fault. The output of IC5e is fed to IC5c and the K input of IC3a. The K input of IC3a going to logical O ensures that then IC3a is clocked, its Q will go to logical O and its Q to logical 1 (this selects B oscillator as in use). The output of IC5c going to logical 1 causes the input to IC4c to go to a logical 1 for a time dependant upon C2 and R2. If ICic's other input is at logical 1 at this time (i.e. oscillator a in use) its output will go to logical O for about luS. This pulse is fed via IC4b to the clock input of IC3a which causes IC3a Q to go to logical 1 which selects B Oscillator as in use, as mentioned above. Should the B oscillator already have been in use then the A went faulty then IC4c will be inhibited (IC3a Q at logical 0) and the only effect will be to operate the fault latch. In the case where one oscillator is faulty and the other goes faulty, both the J and K inputs to IC3a will be at logical 0 when it is clocked and so no change-over will take place. The 2 outputs of IC3a are fed via open collector inverters and the control panel suitches to control the input gating on the divider boards. Open collector inverters are used in this position to allow the control lines to be grounded by a manual control switch on the control panel. The circuit action for the B oscillator going faulty is similar to that described above for the A side.

#### Divider control

6. The control circuit for the dividers is identical to that for the oscillators and the above description applies. The only exception is that the output has more drive capacity (three inverters in parallel) to allow it to feed a large number of output and delay boards. The pull up resistors are mounted on the control panel.

#### Alignment Control

7. If the standby divider is not in step with the In use divider, the -1000uS pulse from the in use divider is used to bring into alignment the standby divider. IC15b and c, IC13c and IC14a and d form the sating circuit which extracts the -1000uS pulse from the in use divider and feeds it as an align pulse to the standby divider should the two dividers not be in step. Should 2 consecutive align pulses occur, bistable IC28a and b is set by the second of these align pulses. The output of IC28b presents a fault signal to the overall fault detector IC17.

#### Fault Reset

8. The operation of SV3 is fed as a clean signal to pulse generator circuit C5, R5 via the de-bouncer IC2Oa and b. The exponential signal is transformed into a square wave by IC18a and fed as a 10u8 reset signal to the fault latches throughout the system.

#### Output Fault Circuit

9. Should a fault occur in any one of the output circuits, a logical 1 will be present at one of the inputs of IC25 or IC30. The logical 1 signal at the combined output of IC25 and IC30 is inverted twice by IC29 c and e and leaves the board to light the output fault LED. When a fault occurs the output fault latch IC28c and d will be set by the pulse from the pulse generator of R6 and IC29a. In order to avoid the masking of important faults by minor (output) faults, provision is made to allow the output fault latch to be reset even though the output fault still persists, however in this situation the output fault LED will remain lit when the overall fault LED is extinguished.

#### Overall Fault

10. The outputs from the individual fault latches are fed to IC17 where they are commoned to provide an overall fault signal. This is inverted by IC13b and fed from the board to light the overall fault LED.

#### ANNEX A TO SECTION 4 PART 5

# CONTROL BOARD FAULT LOGIC CTION

| Osc. or Div A | Osc. or Div B |                                          |

|---------------|---------------|------------------------------------------|

| រន្ធរ         | 151           | Select either for use.                   |

| Fault         | 151           | Select B for use and operate fault latch |

| រន្ធរ         | Fault         | Select A for use and operate fault latch |

| Fault         | Fault         | Operate fault latch                      |

### ALIGN

| ALIGN                                  |                  |                                                                |

|----------------------------------------|------------------|----------------------------------------------------------------|

| $\underline{\mathtt{Divider}\ \Delta}$ | <u>Divider B</u> |                                                                |

| In use                                 | aligned          | Do nothing                                                     |

| In use                                 | Mis-aligned      | Apply a pulse timed at -1000uS to the align input of Divider B |

|                                        |                  | input of bivider b                                             |

| Aligned                                | In use           | Do nothing                                                     |

| Mis-aligned                            | In use           | Apply a pulse time at -1000uS to the align                     |

| _                                      |                  | input of Divider A                                             |

|                                        |                  | the second of the second of the                                |

More than one successive pulse applied Operate alignment fault latch and light to either align input. the fault LED

Output fault

Operate overall fault latch with pulse and light output fault LED.

```

SECTION 4 - PART 6 - RACK IRING INTERCONNECTIONS

Osc Osc Cont Cont Div Div O/P O/P Del Del

Signal Description

В

Bd Pan.

Δ

\mathbf{B}

В

\mathbf{B}

40a

3z

Delag B fault

40a

4z

Delay A fault

Catout B fault

5z

59a

62

59a

Output A fault

8z

9z

Spare fault input

10z

11z

lines to Control Board

14z

16z

Grounded when not used

18z

20±

56z 56z 21a

52

Fault latch reset pulse

22z

" Switch (Norm made)

а

23a

Z

O/P foult Led. drive

24a

Z

Oscillator foult LED drive

26a

Z

Overall fault LED drive

27a

Z

Alignment fault LED drive

28a

Z

Divider fault LED drive

29z

a

Fault reset switch (Norm. broken)

30a

21z

Divider B align pulse

31a

21z

Divider A align pulse

32z

23a

Divider B -1000uS pulse

33z

55z 52z 52z 13z 13z

Buffer i/p control (Sw'd) A=0

Divi er A -1000uS pulse

Buffer i/p control (Sy'd) A=1

Buffer i/p control (Unsw) A=1

34z

23a

35z

а

552

55z 53z 14z 14z

40a

Z

4la

Z

Buffer i/p control (Unsw) A=0

Divider i/p control (Unsw) A=1

Divider i/p control (Unsw) A=0

43a

\mathbf{z}

44a

Z

46z

13a

Divider A fault

48z

13a

Divider B fault

50z

Divider Manual 1

a

5lz

Divider Manual B

58a

55z

Oscillator i fault

56z

Oscillator Manual A

58a 57z

Oscillator B fault

58z

Oscillator Manual B

3

Divider i/p control (Sw'd) A=0

Divider i/p control (Sw'd) A=1

54z

34z 3.;z

54z

41z 41z

a

250KHz - Oscillator B

57a

32z 32z

57a

39z 38z

250KHz - Oscillator A

29a

-750uS - A

29a

-750uS - B

25a

-250uS - i

25a

-250uS - B

-125uS - 🕹

3a

Inverted pulse o/p's

За

-125uS - B

lla

-8uS - 🔝

at TTL logic level.

lla

-8uS - B

To be wired as req'd.

9a

Ous - 1

9a

) to O/P & delay boards

OuS - B

27a

z

Scope trigger (-1000uS)

z

27a

Scope trigger (-1000uS)

38

a

Inhibit align A delay

38

а

Inhibit align B delay

```

```

Rack Wiring Interconnections (Continued)

Osc Osc Cont Cont Div Div O/P O/P Del Del

Bd.

Pan.

جک

\mathbb{B}

\mathbb{B}

Ĺ,

\mathbf{B}

Signal Description

Δ

500Hz (to RLL)

49a

z

500Hz (to Rim)

49a

z

TTL 500Hz - parallel source

48z 48z

15a 15a

Delay output ligh for trigger No

5a

lz

2z

Delay output align for trigger No ?

6а,

Delay output align for trigger Mc

3z

7a

.z 8a

Delay output align for trigger No .

Delay output align for trigger No -

5a 1z

6a 2z

Delay output align for trigger No

Delay output ligh for trigger No I

7a

3z

Delay output align for trigger No ..

8a

.12

9z 9z

B input No 3

B input No 2 ) Tire as required to

10z 10z

B input No 1 ) the Divider inverted

llz llz

) pulse outputs.

A input No 1

15z 15z

16z 16z

1 input No 2

A input No 3 )

13z 18z

Selected output No 1

12a

Tire as

12a

Selected output No 1 )

Selected output No 2 ) required to

17a

Selected output No 2 ) input pins

Selected output No 3 ) 21-24 on the

Selected output No 3 ) same board.

17a

19a

19a

TTL input for A Delay output No 1

21z

TTL input for Delay B output No 1

21z

22z

TTL input for Delay A output No 2

TTL input for Delay B output No 2

22z

TTL input for Delay 1 output No 3

23z

TTL input for Delay B output No 3

23z

TTL input for Delay 1 output No 4

24z

TTL input for Delay B output No 4

24z

B input No 1 ) ire as required to

48z 48z

B input No 2 )the Divider

49z 45z

B input No 3 )inverted pulse

A input No 3 )outputs.

A input No 2 )

50z 50z

54z 54z

A input No 2

55z 55z

4 input No 1 )

57z 57z

Selected output No 1 ) Tire as

51a

Selected output No 1 ) required to

51a

Selected output No 2 ) input ping

Selected output No 2 ) 1-46 on

Selected output No 3 ) the same

56a

56a

58a

Selected output No 3 ) board.

58a

TTL input for O/P A output No 4

41z

TTL input for O/P B output No 4

41z

TTL input for O/P A output No 5

42z

TTL input for O/P B output No 5

42z

PTL input for O/P 1 output No 6

43z

TTL input for O/P B output No 6

43z

TTL input for O/P A output No 3

442

TTL input for O/P B output No 3

44z

45z

TTL input for O/P .. output No 2

TTL input for O/P B output No 2

45z

46z

TTL input for O/P A output No 1

```

.46z

TTL input for O/P B output No 1

| Rack                             | Wirir                       | g Int | terco       | nnect:       | ions (       | Conti                                                              | nued)                                                              |                            |                                   |                                |                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------|-----------------------------|-------|-------------|--------------|--------------|--------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------|-----------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0sc<br>A                         | Osc<br>B                    |       | Cont<br>Pan | Div<br>A     | Div<br>B     | 0/P<br>Λ                                                           | 0/P I<br>B                                                         | Del<br>A                   | Del<br>B                          | Power<br>Rail                  |                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 50-2<br>42-4<br>8<br>1<br>2<br>3 | 50-2<br>42-4<br>8<br>1<br>2 |       |             |              |              |                                                                    |                                                                    |                            |                                   | +5volts<br>+40volts<br>+5volts | (screened) 500Hz (Sw'd) Ref. phase. 500Hz (Sw'd) Ref. phase. 500Hz Ref. phase return 500Hz Variable phase (Sw'd) 500Hz Variable phase (Sw'd)                                                                                                                                                                                                                                                                                                 |

| 4<br>( ;                         | 4                           | 59/   | 60          | 59/60<br>1/2 | 59/60<br>1/2 | )                                                                  |                                                                    |                            |                                   | +5volts Ground +5volts         | JUUNZ VALTABLE MASSE TEVAL                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                  |                             | 1/    | 2           |              |              |                                                                    | 2-4<br>3 36 <b>-</b> 8                                             |                            |                                   | Ground +5volts                 | +40volts (Switched)<br>+40volts (Switched)                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                  |                             |       |             |              |              | 1/2                                                                | 2 1/2                                                              | 29-3<br>37-8               | 29 <b>-</b> 3:<br>3 37 <b>-</b> 8 | +5volts                        | +40volts (Switched)<br>+40volts (Switched)                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                  |                             |       |             |              |              | 7<br>9<br>12<br>14<br>17<br>19<br>22<br>24<br>27<br>29<br>32<br>34 | 7<br>9<br>12<br>14<br>17<br>19<br>22<br>24<br>27<br>29<br>32<br>34 | 59<br>57<br>55             | 59<br>57<br>55                    | Ground                         | Fixed trigger output No? Screen for above Fixed trigger output No? Screen for above Fixed Trigger output No. Screen for above Delayed trigger output No. |

| (                                |                             |       |             |              |              |                                                                    |                                                                    | 53<br>51<br>49<br>47<br>45 | 53<br>51<br>49<br>47<br>45        |                                | Screen for above Delayed trigger output No 3 Screen for above Delayed trigger output No 4 Screen for above                                                                                                                                                                                                                                                                                                                                   |