As you are now the owner of this document which should have come to you for free, please consider making a donation of £1 or more for the upkeep of the (Radar) website which holds this document. I give my time for free, but it costs me around £300 a year to bring this document to you. You can donate here <a href="https://blunham.com/Radar">https://blunham.com/Radar</a>, thank you.

Do not upload this copyright pdf document to any other website. Breaching copyright may result in a criminal conviction and large payment for Royalties.

This document was generated by me, Colin Hinson, from a document held at R.A.F. Henlow Signals Museum which is believed to be out of copyright or Crown Copyright. It is presented here (for free) under the Open Government Licence (O.G.L.) if under Crown Copyright and this version of the document is my copyright (along with the Crown Copyright) in much the same way as a photograph would be. It should be noted that most of the pages are identifiable as having been processed by me. If you believe the original document to be under copyright, please contact me.

The document should have been downloaded from my website <a href="https://blunham.com/Radar">https://blunham.com/Radar</a>, or any mirror site named on that site. If you downloaded it from elsewhere, please let me know (particularly if you were charged for it). You can contact me via my Genuki email page: <a href="https://www.genuki.org.uk/big/eng/YKS/various?recipient=colin">https://www.genuki.org.uk/big/eng/YKS/various?recipient=colin</a>

You may not copy the file for onward transmission of the data nor attempt to make monetary gain by the use of these files. If you want someone else to have a copy of the file, point them at the website (<a href="https://blunham.com/Radar">https://blunham.com/Radar</a>). Please do not point them at the file itself as it may move or the site may be updated.

\_\_\_\_\_

I put a lot of time into producing these files which is why you are met with this page when you open the file.

In order to generate this file, I need to scan the pages, split the double pages and remove any edge marks such as punch holes, clean up the pages, set the relevant pages to be all the same size and alignment. I then run Omnipage (OCR) to generate the searchable text and then generate the pdf file.

Hopefully after all that, I end up with a presentable file. If you find missing pages, pages in the wrong order, anything else wrong with the file or simply want to make a comment, please drop me a line (see above).

If you find the file(s) of use to you, you might like to make a donation for the upkeep of the website – see <a href="https://blunham.com/Radar">https://blunham.com/Radar</a> for a link to do so.

Colin Hinson

In the village of Blunham, Bedfordshire, UK.

March 1979

10 JUL 1979

# UK/FRR 626 HF RECEIVER (Racal Type RA. 1778/DA78120/B)

# GENERAL AND TECHNICAL INFORMATION ALSO REPAIR AND RECONDITIONING INSTRUCTIONS

BY COMMAND OF THE DEFENCE COUNCIL

Ministry of Defence

Sponsored for use in the

ROYAL AIR FORCE by D. Sigs (Air)

Prepared by Racal Communications Systems Ltd., Bracknell, Berks.

Publications authority: ATP/MOD (PE)

Service users should send their comments through the channel prescribed for the purpose in:

AP 100B-01 Order 0504

#### MODIFICATION RECORD

The following record confirms that this publication incorporates all technical changes necessitated by the modifications listed below. Information on modification titles, classification categories and Mark applicabilities is given in Topic 2.

| Mod No.      | Brief Description                                                     |

|--------------|-----------------------------------------------------------------------|

| A8556        | Decrease length of 'read' pulse.                                      |

| A8529        | Introduction of alternative IF/AF board.                              |

| A8778        | Introduction of 100 $k\Omega$ resistors on PM370 board.               |

| A9006        | Add ferrite bead to PM336 board.                                      |

| A9007        | To change diodes D13, D14 on PM674 board.                             |

| A9662        | To prevent amplifier oscillation on PM335 board.                      |

| A9722        | To reduce spurious signals on PM336 board.                            |

| B0077        | Reposition the mains fuse.                                            |

| B0190        | Replacement of nickel-cadmium battery.                                |

| B0190 Alt 1. | Replacement of nickel-cadmium battery.                                |

| B0529        | Addition of 1 $k\Omega$ resistors to transistors 1TR1, 1TR2 and 1TR3. |

| TC0024       | Replacement of unobtainable capacitors.                               |

# Maintenance manual (Part 1)

RA. 1778/DA78120/B HF Communications Receiver (Chapters 1 to 16)

# CONTENTS

## PART 1

|             | TECHNICAL SPECIFICATION          |

|-------------|----------------------------------|

| CHAPTER 1   | PRINCIPLES OF OPERATION          |

| CHAPTER 2   | LOW FREQUENCY LOOP BOARD PM588   |

| CHAPTER 3   | UPPER LOOP BOARD PM589           |

| CHAPTER 4   | TRANSFER LOOP BOARD PS.338       |

| CHAPTER 5   | HIGH FREQUENCY LOOP BOARD PS.337 |

| CHAPTER 6   | 34 MHz GENERATOR BOARD PM339     |

| CHAPTER 7   | FREQUENCY STANDARD ASSEMBLY      |

| CHAPTER 8   | RF UNIT                          |

| CHAPTER 9   | FIRST MIXER BOARD PM335          |

| CHAPTER 10  | SECOND MIXER BOARD PM336         |

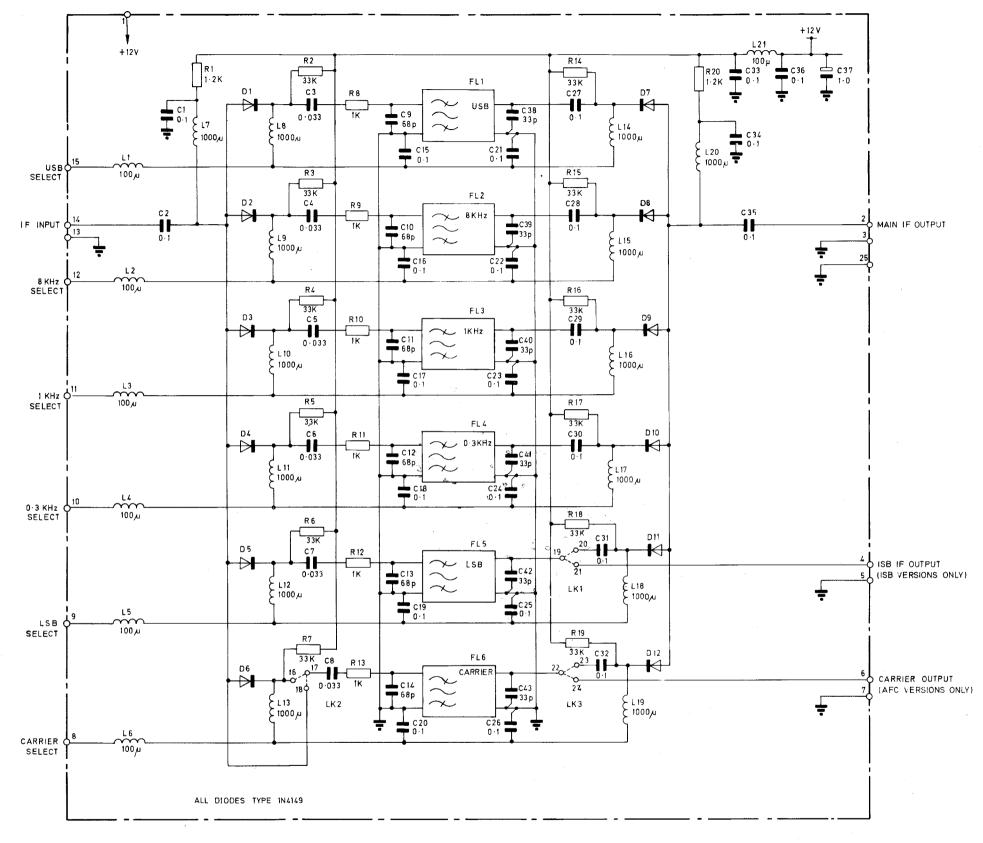

| CHAPTER 11  | IF FILTER BOARD PS.367           |

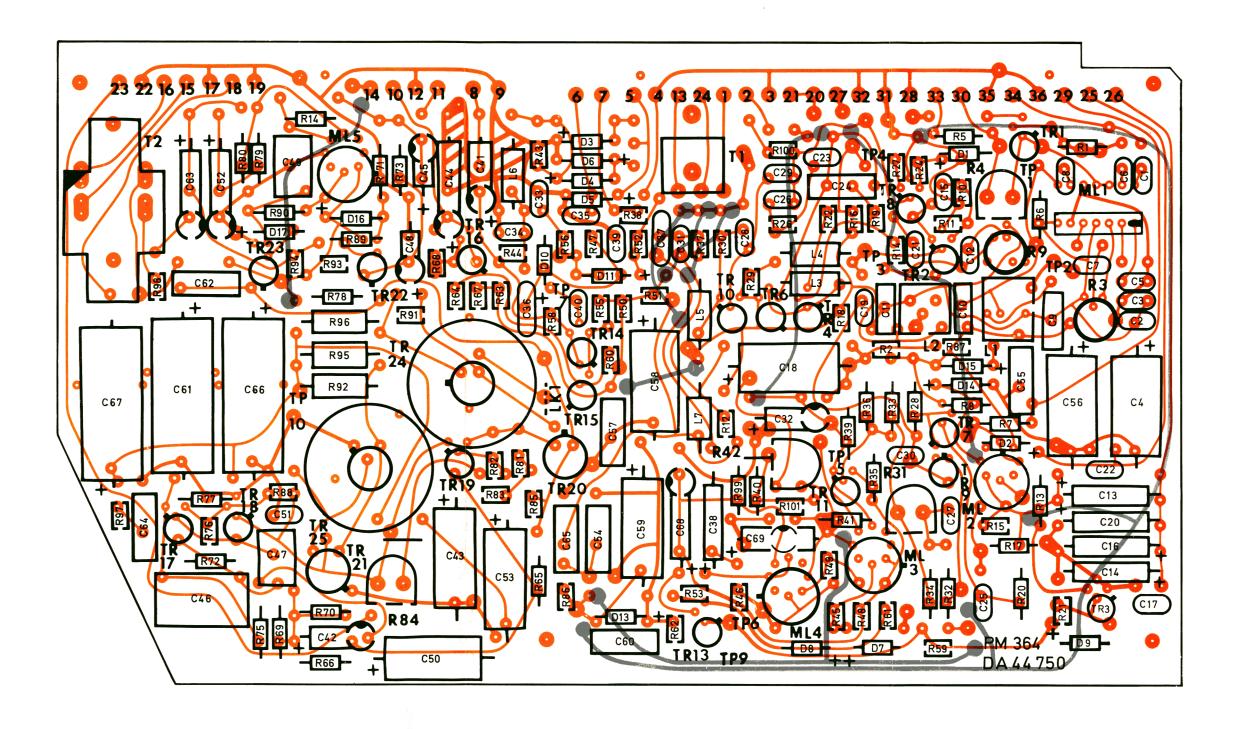

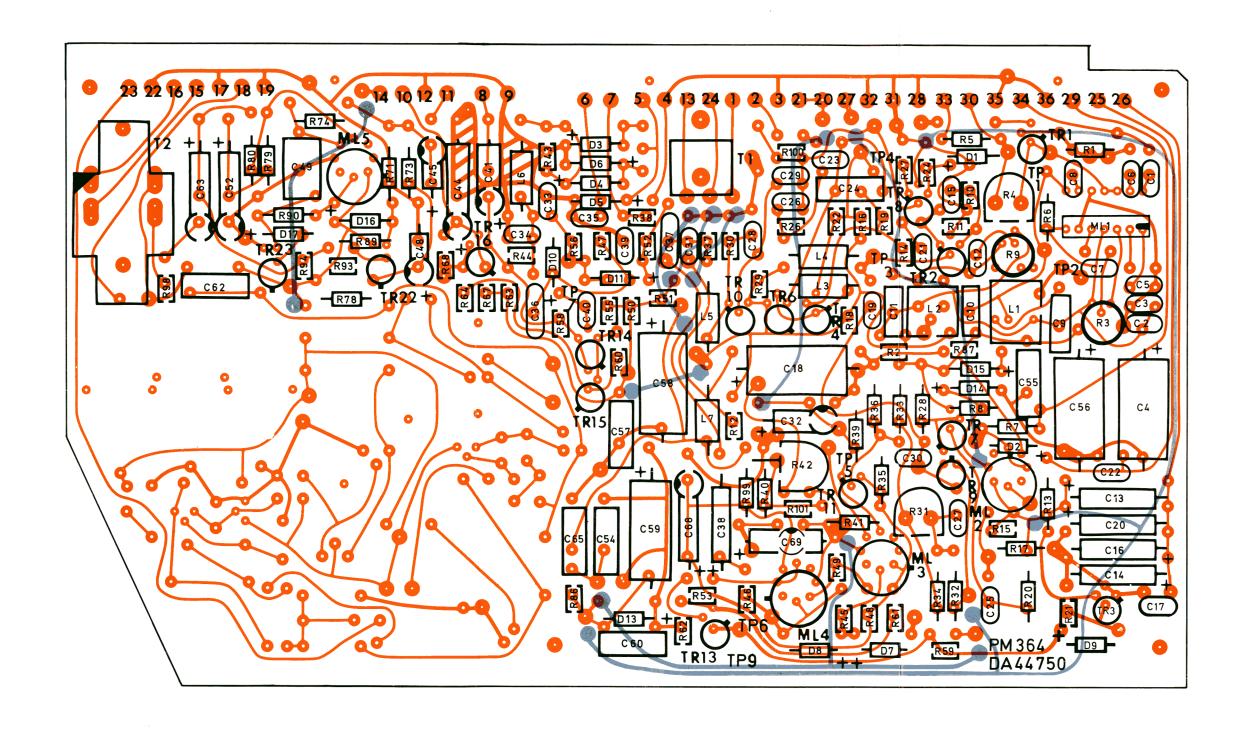

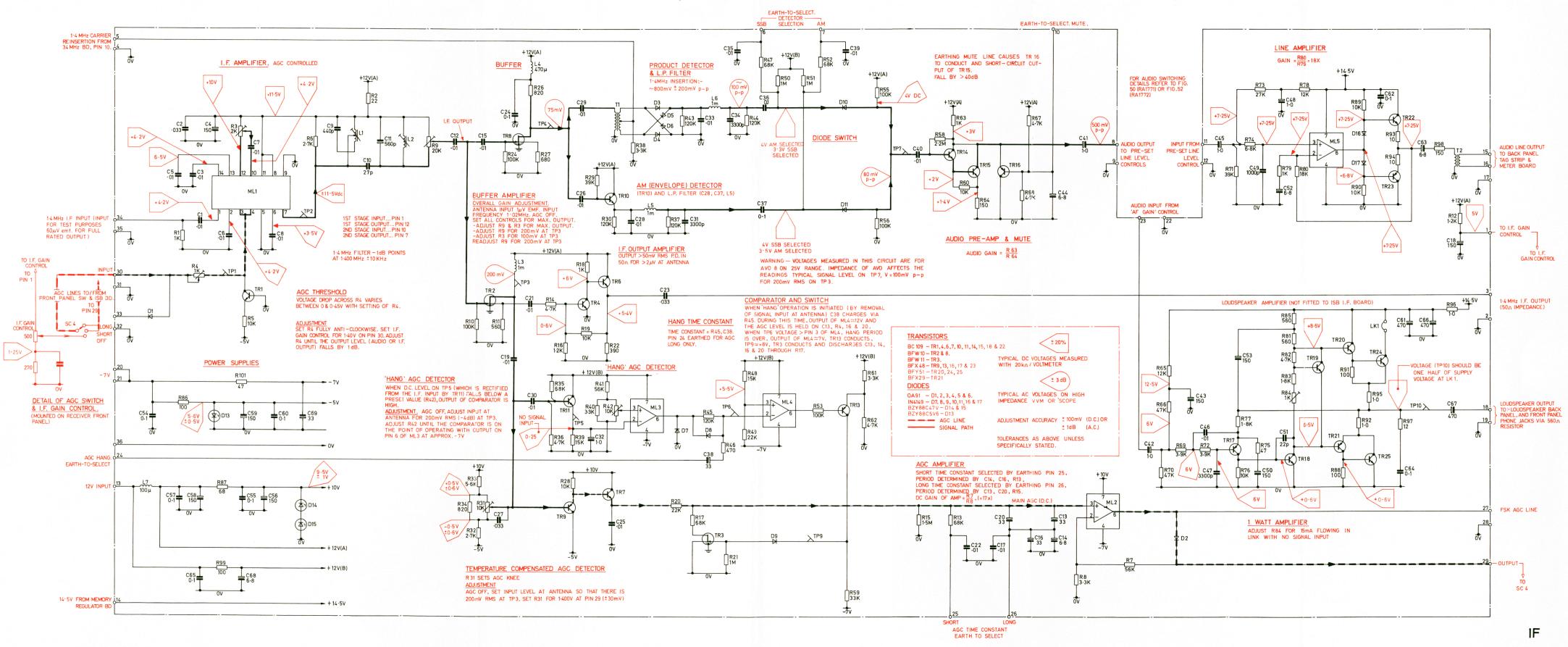

| CHAPTER 12  | IF/AF BOARD PM364                |

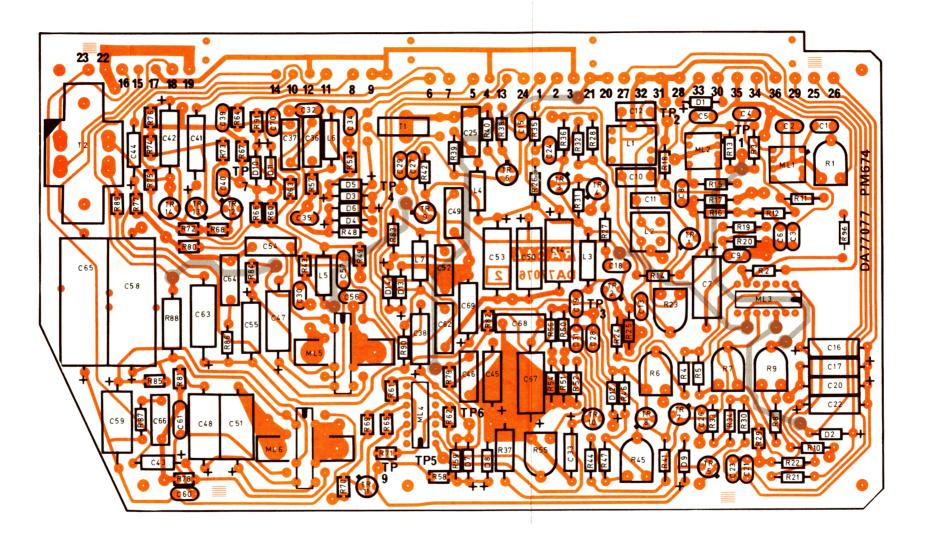

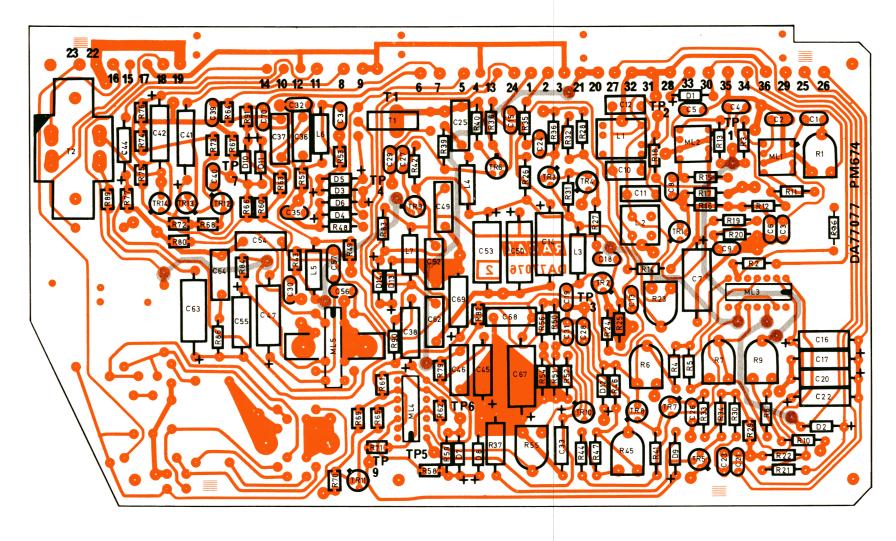

| CHAPTER 12A | IF/AF BOARD PM674                |

| CHAPTER 13  | SHAFT ENCODER                    |

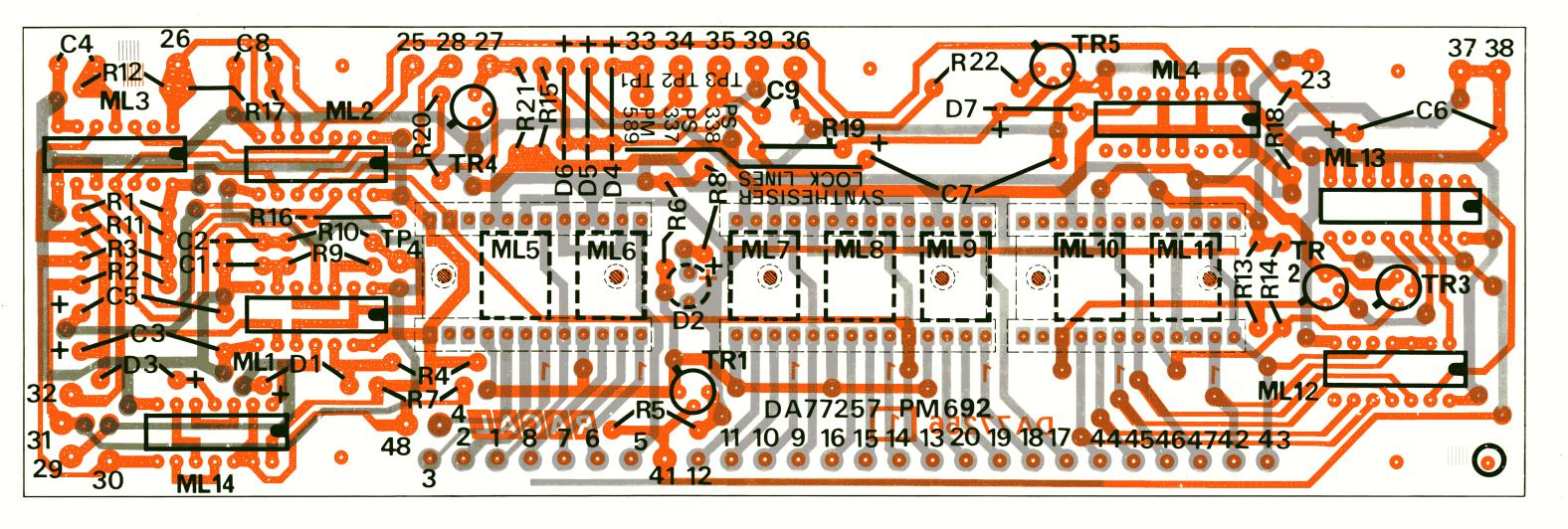

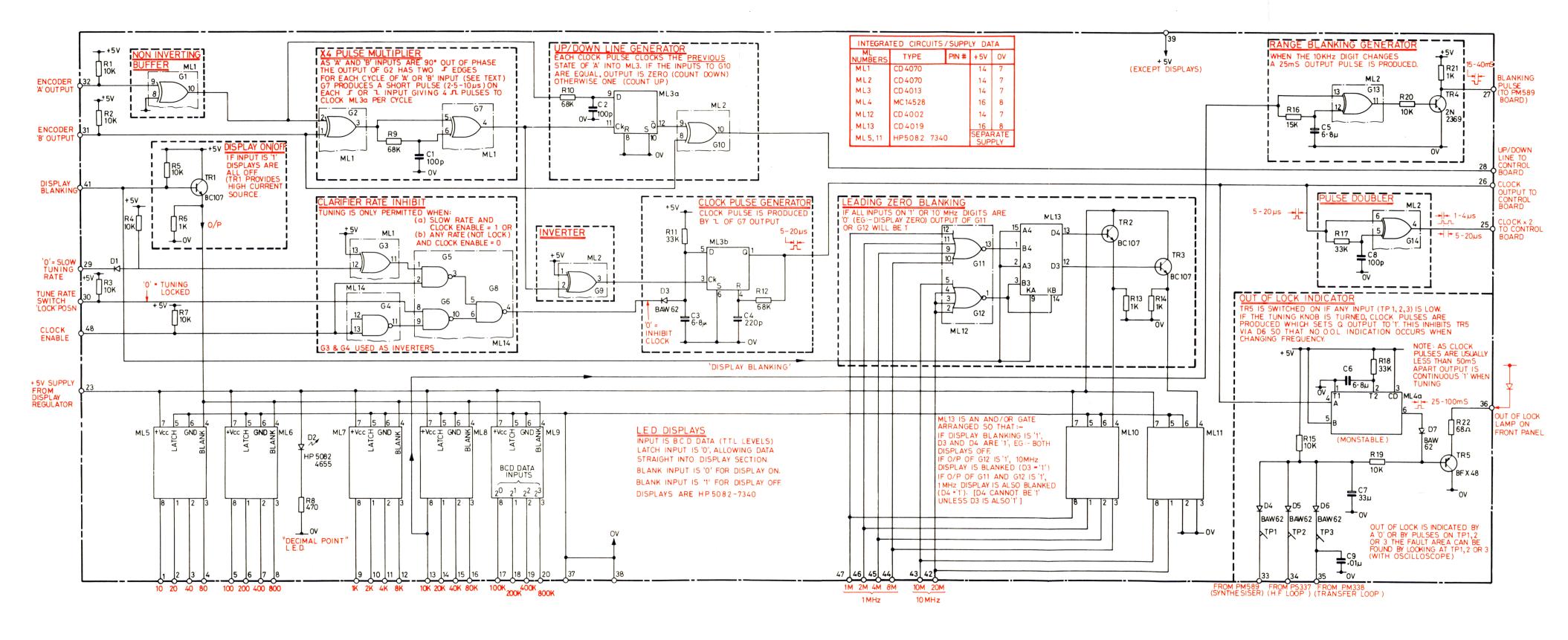

| CHAPTER 14  | DISPLAY BOARD PM692              |

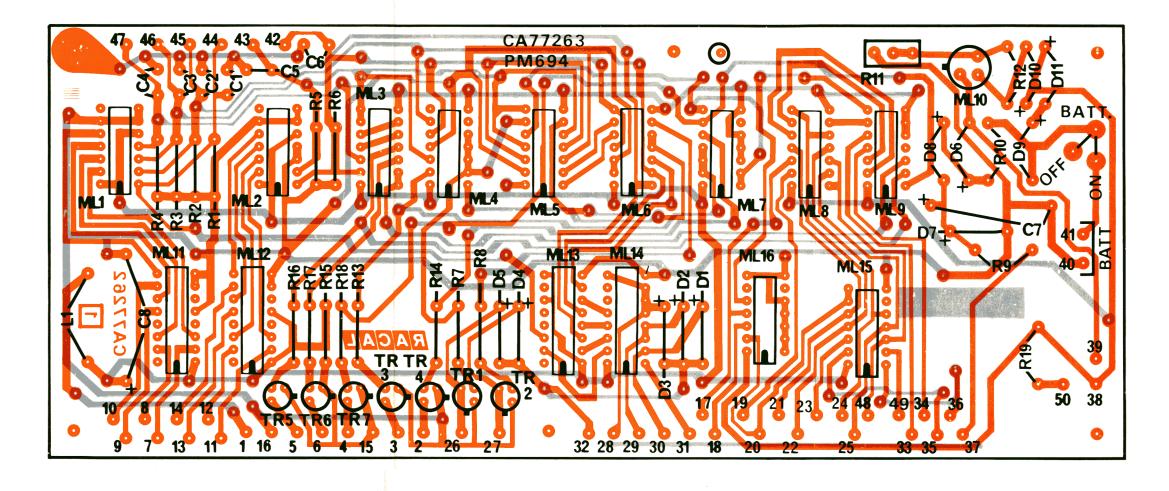

| CHAPTER 15  | DECODER BOARD PM694              |

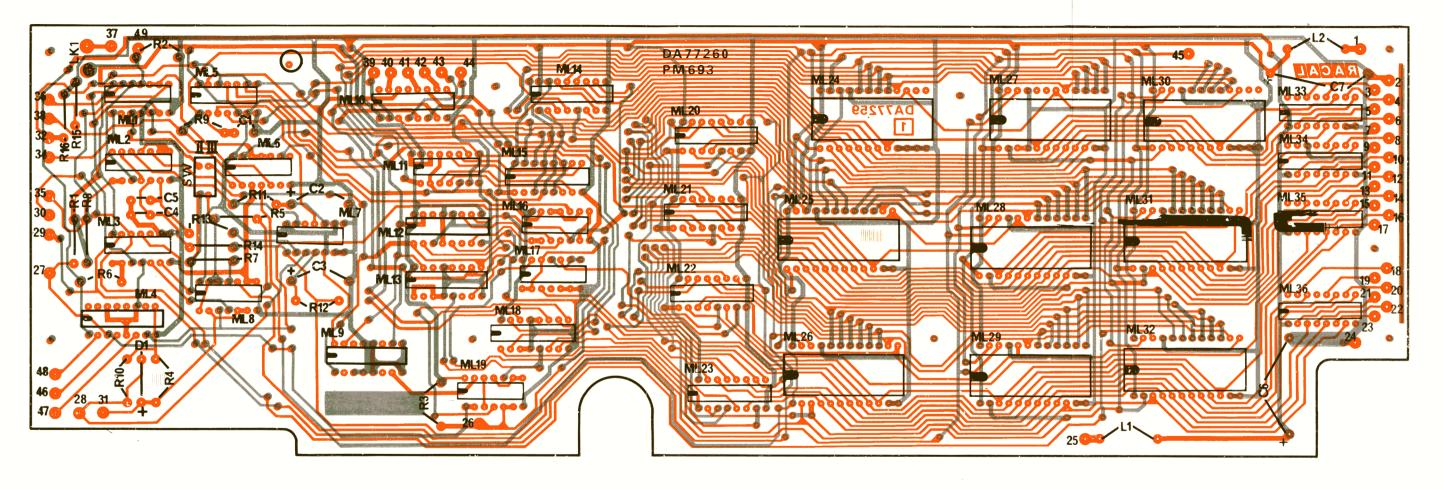

| CHAPTER 16  | MEMORY BOARD PM693               |

|             |                                  |

# PART 2

| CHAPTER 17 | AFC BOARD PM664                                             |

|------------|-------------------------------------------------------------|

| CHAPTER 18 | FSK DEMODULATOR BOARD PM368                                 |

| CHAPTER 19 | POWER SUPPLIES (INCLUDING BOARD PM370 AND PS427/1)          |

| CHAPTER 20 | INTERCONNECTIONS AND CHASSIS LAYOUT (INCLUDING BOARD PM419) |

| CHAPTER 21 | DISMANTLING AND RE-ASSEMBLY                                 |

| CHAPTER 22 | FUNCTIONAL TEST PROCEDURES                                  |

| CHAPTER 23 | ALIGNMENT PROCEDURES                                        |

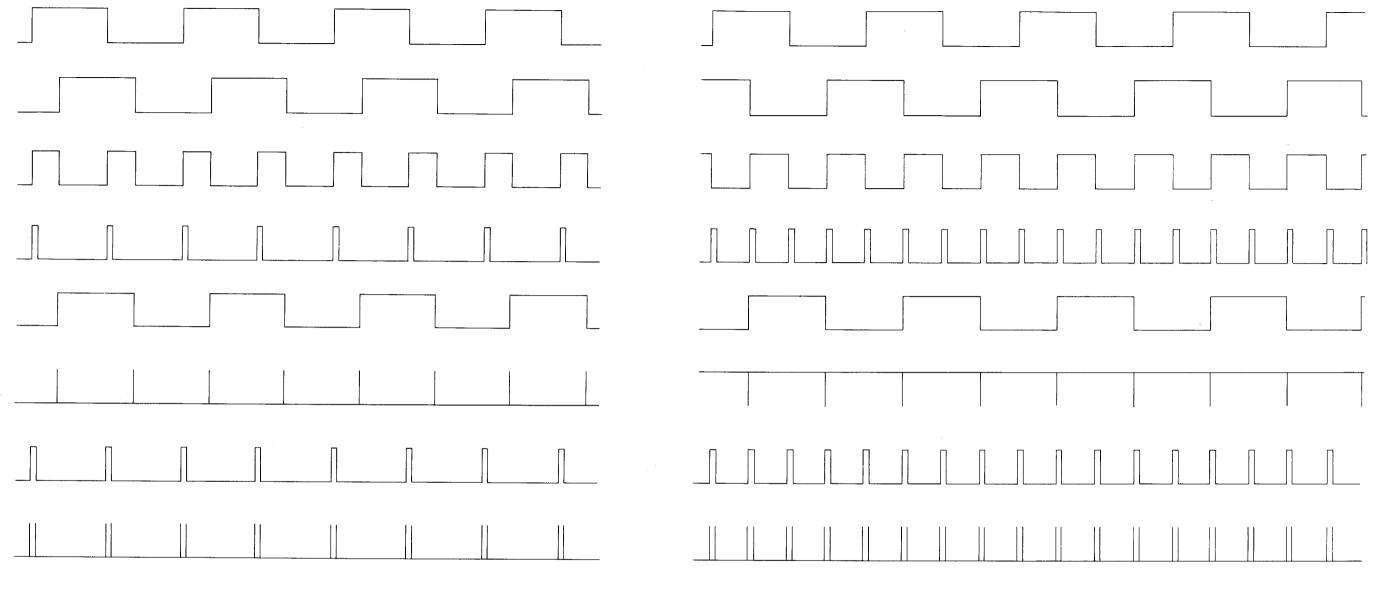

CHAPTER 24 FAULT DIAGNOSIS AND OSCILLOGRAMS

CHAPTER 25 LIST OF COMPONENTS

SUPPLEMENT 1 INTRODUCTION TO TTL LOGIC

SUPPLEMENT 2 INTRODUCTION TO CMOS LOGIC

SUPPLEMENT 3 ALTERNATIVE LOGIC SYMBOLS

SUPPLEMENT 4 INTRODUCTION TO OPERATIONAL AMPLIFIERS

SUPPLEMENT 5 REPAIR TECHNIQUES

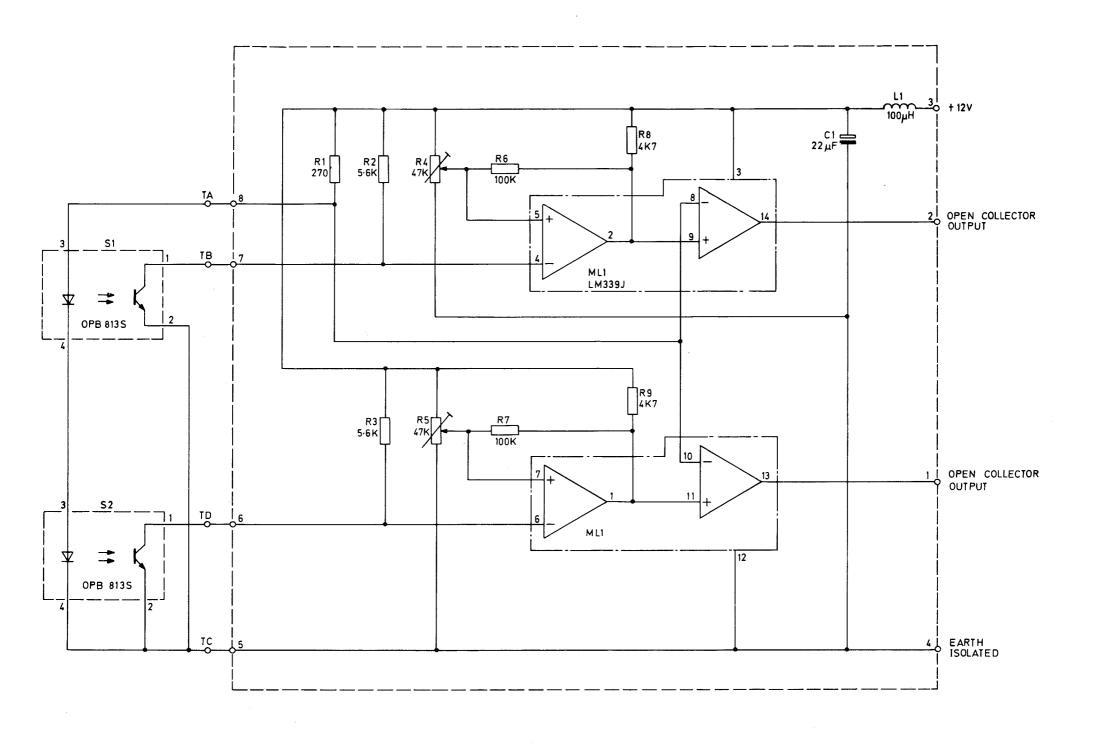

APPENDIX 1 AUDIO SWITCHING UNIT MM.532

APPENDIX 2 SOLID STATE FSK RELAY ATR-24

APPENDIX 3 NOT APPLICABLE

APPENDIX 4 IF CONVERTER MODULE MS561

#### TECHNICAL SPECIFICATION

The performance as stated in this specification is applicable to the wideband condition. If the RF tuning unit is in use an additional 20dB of protection is given at  $\frac{1}{2}$  12 $\frac{1}{2}$ % off-tune.

Frequency Range:

15kHz - 30MHz

Modes of Reception:

A1, A2, A2H, A2J, A3, A3A, A3J, A3H with the following options:

- (1) Choice of USB or LSB

- (2) Provision for reception of A3B or F1

- (3) Provision of AFC

Tuning:

- (1) 12 Programmable Channels

- (2) Continuously tunable synthesizer in 10Hz, 20Hz or 1kHz increments over the full frequency range. Seven digit electronic readout.

Tuning Accuracy:

<sup>±</sup> 5Hz relative to the frequency of the wanted signal.

Frequency Stability:

- (1) The following optional alternative frequency standards may be fitted:

- (a) Temperature Controlled Crystal Oscillator (TCXO)

- (i) Temperature: Better than  $\frac{1}{2}$  1.5 in  $10^6$   $-10^{\circ}$ C to  $+55^{\circ}$ C.

- (ii) Long Term:  $\frac{+}{2}$  in  $10^7$  over a 30 day period.

- (b) Frequency Standard Type 9400

- (i) Temperature:  $\frac{1}{2}$  1 in  $10^8$ /°C.

- (ii) Long Term:  $\frac{1}{2}$  1.5in  $10^7$  over a 30 day period or  $\frac{1}{2}$ 5 in  $10^7$  per day.

- (c) Frequency Standard Type 9420

- (i) Temperature:  $\frac{1}{2}$  6 in  $10^{10}$ / °C.

- (ii) Long Term:  $\pm 1.5$ in  $10^8$  over a 30 day period or  $\pm 5$  in  $10^{10}$  per day.

- (2) Provision is made for the use of an external frequency standard.

#### Antenna Input:

- (1) Wideband. 50 ohms to 75 ohms nominal. BNC coaxial connector.

- (2) RF tuning is available within the receiver. This is provided by five automatically selected bandpass filters covering the frequency range 1MHz to 30MHz. Manual RF peak tuning is provided over each pre-selected band of frequencies. Each tuned range provides a nominal attenuation of 20dB at  $12\frac{1}{2}\%$  off-tune. A low pass filter is used below 1MHz.

- (3) Receiver muting is provided to protect the receiver from local emissions on the tuned frequency. The operation of the muting circuits permits 'break in' or 'listen through' operation when keying at a rate of up to 20 bauds.

- (4) The receiver will withstand without damage RF input signals of 30V (e.m.f.) continuously. A fuse and spark gap is provided for protection against higher voltages.

- (5) Re-radiation with the antenna input terminated in 50 ohms is less than  $10\mu V$ .

Sensitivity:

(1) CW and SSB (A1, A2H, A3A, A3H, A3J)

In a 3kHz bandwidth the signal-to-noise ratio is better than:

500kHz-30MHz , 15dB with 1  $\mu V$  (e.m.f.) input. 50kHz-500kHz , 15dB with 3  $\mu V$  (e.m.f.) input. 15kHz-50kHz , 15dB with 10  $\mu V$  (e.m.f.) input.

(2) <u>DSB (A2, A3)</u>

In a 3kHz bandwidth the signal-to-noise ratio is better than:

500kHz-30MHz, 15dB with  $1.5\,\mu V$  (e.m.f.) input 70% modulated.

50kHz--500kHz , 15dB with  $5~\mu\text{V}$  (e.m.f.) input 70% modulated.

15kHz-50kHz, 15dB with  $15\,\mu V$  (e.m.f.) input 70% modulated.

IF Selectivity:

#### (1) SSB (A3A, A3J) and ISB (A3B)

Passband at -6dB: 250Hz to 3000Hz.

Passband at -60dB: 400Hz and +4100 Hz.

or alternatively

Passband at -6dB: 150Hz to 6000Hz.

Passband at -60db: -300Hz and +8000Hz.

# (2) CW/MCW/AM/FSK (A1, A2, A3, A2H, A3H, F1)

Standard Receivers. In addition to the mode-selected SSB or ISB filters, up to four optional IF filters may be fitted although certain combinations of facilities will permit only three filters to be fitted. IF filters of the following nominal passbands are available:

0.3kHz, 1kHz, 3kHz, 6kHz, 8kHz, 13kHz.

Alternative filters can be supplied to special order.

Cross Modulation:

With a wanted signal greater than 300  $\mu$ V e.m.f., in a 3kHz bandwidth, an unwanted signal, 30% modulated, removed not less than 20kHz, will be greater than 300mV e.m.f., to produce an output 20dB below the output produced by the wanted signal.

Reciprocal Mixing:

With a wanted signal of less than  $100\,\mu\text{V}$  e.m.f., in a 3kHz bandwidth, an unwanted signal more than 20kHz removed will be greater than 70dB above the wanted signal level to give a noise level 20dB below the output produced by the wanted signal.

Blocking:

With a wanted signal of 1mV e.m.f., an unwanted signal more than 20kHz removed must be greater than 500mV to reduce the output by 3dB.

Intermodulation Products:

#### (1) Out of Band

With two 30mV e.m.f. signals separated and removed from the wanted signal by not less than 20kHz the third order intermodulation products are not less than -85dB below either of the interfering signals and typically better than -90dB.

#### (2) In Band

Two in band signals of 30mV e.m.f. will produce third-order intermodulation products of not greater than -40dB.

Spurious Responses:

(1) External

External signals, 20kHz removed from the wanted signal, must be at least 80dB above the level of the wanted signal to produce an equivalent output.

(2) Internal

The specified sensitivity figures in the CW/SSB modes are not reduced by more than 3dB as a result of any internally generated spurious signals.

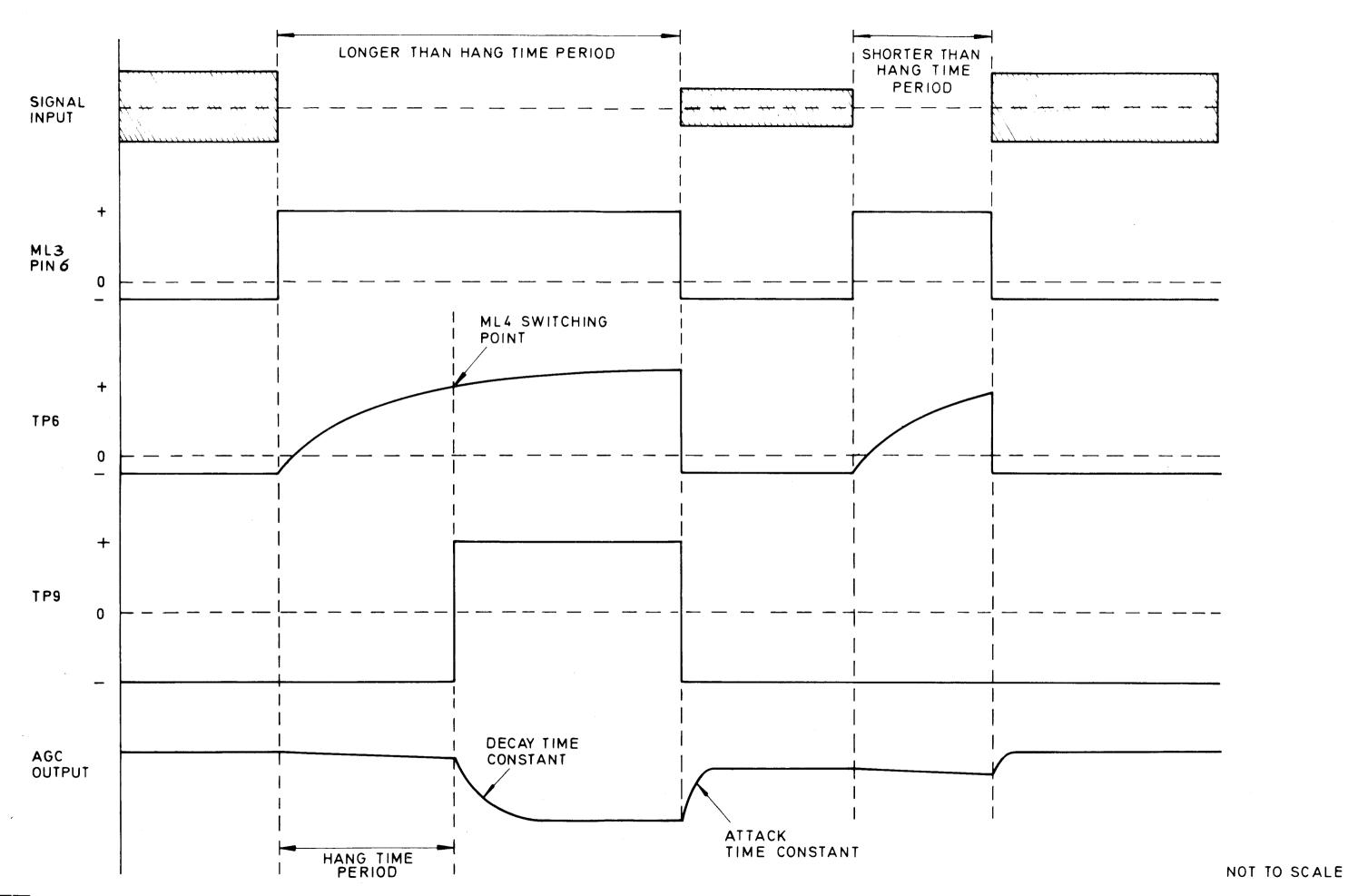

AGC:

(1) Range

An increase in input of 100dB above 2  $\mu V$  e.m.f. will produce an output change of less than 6dB.

(2) Switched selection of AGC 'off', 'short' and 'long' time constants is provided.

AFC (A3A, A3B):

- (1) AFC is available as an optional internal facility and is provided with a front panel switch for switching AFC in or out of operation.

- (2) Capture range: ± 50Hz.

Follow range: ± 500Hz or beyond.

Residual Error: 2Hz max.

Memory:

In the event of carrier failure, or worsening of the carrier to noise/modulation level of 10dB, no re-tuning is necessary.

BFO Range:

± 3kHz variable by a slow motion control.

IF Output (AGC On):

1.4MHz, nominally 100mV (e.m.f.) into 50 ohms.

·Audio Characteristics:

(1) Output Levels:

- (a) Line outputs, 1mW nominal into 600 ohms balanced, adjustable by preset level control on front panel to +6dBm.

- (b) Phone outputs unbalanced, 10mW nominal into 600 ohms.

- (c) 50mW into an internal loudspeaker which is capable of being switched in or out of operation.

- (d) Connection for external speaker 1 watt into 8 ohms.

- (e) Two 3 mW,  $600\Omega$  outputs.

#### (2) AF Response:

- (a) Line outputs. Within IdB from 100Hz to 6000Hz relative to the level of a standard 1000Hz tone.

- (b) The overall AF response will be dependent upon the IF bandwidth selected.

#### (3) AF Distortion:

- (a) Line outputs. Not greater than 2% at specified output of 1mW nominal.

- (b) Loudspeaker outputs. Not greater than 5% at 50mW output to internal loudspeaker, and 1W output to external speaker.

- (c) Phone output. Not greater than 5% at specified output of 10mW nominal.

Cross Talk (A3B):

With a wanted signal at a level of 1 mV and the AF output adjusted to 1mW, the cross talk from an equal signal in the opposite sideband, at greater than 400Hz from the carrier, is not greater than -50dB relative to 1mW.

# Frequency Shift Demodulation

(optional):

- (1) Frequency shift range, 85Hz to 850Hz.

- (2) Maximum keying speed 200 bauds.

- (3) Telegraph distortion not greater than 5% up to 100 bauds.

- (4) Telegraph output. Polar (double current) DC output approximately 100mA with choice of 6-0-6V or 80-0-80V. Normally positive on 'Mark'. Provision is made by internal adjustment for neutral (single current) operation.

- (5) Mark/space reversal is available to the operator and a 'tune' switch position is provided to permit tuning of the receiver without operating the teleprinter.

iMetering:

A meter is provided on the front panel to indicate RF level,.

AF level to line, FSK tune, and suitable performance or

supply test levels.

Power Supply:

100V-125V or 200V-250V,  $\pm 10\%$ , 45-65Hz.

Power Consumption:

Approximately 60VA (Basic receiver).

Approximately 90VA (Fully equipped).

**Environmental Conditions:**

The equipment is designed to meet certain of the requirements of the British Defence Specification DEF.133, L2, for ambient

temperature range of:

Operating Temperature  $-10^{\circ}$ C to  $+55^{\circ}$ C. Storage Temperature  $-40^{\circ}$ C to  $+70^{\circ}$ C. Relative Humidity 95% at  $+40^{\circ}$ C.

Dimensions:

Rack Mounted

In Bench Cabinet

Height: 178mm (7 in.) 220mm (8.65 in.) Width: 483mm (19 in.) 495mm(19.5 in.) Depth: 410mm(16.15 in.)445mm(17.5 in.)

Weight (approx):

22kg (48.5lb)

28kg (61.5lb)

#### FRONT PANEL CONTROLS AND FITTINGS

12 way Rotary Channel Selector Switch Rotary VFO Type Frequency Control

Tuning Rate Switch (Fast, Medium, Slow and Lock)

RF Tuning Control

AGC Time Constants Switch AFC On/Off Switch (Optional)

AFC Lock Lamp Mode Switch

Meter Facility Switch

Meter

Channel, Tune, Load

Loudspeaker

Loudspeaker Switch Headphone Socket IF Gain Control AF Gain Control

BFO Slow Motion Control Line Level Preset Adjusters

Filter Switch

Power On/Off Switch

#### REAR PANEL CONNECTIONS AND FACILITIES

Antenna Input Socket (BNC) Antenna Input Fuse Power Input Socket Mains Voltage Adjuster Panel Power Input Fuse Teleprinter Supply Fuse Teleprinter Supply Selector Switch **Ground Terminal** 34MHz Input/Output Socket 34MHz Input/Output Switch Frequency Standard Input/Output Socket Frequency Standard Internal/External Switch 35.4MHz to 65.4MHz Input/Output Socket 35.4MHz to 65.4MHz Input/Output Switch AGC Output (for diversity operation) Line Output(s) (2 outputs for ISB version only). Terminal Two 3mW, 600 - ohm outputs Strip Loudspeaker Output Mute Line FSK Output 1.4 MHz IF Output Socket

#### **ACCESS ORIES**

AA.660/A

Headset, 600 ohms, with ventilated ear cushions, lead and plug.

Headsets are also available with standard ear cushions and anti-perspiration covers.

Note: All accessories and optional facilities and modules to be specified at time of order.

# CHAPTER 1

# PRINCIPLES OF OPERATION

# CONTENTS

|                                                                                                       | Page                                      |

|-------------------------------------------------------------------------------------------------------|-------------------------------------------|

| INTRODUCTION                                                                                          | 1 - 1                                     |

| FREQUENCY SYNTHESIS                                                                                   | 1 - 1                                     |

| frequency standard                                                                                    | 1 - 2                                     |

| 1.4 MHz OUTPUT                                                                                        | 1 - 2                                     |

| 34 MHz OUTPUT                                                                                         | 1 - 2                                     |

| 35.4 to 65.4 MHz OUTPUT                                                                               | 1 - 2                                     |

| LOW FREQUENCY LOOP Tuning Example                                                                     | 1 - 2<br>1 - 3                            |

| LOWER TRANSFER LOOP Tuning Example                                                                    | 1 - 3<br>1 - 3                            |

| UPPER LOOP Tuning Example                                                                             | 1 - 4<br>1 - 4                            |

| UPPER TRANSFER LOOP Tuning Example                                                                    | 1 - 4<br>1 - 5                            |

| HF LOOP                                                                                               | 1 - 6                                     |

| rf/if/af section                                                                                      | 1 - 6                                     |

| RF UNIT Protection Stage RF Amplifier                                                                 | 1 - 6<br>1 - 7<br>1 - 8                   |

| FIRST MIXER                                                                                           | 1 - 8                                     |

| SECOND MIXER                                                                                          | 1 - 8                                     |

| MAIN IF/AF STAGES  Product and AM Detectors  AGC Detector  Audio Pre-amplifier  Loudspeaker Amplifier | 1 - 8<br>1 - 9<br>1 - 9<br>1 - 9<br>1 - 9 |

| ISB IF/AF BOARD                                                                                       | 1 - 9                                     |

| AUTOMATIC FREQUENCY CONTROL                                                                           | 1 - 9                                     |

| FREQUENCY SHIFT KEYING                                                                                | 1 - 10                                    |

## ILLUSTRATIONS

|                                                    | <u>Fig. No.</u>     |

|----------------------------------------------------|---------------------|

| Simplified Block Diagram: Overall Receiver         | (In Text)           |

| Simplified Functional Diagram: Frequency Synthesis | (At end of Chapter) |

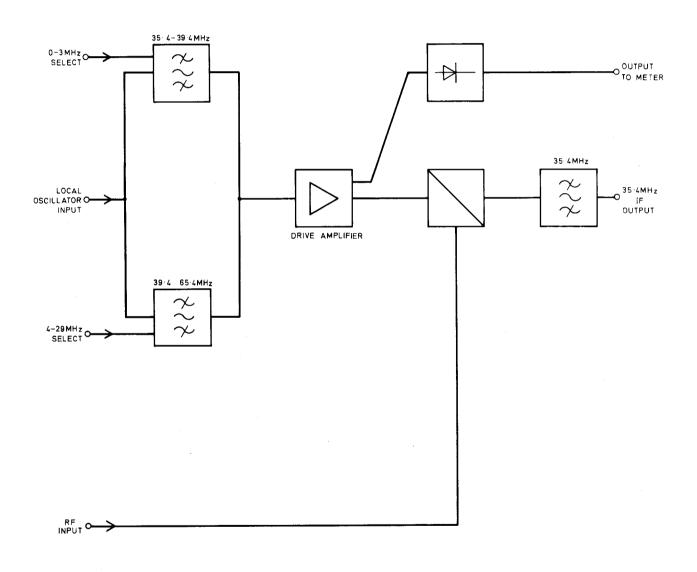

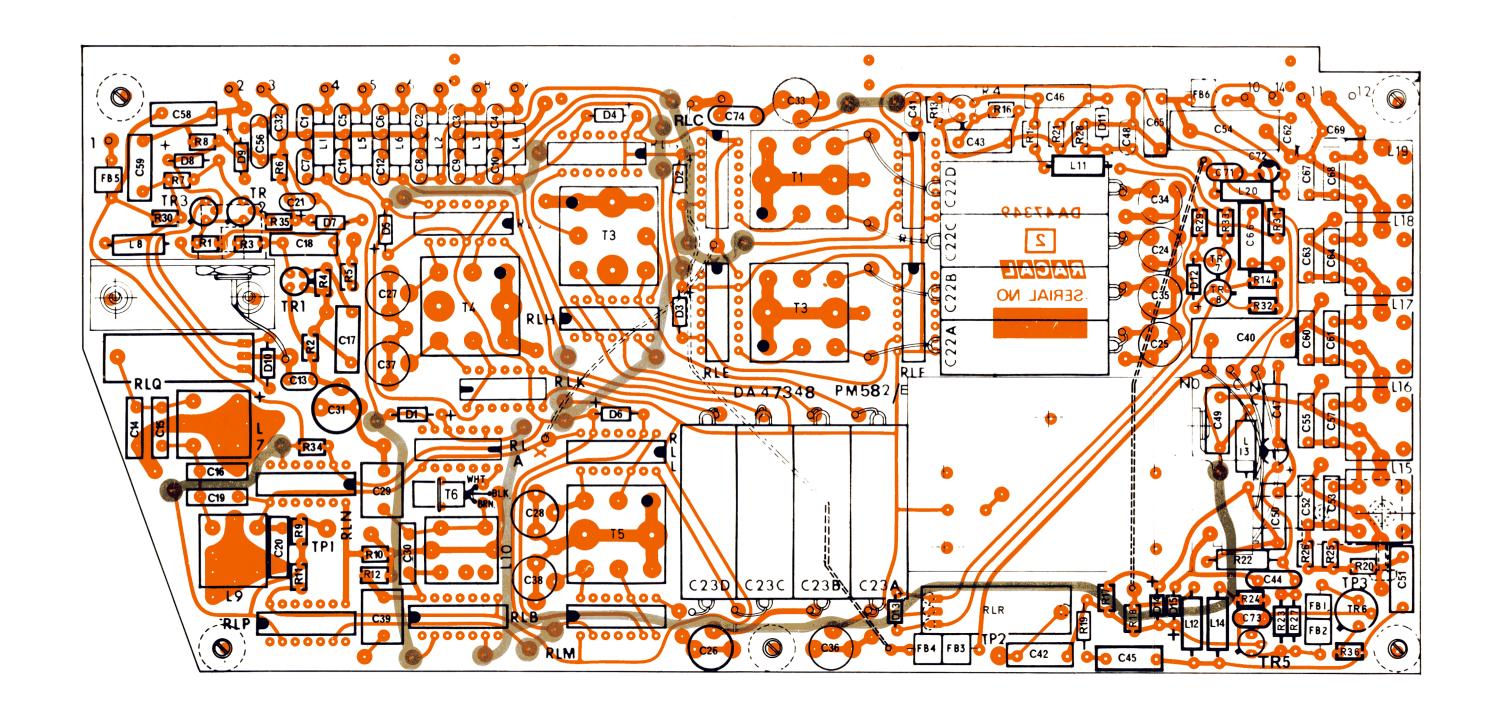

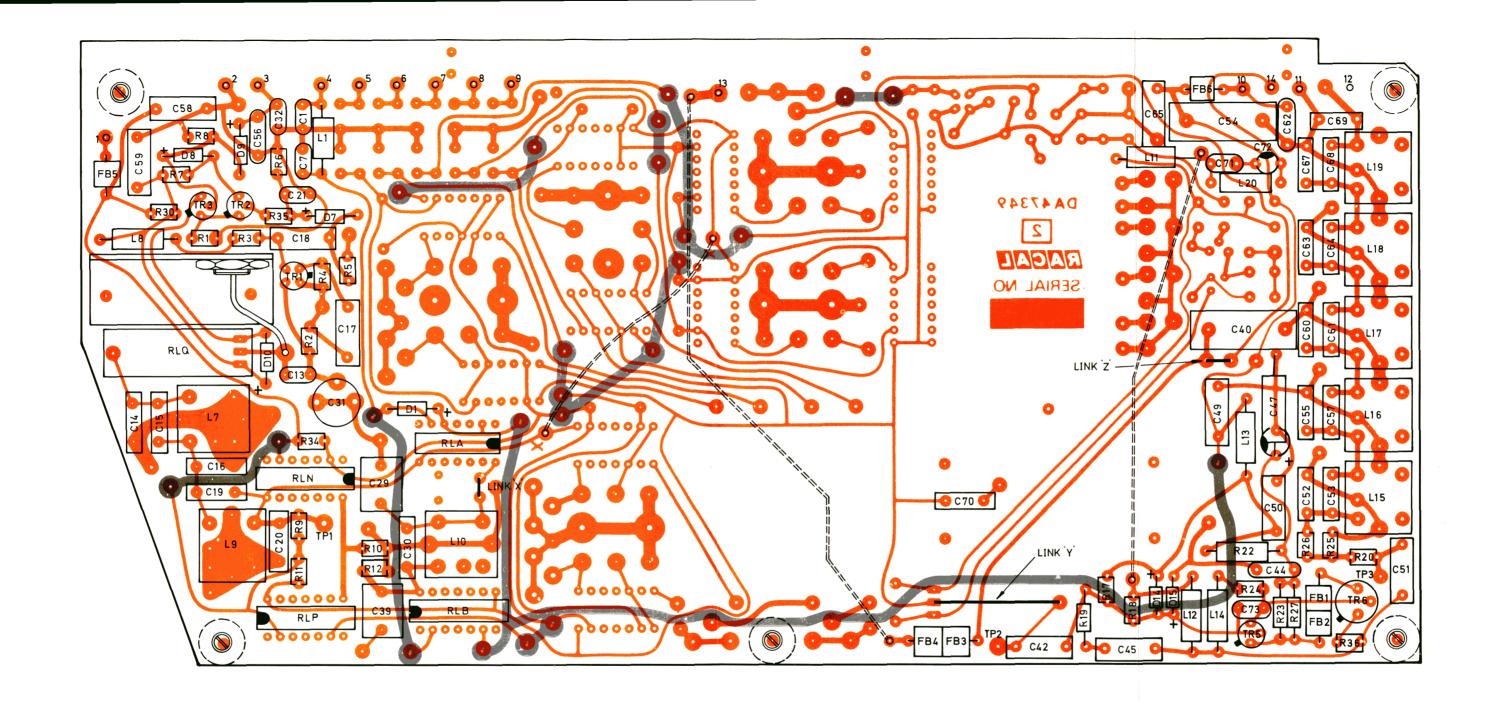

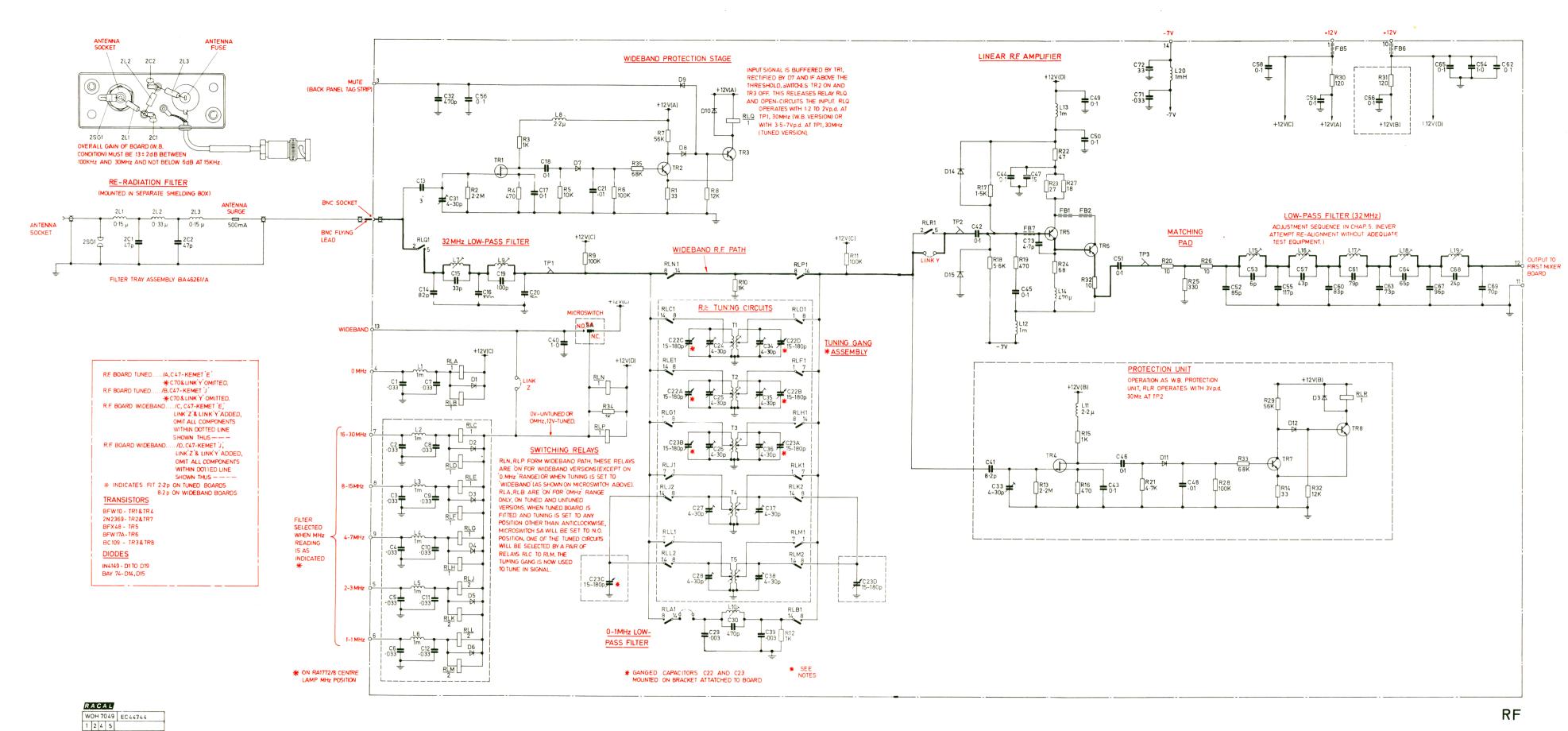

| Simplified Block Diagram: RF Unit                  | 1.3                 |

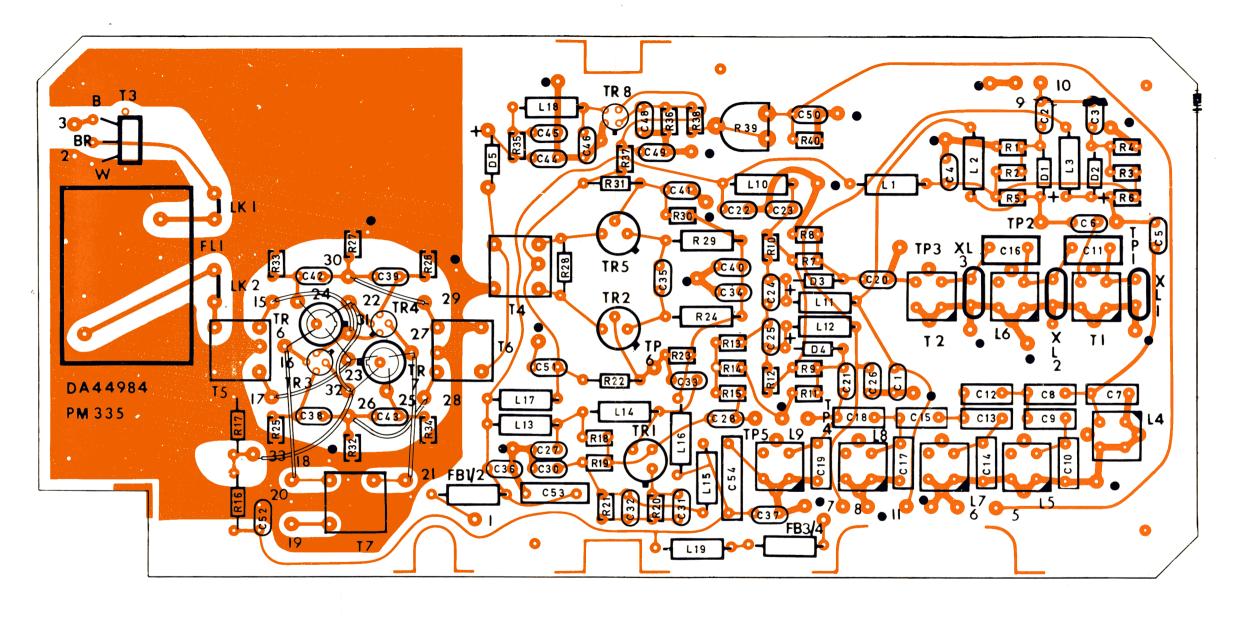

| Simplified Block Diagram: First Mixer              | 1.4                 |

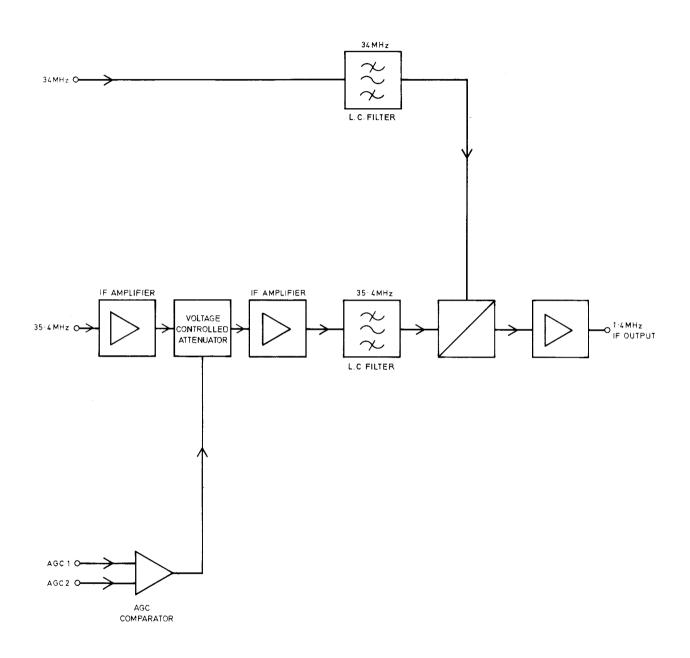

| Simplified Block Diagram: Second Mixer             | 1.5                 |

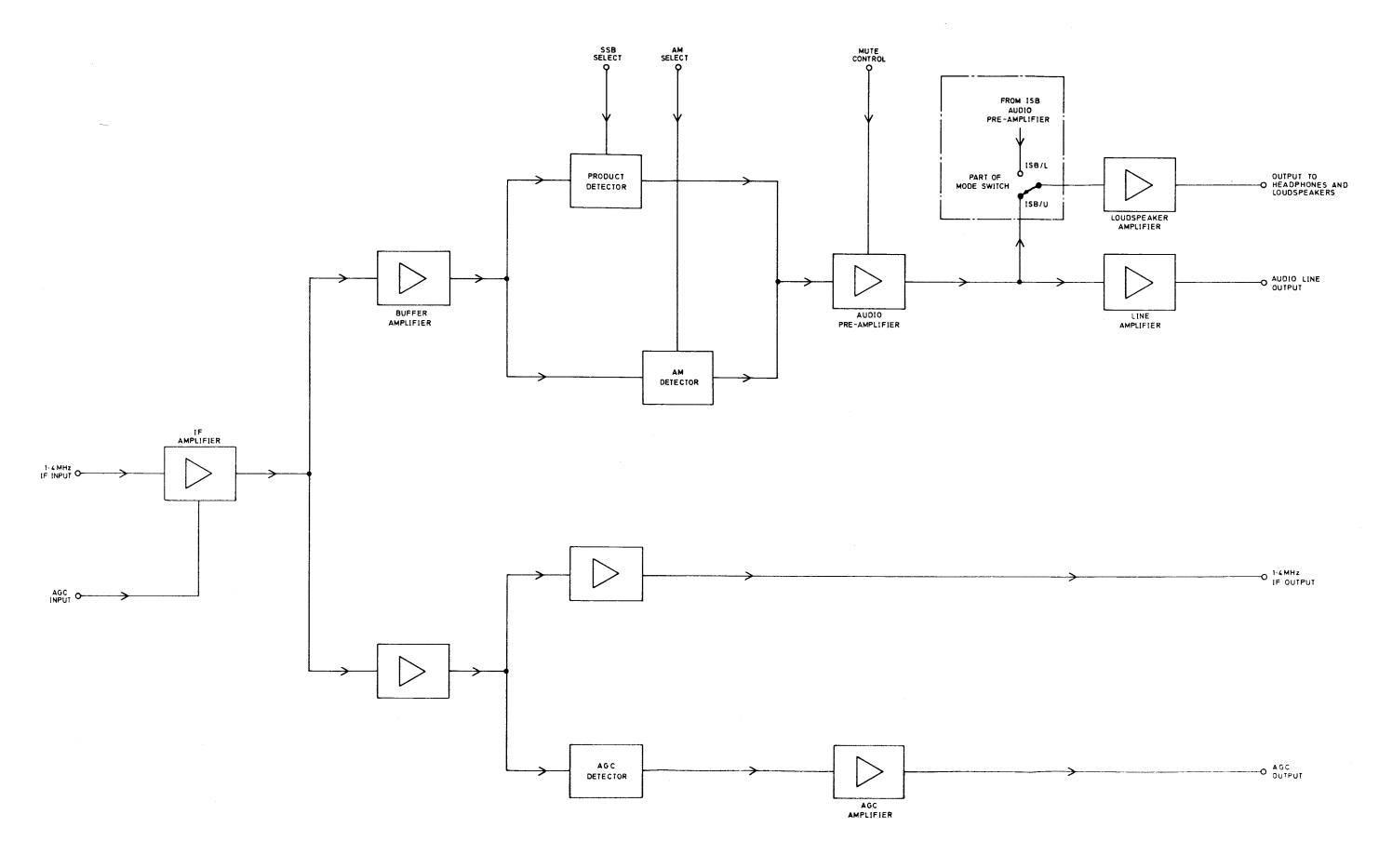

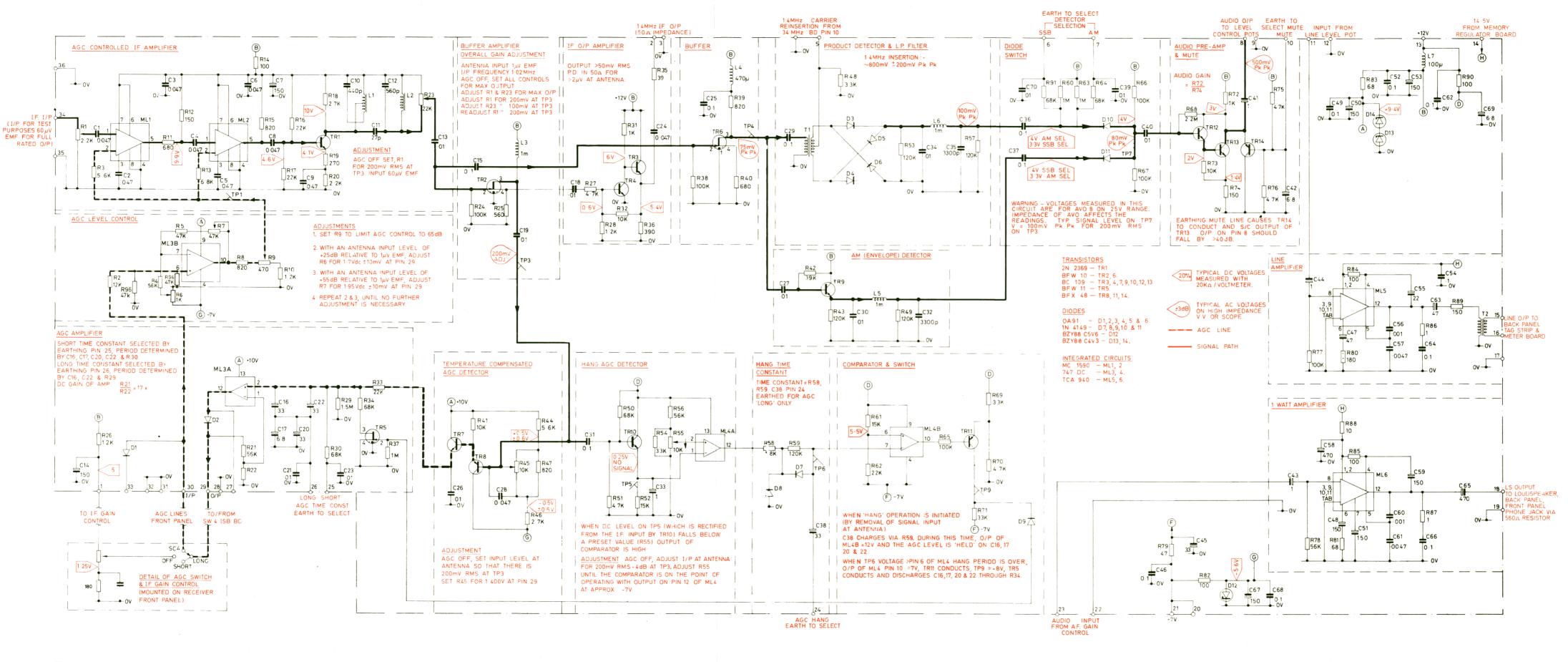

| Simplified Block Diagram: Main IF/AF Board         | 1.6                 |

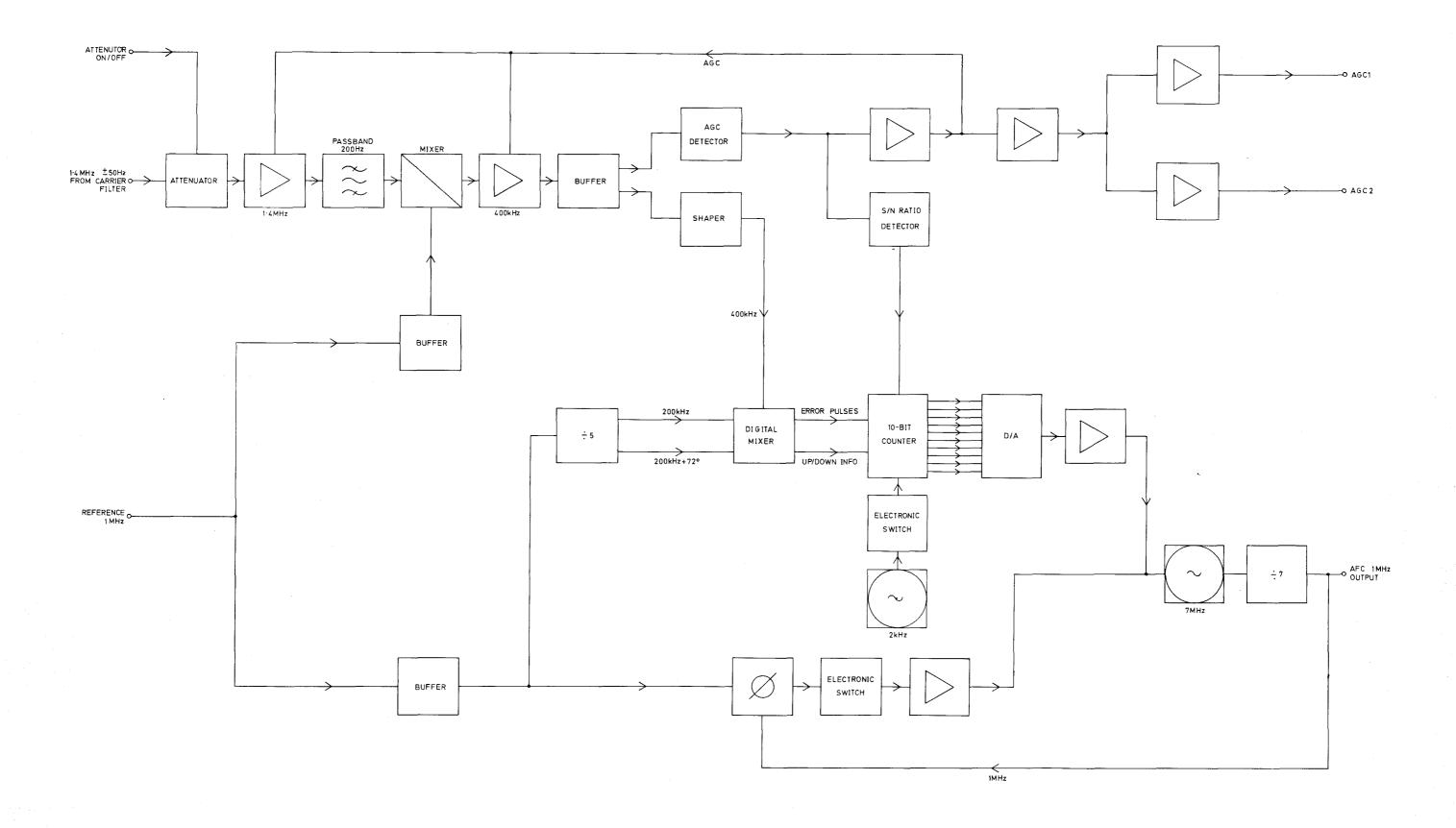

| Simplified Block Diagram: AFC Board                | 1.7                 |

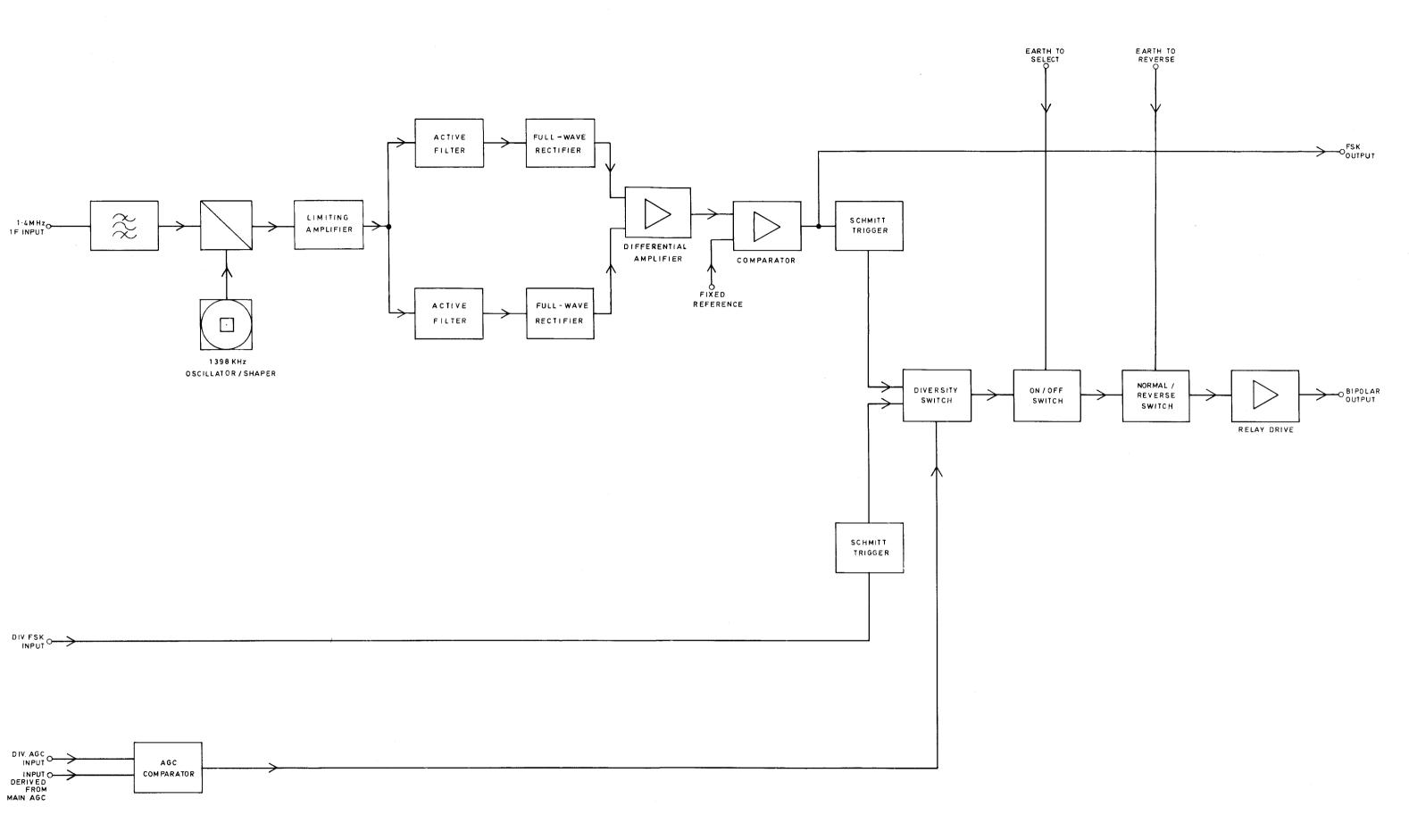

| Simplified Block Diagram: FSK Board                | 1.8                 |

| Overall Block Diagram RA.1778                      | 1.9                 |

| TABLES                                             |                     |

|                                                    | Page                |

| Table 1: Decimal to Nines Complement Conversion    | 1-5                 |

#### CHAPTER 1

#### PRINCIPLES OF OPERATION

#### INTRODUCTION

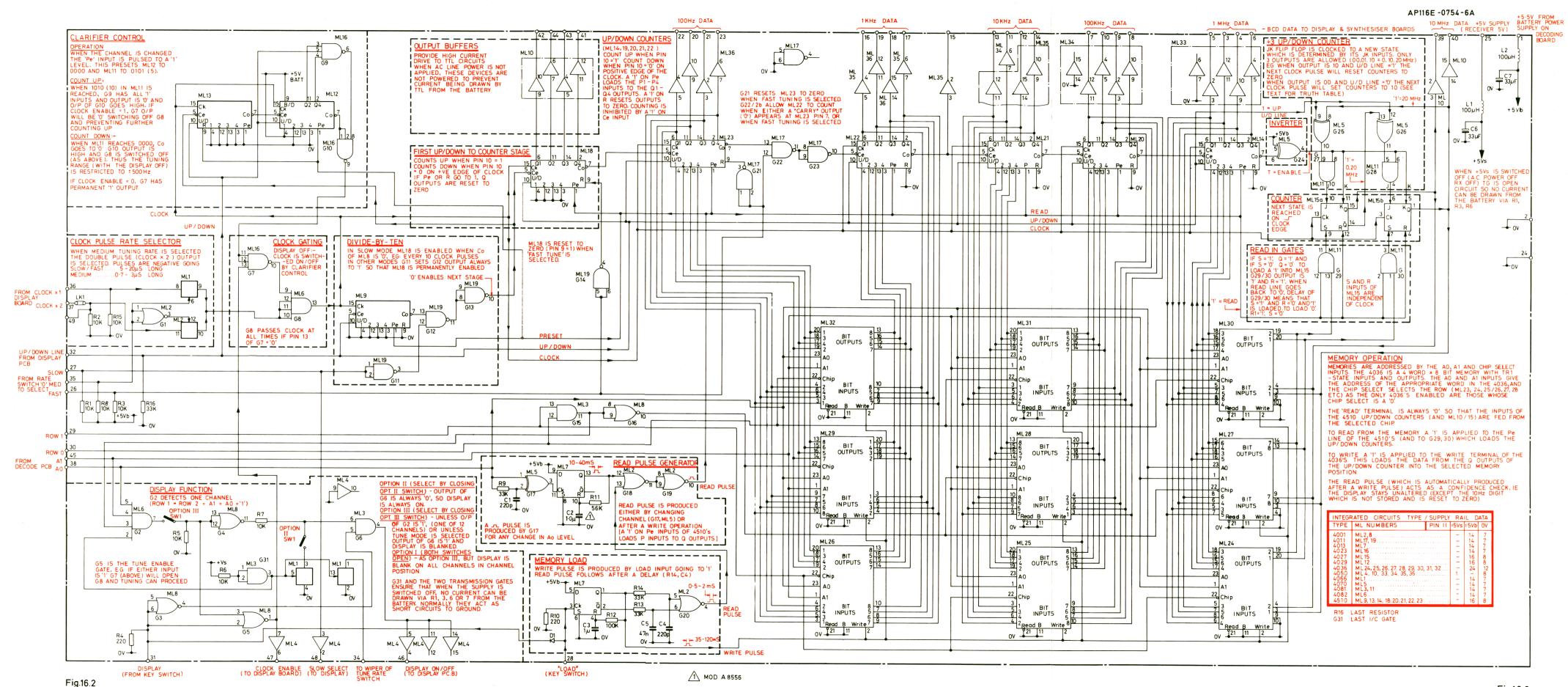

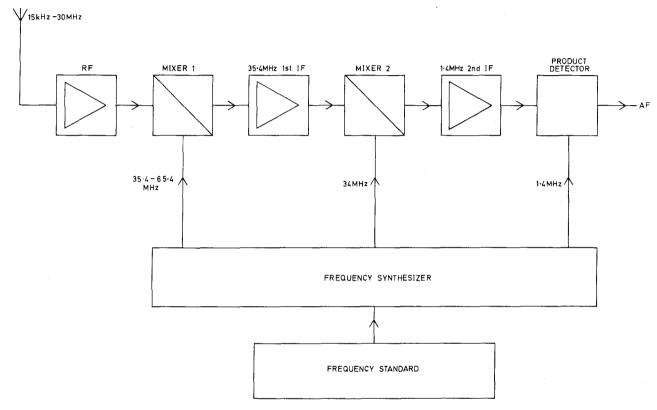

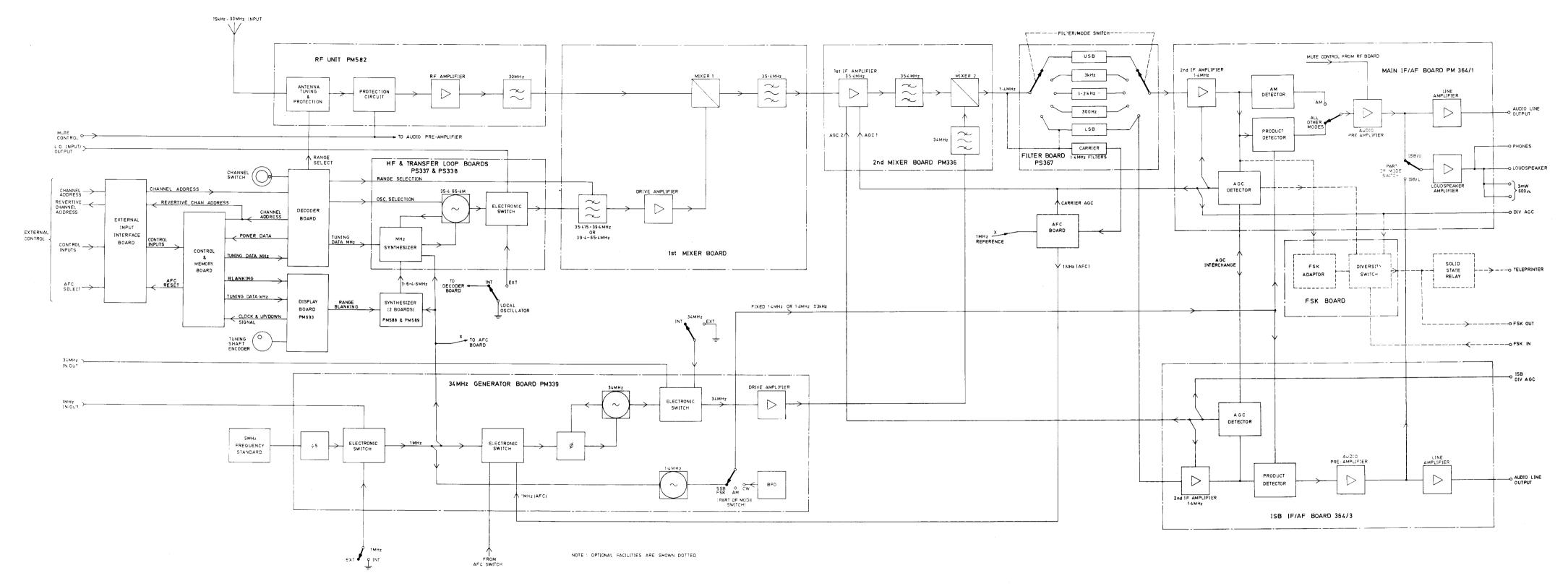

1. This chapter, in conjunction with the overall block diagram Fig. 1.9, describes the functional principles of the RA.1778 receiver. For explanation purposes, the receiver may be divided into two main sections, namely the frequency synthesizer and the RF/IF/AF section (see illustration below).

Simplified Block Diagram: Overall Receiver

Fig. 1.1

#### FREQUENCY SYNTHESIS

- 2. The above simplified block diagram of the RA. 1778 receiver shows the three mixer injection signals produced by the frequency synthesizer. The first IF, at 35.4MHz, is high, compared with the received signal frequency at the antenna, to provide good image rejection. To produce this first IF the frequency synthesizer must provide an output signal in the range 35.4 to 65.4MHz. The second IF, at 1.4MHz, is low to provide good selectivity, and the mixer requires a fixed frequency output signal from the synthesizer at 34MHz. Finally, a frequency of 1.4MHz is needed for the product detector for the reception of SSB signals.

- 3. The indirect method of frequency synthesis is used where the required output frequencies (with the exception of the 1.4MHz output) are derived from voltage-

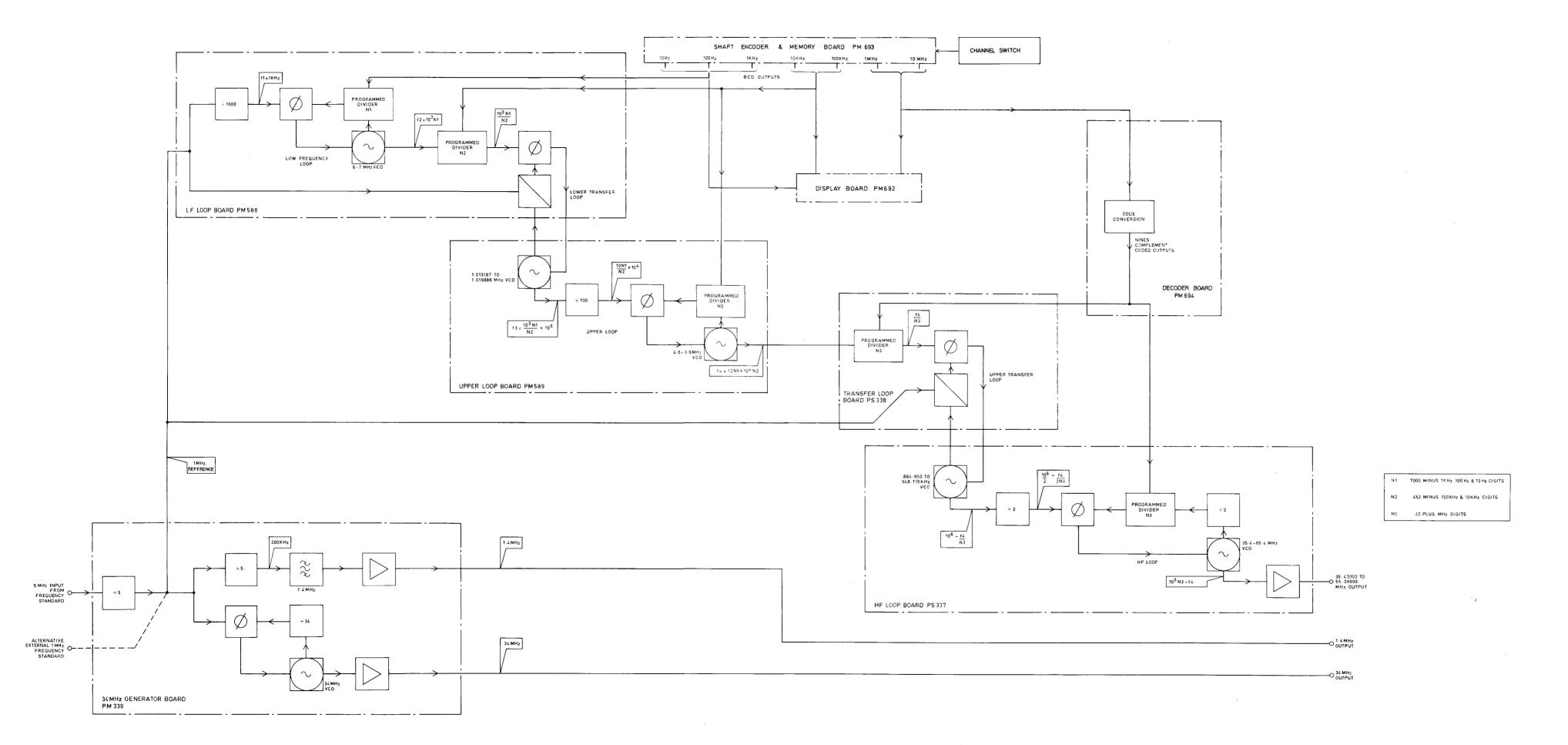

controlled oscillators which are phase locked to a common frequency standard. A simplified functional diagram of the frequency synthesizer section of the receiver is given in Fig. 1.2 at the end of the chapter.

#### FREQUENCY STANDARD

4. Any one of three types of 5MHz frequency standard may be fitted to the receiver, dependent upon the degree of frequency stability required. The output signal from the frequency standard is divided by five to produce a 1 MHz reference frequency for the synthesizer. Alternatively, provision is made for the use of an external 1MHz frequency standard.

#### 1.4MHz OUTPUT

5. The 1MHz reference frequency signal from the frequency standard is further divided by five to produce an output at 200kHz. A 1.4MHz crystal filter selects the seventh harmonic and this is amplified to produce a 1.4MHz output signal at the required level.

#### 34MHz OUTPUT

6. The 34 MHz second mixer injection frequency is derived from a 34MHz voltage controlled oscillator (VCO) which is phase locked to the 1MHz reference frequency. A sample of the VCO output is first divided by 34 and is then phase compared with the 1MHz reference frequency; any phase difference results in a correction voltage which is fed back to the VCO.

#### 35.4 to 65.4MHz OUTPUT

7. This is the main output signal from the frequency synthesizer; it covers the frequency range 35.40000 to 65.39999 MHz in 10Hz increments and is controlled by the output of the shaft encoder and counter or by the output of the 12-channel memory circuit. The output frequency is derived from five cascaded phase-locked loops. Digital frequency information is applied to these phase-locked loops along groups of four lines, one group per digit of frequency information.

#### LOW FREQUENCY LOOP

- 8. The low frequency loop consists of a 6 to 7 MHz VCO, a programmed divider, N1, and a phase comparator. The phase comparator compares the phase of the output signal from the programmed divider with that of a 1kHz reference frequency derived from the frequency standard. Should a phase difference exist, a correction voltage is derived which is fed back to the VCO to eliminate the error.

- 9. The programmed divider, N1, has a division ratio of from 7000 to 6001 and is controlled by the 10Hz, 100Hz and 1kHz digits of the selected receiver operating frequency; a receiver frequency setting of 000 sets the division ratio to 7000, a setting of 999 sets the division ratio to 6001, and the division ratio for intermediate frequency

settings is given by the expression: N1 = 7000 minus selected 1kHz, 100Hz and 10Hz digits. The divider consists of a number of cascaded decade counters where the start of a count sequence may be programmed by the frequency determining lines encoder and where the counter is reset (strobed) when a count of 7000 is reached. When the VCO has been driven to the correct frequency, reset (strobe) pulses will occur at a repetition rate of exactly 1000 pulses per second, as will the output pulses applied to the phase comparator.

#### **Tuning Example**

10. Consider a receiver operating frequency of 12.34567MHz. The first mixer injection frequency required to produce the first intermediate frequency of 35.4MHz is, therefore, 12.34567MHz + 35.4MHz, which equals 47.74567MHz. Returning to the operating frequency of 12.34567MHz, only the last three digits, i.e. 567, need be considered for this part of the circuit. Thus the programmed divider, N1, is preset to start counting at 567 and counts up to 7000, a total of 6433 pulses (7000-567); this is equal to a VCO frequency of 6.433 MHz.

#### LOWER TRANSFER LOOP

- 11. The lower transfer loop, so called because the low frequency increments at its input, i.e. the 10Hz, 100Hz and 1kHz digits, are transferred to its output, consists of a programmed divider, N2, a 1.013187 to 1.019886MHz VCO, a mixer and a phase comparator. It generates, together with the upper loop, the 100kHz and 10kHz digits of the variable output frequency.

- 12. The programmed divider, N2, has a division ratio of from 453 to 354 and is controlled by the 100kHz and 10kHz digits of the selected receiver operating frequency. (This division ratio is modified to cover the range 455 to 352 when in the overspill condition, i.e. 20kHz beyond either end of the selected 1MHz band). A receiver frequency setting of 00 for the 100kHz and 10kHz digits results in a division ratio of 453, a setting of 99 results in a division ratio of 354 and the division ratio for intermediate frequency settings is given by the expression: N2 = 453 minus the selected 100kHz and 10kHz digits.

- 13. The output signal for the low frequency loop is first divided by N2 and is then applied as one input to the phase comparator. The output from the VCO is mixed with the 1MHz reference frequency, derived from the frequency standard, and the difference frequency signal from the mixer is applied as the second input to the phase comparator. Thus the output voltage from the phase comparator drives the VCO to a frequency which is exactly 1MHz above the output signal frequency from the programmed divider, N2.

#### Tuning Example

14. Returning to the receiver operating frequency of 12.34567MHz (see paragraph 10), the 100kHz and 10kHz digits required are 3 and 4 respectively. The division ratio of N2 is, therefore, 453-34 = 419. The 6.433MHz output frequency from the low frequency loop is divided by 419 and the result is added to 1MHz.

Lower Transfer Loop Output =

$$\frac{6.433 \times 10^6}{419} + 10^6 \text{Hz}$$

$$= 1.015353 \text{MHz}$$

#### UPPER LOOP

15. The output signal from the lower transfer loop is first divided by 100 and is then applied as one input to a phase comparator; the other phase comparator input is from a programmed divider, N2, and a 3.6 to 4.6 MHz VCO is driven to the required frequency by the phase comparator output. The programmed divider, N2, is set to the same division ratio as that of the lower transfer loop, as described in paragraph 12.

#### Tuning Example

16. The 1.015353MHz output signal from the lower transfer loop (see paragraph 14) is first divided by 100 and is then multiplied by N2, i.e. 419.

Upper Loop Output =

$$\frac{1.015353}{100}$$

x 419

= 0.010154 x 419

= 4.25433 MHz

#### UPPER TRANSFER LOOP

- 17. This loop, in conjunction with the HF loop, generates the MHz portion of the variable output frequency, and is controlled by the MHz digits. It consists of a programmed divider, N3, a phase comparator, a mixer and a VCO which covers the frequency range 884.950 to 948.116 kHz.

- 18. The programmed divider, N3, has a division ratio of from 40 to 69. In contrast to the previously described programmed dividers, N1 and N2, the division ratio of N3 is found by adding 40 to the setting of the receiver MHz digits. This is achieved by first converting the decimal 0 to 29 output from the MHz digits into a 'nines complement' code before application to the programmed divider which counts from the programmed starting point up to 99, and then to 39 when the reset occurs. Table 1 gives the conversion from decimal to nines complement code.

| Decimal |   | ВС | :D |   | Ni | nes Comp | lement |    | Decimal |

|---------|---|----|----|---|----|----------|--------|----|---------|

|         | D | С  | В  | A | D9 | C9       | B9     | A9 |         |

| 0       | 0 | 0  | 0  | 0 | 1  | 0        | 0      | 1  | 9       |

| 1       | 0 | 0  | o  | 1 | 1  | 0        | 0      | 0  | 8       |

| 2       | 0 | 0  | 1  | 0 | 0  | 1        | 1      | 1  | 7       |

| 3       | 0 | 0  | 1  | 1 | 0  | 1        | .1     | 0  | 6       |

| 4       | 0 | 1  | 0  | 0 | 0  | 1        | 0      | ]  | 5       |

| 5       | 0 | 1  | 0  | 1 | 0  | 1        | 0      | 0  | 4       |

| 6       | 0 | 1  | 1  | 0 | 0  | 0        | 1      | 1  | 3       |

| 7       | 0 | 1  | 1  | 1 | 0  | 0        | 1      | 0  | 2       |

| 8       | 1 | 0  | 0  | 0 | 0  | 0        | 0      | 1  | 1       |

| 9       | 1 | 0  | 0  | 1 | 0  | 0        | 0      | 0  | 0       |

Table 1: Decimal to Nines Complement Conversion

19. The 4.6 to 3.6MHz output from the upper loop is divided by N3 and is then applied as one input to a phase comparator. The output from the VCO is mixed with the 1MHz reference frequency, derived from the frequency standard, and the difference frequency output from the mixer is applied as the second input to the phase comparator. Thus the output voltage from the phase comparator drives the VCO to a frequency which is equal to 1MHz minus the output frequency from the programmed divider, N3.

#### Tuning Example

20. The division ratio for the programmed divider, N3, is obtained by adding 40 to the MHz digits of the receiver operating frequency. Thus for the frequency of 12.34567 MHz (see para. 10), N3 will be 40 plus 12 which equals 52. The 4.25433MHz output from the upper loop (see para. 16) is divided by 52 and the result is then subtracted from 1MHz to give the upper transfer loop output frequency.

Upper Transfer Loop Output =

$$1 - \frac{4.25433}{52}$$

MHz

=  $1 - 0.081814$

= 918.186 kHz

#### HF LOOP

21. The output signal from the upper transfer loop is first divided by two and is then applied as one input to a phase comparator. The output from a 35.4 to 65.4MHz VCO is also divided by two and is then applied to the programmed divider, N3, which in turn provides the second input to the phase comparator. Thus the VCO is driven to the required frequency by the phase comparator output. The programmed divider, N3, is set to the same division ratio as that of the upper transfer loop.

#### Tuning Example

22. The 918.186kHz output from the upper transfer loop is first divided by two and is then multiplied by 2N3, i.e. 2 x 52, to give the final output frequency.

First Mixer Injection Frequency =

$$\frac{0.918186}{2}$$

× 2 × 52MHz

= 0.918186 × 52MHz

= 47.74567 MHz.

This figure is the receiver operating frequency plus the first intermediate frequency and agrees with the original frequency arrived at in paragraph 10.

23. A functional block diagram of the frequency synthesiser is given in Fig. 1.2 at the end of this chapter. To calculate the frequency or division ratio at any point in the circuit, calculate the values of N1, N2 and N3 from the frequency setting of the receiver, then substitute in the equations given. (These equations apply only when the synthesiser is in lock and the dividers are working correctly).

#### RF/IF/AF Section

24. The following paragraphs should be read in conjunction with the respective circuit diagrams (Figs. 1.3 to 1.9).

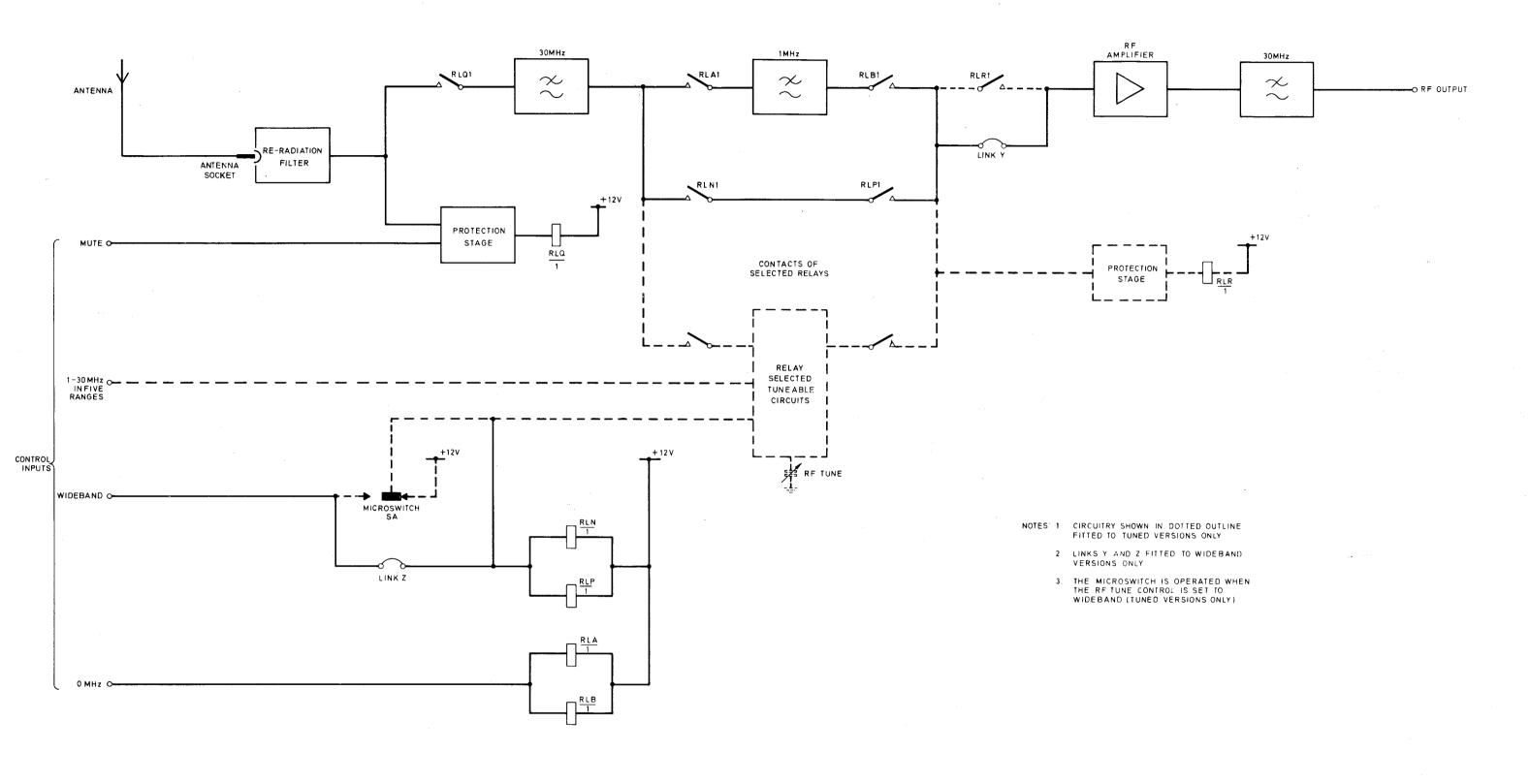

#### RF UNIT

- 25. The received signal at the antenna, in the frequency range 15kHz to 30MHz, is fed via a 500mA fuse and a re-radiation filter to a wideband protection stage. This consists of a voltage sensitive circuit and a relay (RLQ/1), which open-circuits the RF path for signals which exceed approximately 3V e.m.f. at the antenna socket. This relay is also used for receiver muting and operates when an earth is applied to the rear panel MUTE terminal. After operation of the relay the receiver is protected from input signals at the antenna socket of up to at least 30V e.m.f. with automatic recovery.

- 26. From relay contact RLQ1 the received signal is applied to a 30MHz low-pass filter and then takes one of a number of paths dependent on the selected position of the front panel MHz switch, as detailed below.

- 27. (1) MHz reading of OMHz: An earth from the decoder board is connected to relays RLA/1 and RLB/1. The relays energise, the received signal from RLQ1 and the low-pass filter is applied to a 1MHz low-pass filter, via RLA1, and thence, via RLB1 and contact RLR1 of the normally energised protection relay RLR/1, to the wideband RF amplifier.

- MHz reading of other than OMHz and RF TUNE control set to WB (wideband)

Operation of the microswitch SA (controlled by RF TUNE control) connects

an earth from the decoder board to relays RLN/1 and RLP/1. The relays

energise and a path is provided from the low-pass filter to the wideband RF

amplifier via RLN/1, RLP1 and contact RLR1 of the normally energised

protection relay, RLR/1.

- (3) MHz reading of other than OMHz, RF TUNE control not in WB position:

An earth from the decoder board is applied to the appropriate pair of tuneable-circuit selection relays and a common +12V relay supply is provided by the normally closed contacts of the microswitch. The contacts of the selected relays close and the received signal from the low-pass filter is applied to the appropriate tuned circuit, tuned by the RF TUNE control, and thence to the RF amplifier via RLR1.

#### Protection Stage

23. A further protection stage is fitted to the RF board. This allows for 'working through' off-tune signals of up to approximately 10V e.m.f. at the antenna socket The circuit is similar to that of the wideband protection stage; relay RLR/1 becomes de-energised once the 3V e.m.f. threshold is exceeded and the signal path to the RF amplifier is broken.

#### RF Amplifier

29. A conventional circuit of high linearity is used. After amplification, the received signal is passed via a 30MHz low-pass filter to the first mixer.

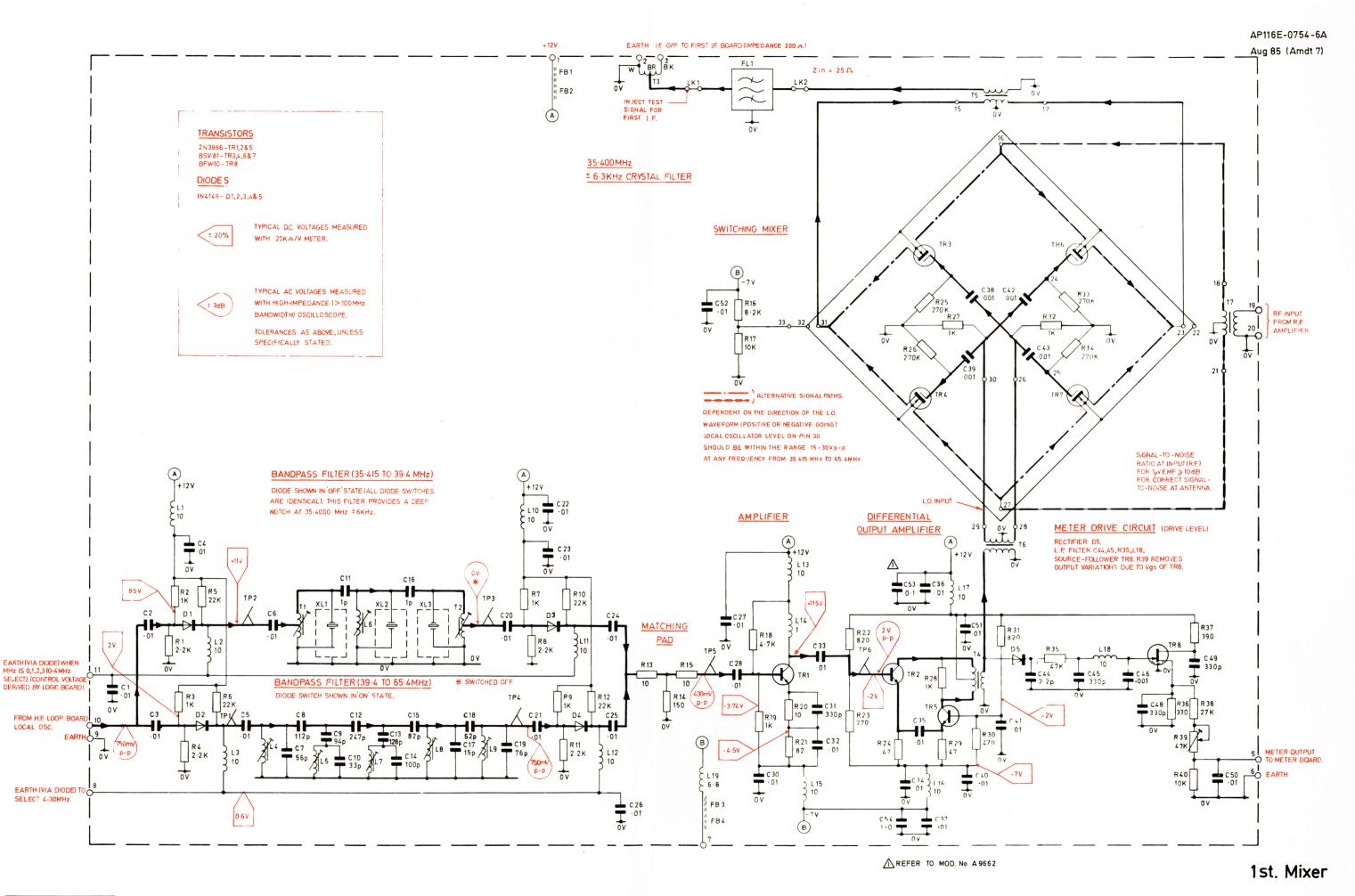

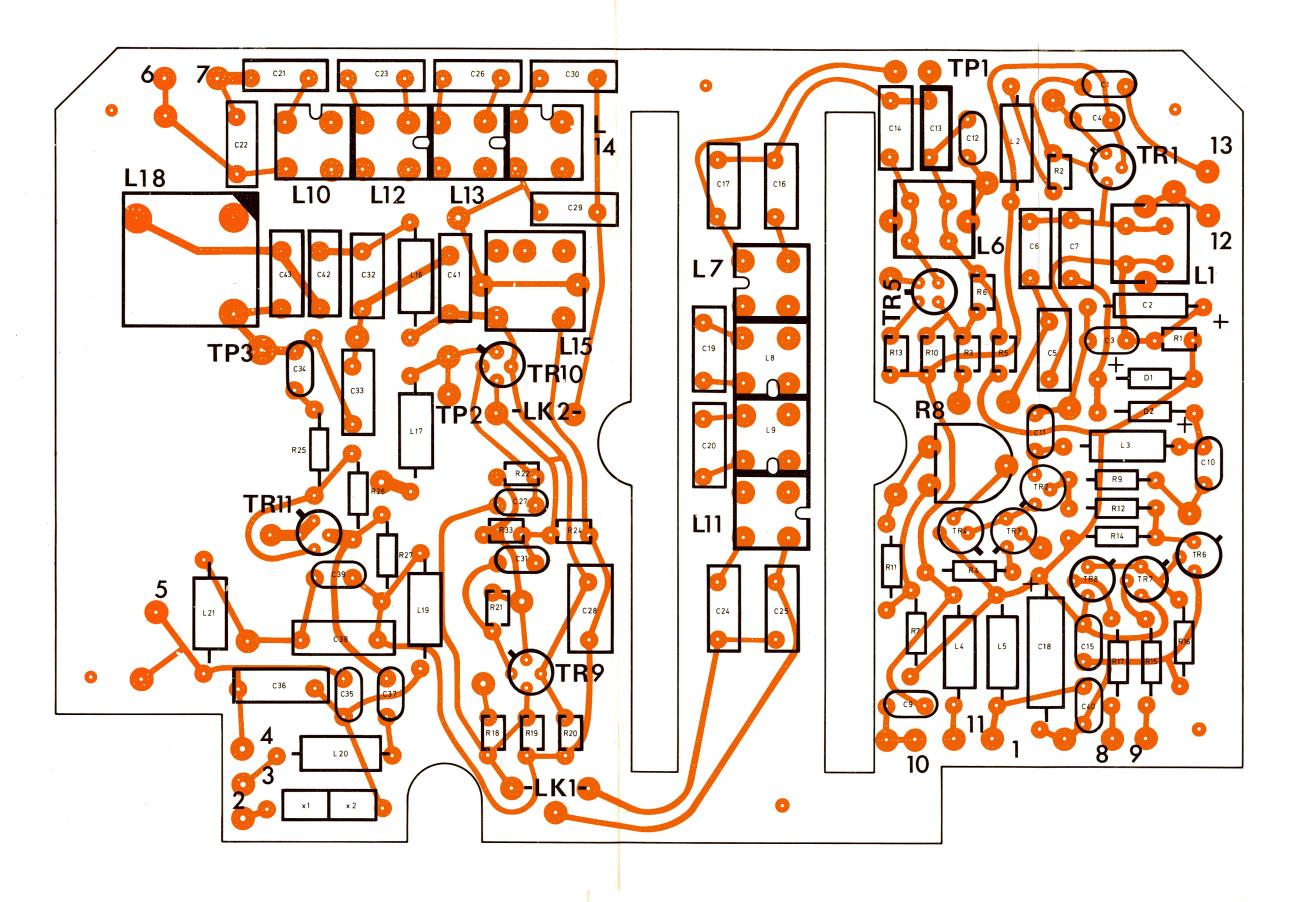

#### FIRST MIXER

- 30. The output signal from the RF unit is mixed with the 35.4 to 65.4 MHz local oscillator signal, from the frequency synthesizer, to produce the first IF at 35.4MHz.

- 31. The local oscillator signal is applied to one of two filters, dependant on the setting of the front panel MHz digits; for settings of 0, 1, 2 or 3MHz, a filter with a passband of 35.415 to 39.4MHz is selected whereas for settings of 4 to 29 MHz a filter with a passband of 39.4 to 65.4 MHz is selected. These filters attenuate noise at the IF frequency.

- 32. The output signal from the selected filter is applied to a drive amplifier and then to a high performance mixer. A detector and amplifier circuit provides an indication of DRIVE LEVEL at the front panel meter.

- 33. The output signal from the RF unit is mixed with the local oscillator signal and the difference frequency is fed via a 35.4 MHz band-pass filter to the second mixer.

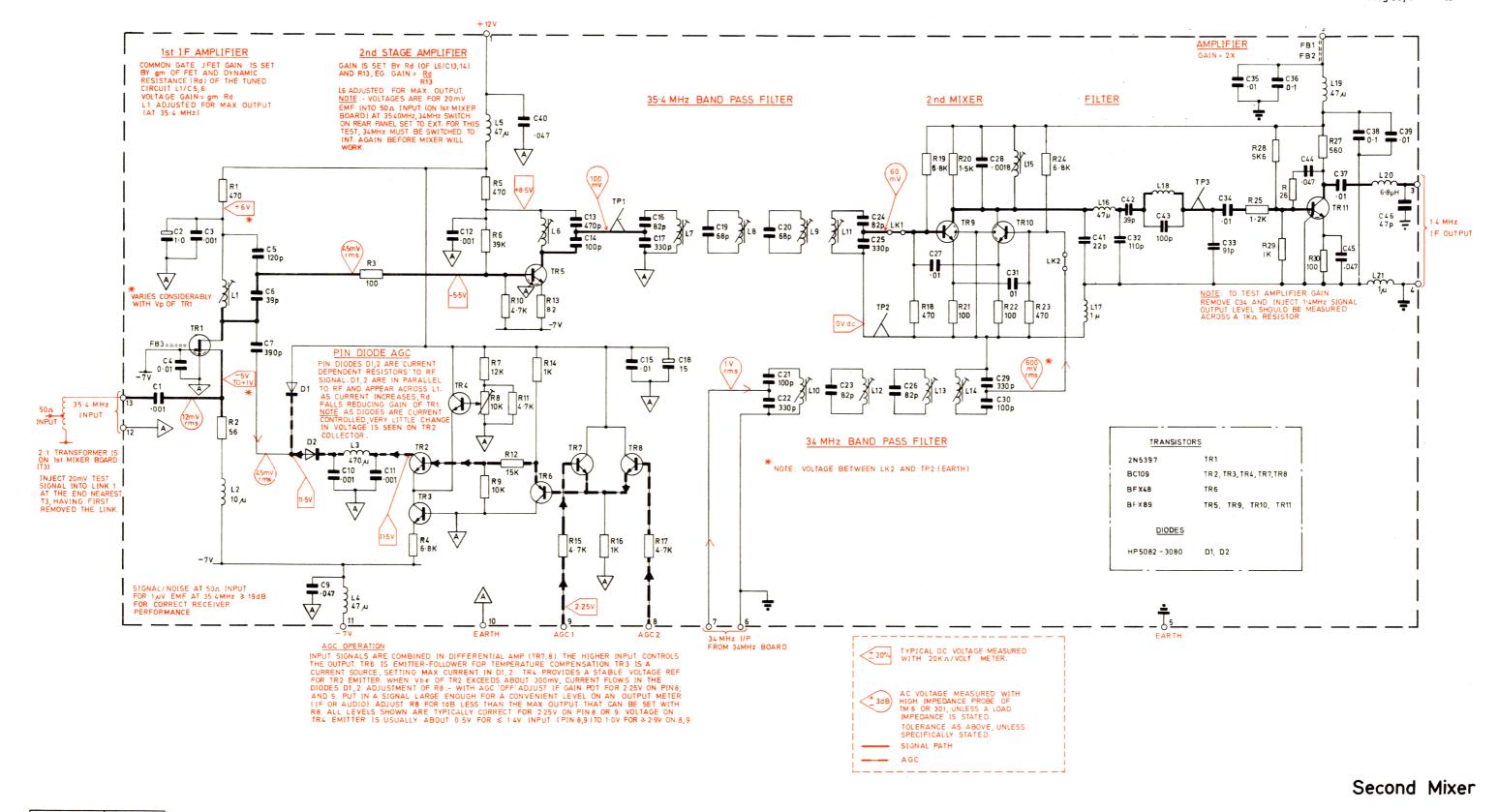

#### SECOND MIXER

- 34. The 35.4 MHz first IF output from the first mixer is amplified and is then mixed with the 34MHz output from the frequency synthesizer. This produces the second IF, at 1.4MHz, which is fed to the IF amplifier stages via the front panel selected SSB, 1SB or symmetrical filter (see Fig 1).

- 35. The output signal level from the first stage of IF amplification is automatically controlled by the AGC1 input from the main IF/AF board (and, in 1SB versions, AGC2 from the 1SB IF/AF board) via a voltage controlled attenuator. The output from the second stage of IF amplification is applied to a balanced mixer via a 35.4MHz band-pass filter.

- 36. The 34MHz second mixer injection frequency, from the frequency synthesizer section, is applied to the mixer via a 34MHz band-pass filter. The difference frequency output from the mixer, at 1.4MHz, is amplified before being applied to the filter board.

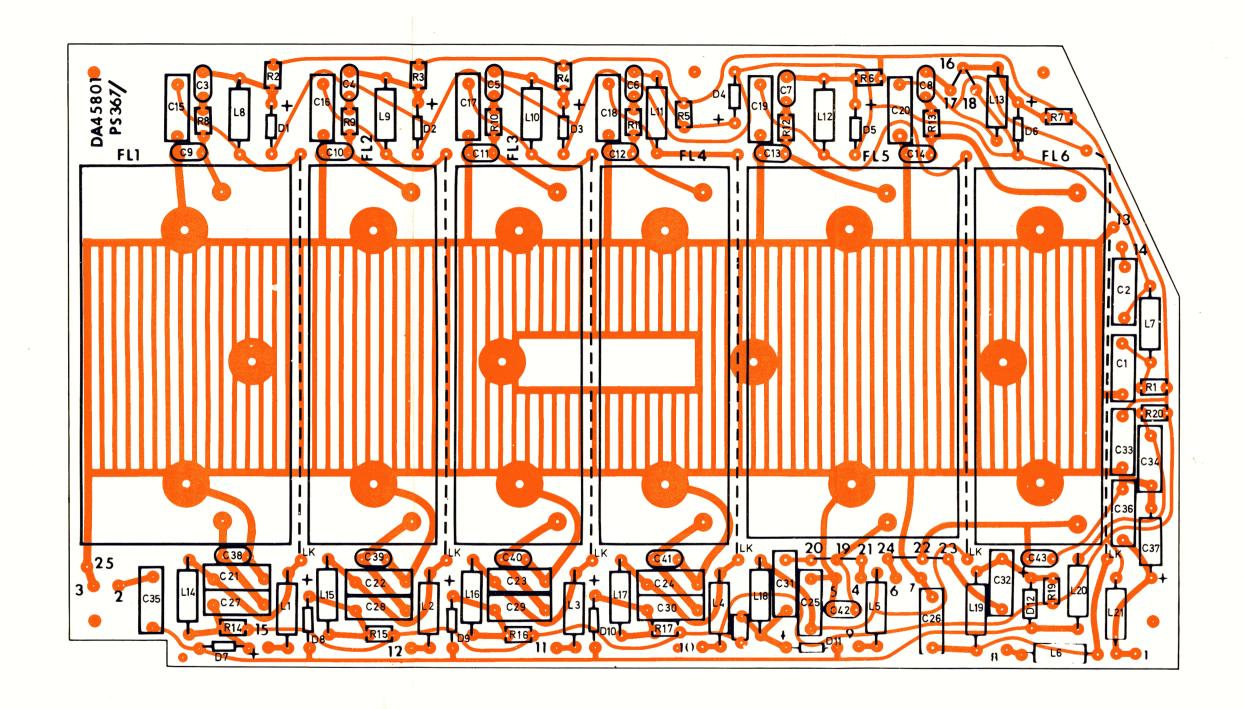

# MAIN IF/AF STAGES

37. The 1.4MHz second IF output signal from the second mixer is applied to the IF/AF board via the selected 1.4MHz filter (see Fig 1). The IF amplifier stage consists of two automatic gain controlled integrated circuit amplifiers. These feed two buffer amplifier stages; the output from one is applied to the product and AM detector, whilst the output from the other is applied to the AGC detector and the 1.4MHz output amplifier.

#### Product and AM Detector

38. Detector selection is controlled by the front panel MODE switch. The AM detector, which is of the envelope type, is selected in the AM position of the MODE 3 witch, and a modified Foster-Seeley type of product detector is selected for all other modes.

#### AGC Detector

39. The AGC detector develops a d.c. voltage which is proportional to the amplitude of the 1.4MHz IF signal. This gain control voltage, after amplification, is applied to the 35.4MHz first IF amplifier (on the second mixer board), a rear panel terminal and also to the 1.4MHz second IF amplifier via the front panel AGC switch. This switch provides for the selection of either a long or a short AGC time constant. In the OFF position the AGC voltage is removed from the 1.4MHz second IF amplifier and the gain of this stage is then controlled by the front panel IF GAIN control.

#### Audio Pre-Amplifier

40. The output signal from either the product detector or the AM detector is applied to the audio pre-amplifier. This stage has a muting capability such that the output is inhibited when an earth is applied to the MUTE terminal on the rear panel. The amplified audio output is applied to the line amplifier via the AM/USB LINE LEVEL control and also to the loudspeaker amplifier (the input switching to the loudspeaker amplifier is only necessary in ISB versions of the receiver).

#### Loudspeaker Amplifier

41. The loudspeaker amplifier provides a 50mW output for the internal loudspeaker, a 1 Watt, 8 ohm output for an externally connected loudspeaker, and two 10mW, 600 ohm headphone outputs.

# ISB IF/AF BOARD

42. This board, which is fitted to ISB versions of the receiver only, is similar to the main IF/AF board except that the AM detector is not utilised and a loudspeaker amplifier is not fitted.

#### **AUTOMATIC FREQUENCY CONTROL**

#### General Description

43. The purpose of the AFC system is to effectively stabilise the signal received from a drifting transmitter. This function is performed by slightly varying the frequency of the 34 MHz injection to the second mixer, maintaining a constant 1.4 MHz output signal. The 34 MHz injection is provided by an oscillator phase locked to an applied 1 MHz input signal.

- 44. With AFC switched OFF, the 34 MHz generator uses the 1 MHz derived directly from the frequency standard. When the AFC is switched ON, the generator uses a 1 MHz signal derived from the AFC board. The exact frequency of this signal is 1 MHz -

- $\underline{\Delta}$  where  $\Delta$  is the positive frequency error of the incoming carrier. The AFC board 34

accepts the 1.4 MHz carrier via the carrier filter, senses that an error is occurring, and adjusts the frequency of its 1MHz output to correct this error.

#### Operation of the Correction System.

- 45. The 1.4 MHz carrier arrives at the input of the AFC board, after extraction from the main IF signal via a 100 Hz carrier filter. The carrier is amplified, converted to 400 kHz by mixing with a 1 MHz signal and amplified again, resulting in a 400 kHz square wave suitable for driving CMOS.

- 46. The square wave is applied to the input of the digital mixer. The mixer is clocked by two 200 kHz signals spaced 72° in phase (1/5 of a clock period). The mixer provides two outputs, one a square wave at the error frequency the other d.c. up/down information which is a logic '1' for negative error, and a '0' for positive error, for example:

- (a) If the transmitter drifts 100 Hz high, the error output will be 100 Hz, and the output a '0'.

- (b) If the transmitter drifts 50 Hz low, the error output will be 50 Hz, and the up/down output a '1'.

The two outputs are fed to a 12-bit binary counter, which increments up or down at the error rate.

47. The ten most significant outputs (Q2 to Q11) are connected to a 10-bit digital to analogue converter, and the analogue output is used, after buffering and level shifting, as the varactor control voltage of a 7MHz oscillator. The 7MHz oscillator signal is divided down to 1MHz, and taken to the 34 MHz board. Since the correction rate is proportional to the error frequency, the lock up time is a logarithmic function of the initial error.

#### FREQUENCY SHIFT KEYING

- 48. The optional FSK board converts a frequency shift keyed signal into bipolar d.c. information suitable for operating a teleprinter or similar device. Provision is included for dual diversity operation (using a pair of receivers), with keying speeds up to 200 bauds and a frequency shift range of 85 Hz to 850 Hz.

- 49. The 1.4MHz IF output from the selected IF filter is applied to a mixer via a 1.4MHz band pass filter. The second input to the mixer is a 1398 kHz signal generated by a crystal oscillator. The difference output from the mixer at 2kHz, is clipped by a limiting amplifier and fed to a frequency discriminator consisting of two active band-pass filters and two full-wave rectifier circuits.

- 50. The output from the discriminator is compared with a reference voltage to produce a digital FSK signal which is taken to a rear panel terminal for connection to a second receiver for diversity operation; it is also applied via a schmitt trigger to a diversity signal comparator and switch.

- 51. An AGC comparator compares the diversity AGC input (from the second receiver) with a voltage derived from the AGC output from the main IF/AF board. The output from the AGC comparator, limited by a zener diode to either +5V (approximately) or -0.7V is applied to the diversity signal comparator and switch.

- 52. The diversity signal comparator and switch employs digital techniques to compare the two FSK signals from the master and slave receivers and, in conjunction with the information obtained from the AGC comparator, opens a path for the selected FSK signal. Switching only occurs when the mark or space output signal from one receiver is coincident with that from the second receiver. This is to avoid the introduction of switching distortion. The output signal from the diversity signal comparator and switch is routed by the MODE switch-controlled on/off and normal/reverse switching circuits to the relay drive amplifier.

Simplified Block Diagram : AFC Board PM664

# CHAPTER 2

# LOW FREQUENCY LOOP BOARD PM588

## CONTENTS

|                                          | Page |

|------------------------------------------|------|

| INTRODUCTION                             | 2-1  |

| 6-7MHz Voltage Controlled Oscillator     | 2-1  |

| Programmed Divider N1                    | 2-1  |

| Reference Frequency Divider              | 2-2  |

| HF Loop Phase Comparator                 | 2-2  |

| LF Loop Out-of-Lock Detector             | 2-3  |

| Programmed Divider N2                    | 2-3  |

| Mixer Stage                              | 2-4  |

| Lower Transfer Loop Phase Comparator     | 2-4  |

| Lower Transfer Loop Out-of-Lock Detector | 2-5  |

| Adjustments                              | 2-5  |

|                                          |      |

# **ILLUSTRATIONS**

|                                         | Fig.No. |

|-----------------------------------------|---------|

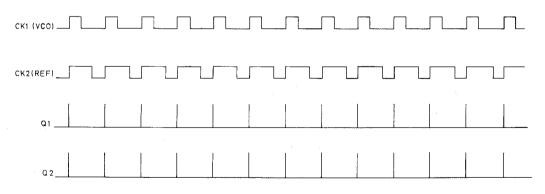

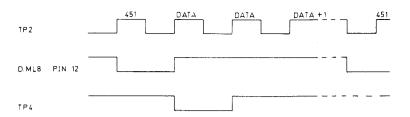

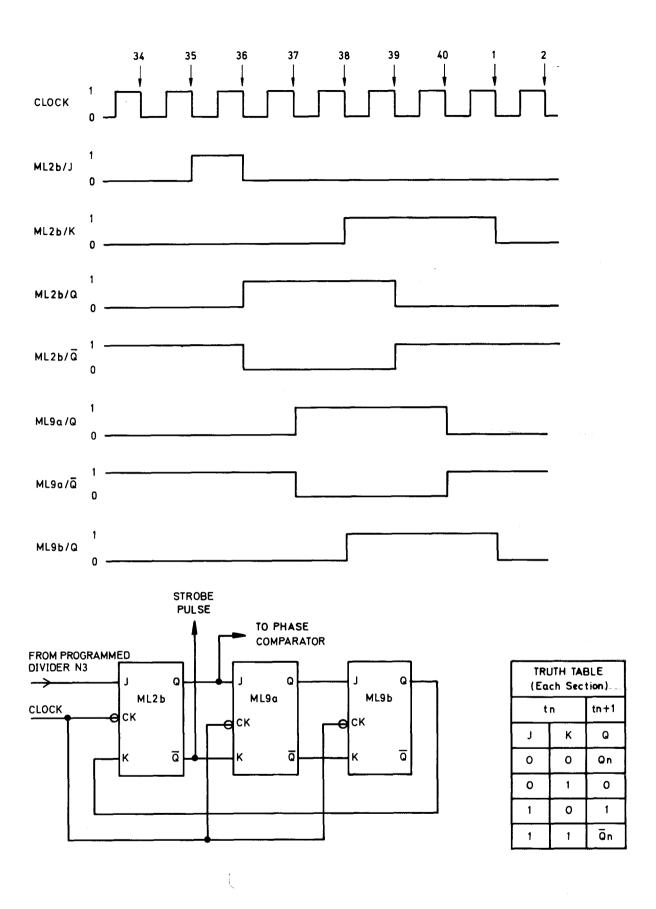

| Timing Diagram: Strobe Pulse Generation | 2.1     |

| Timing Diagram: Phase Comparator        | 2.2     |

| Timing Diagram: Out-of-Lock Detector    | 2.3     |

| Timing Diagram: Strobe Pulse Generation | 2.4     |

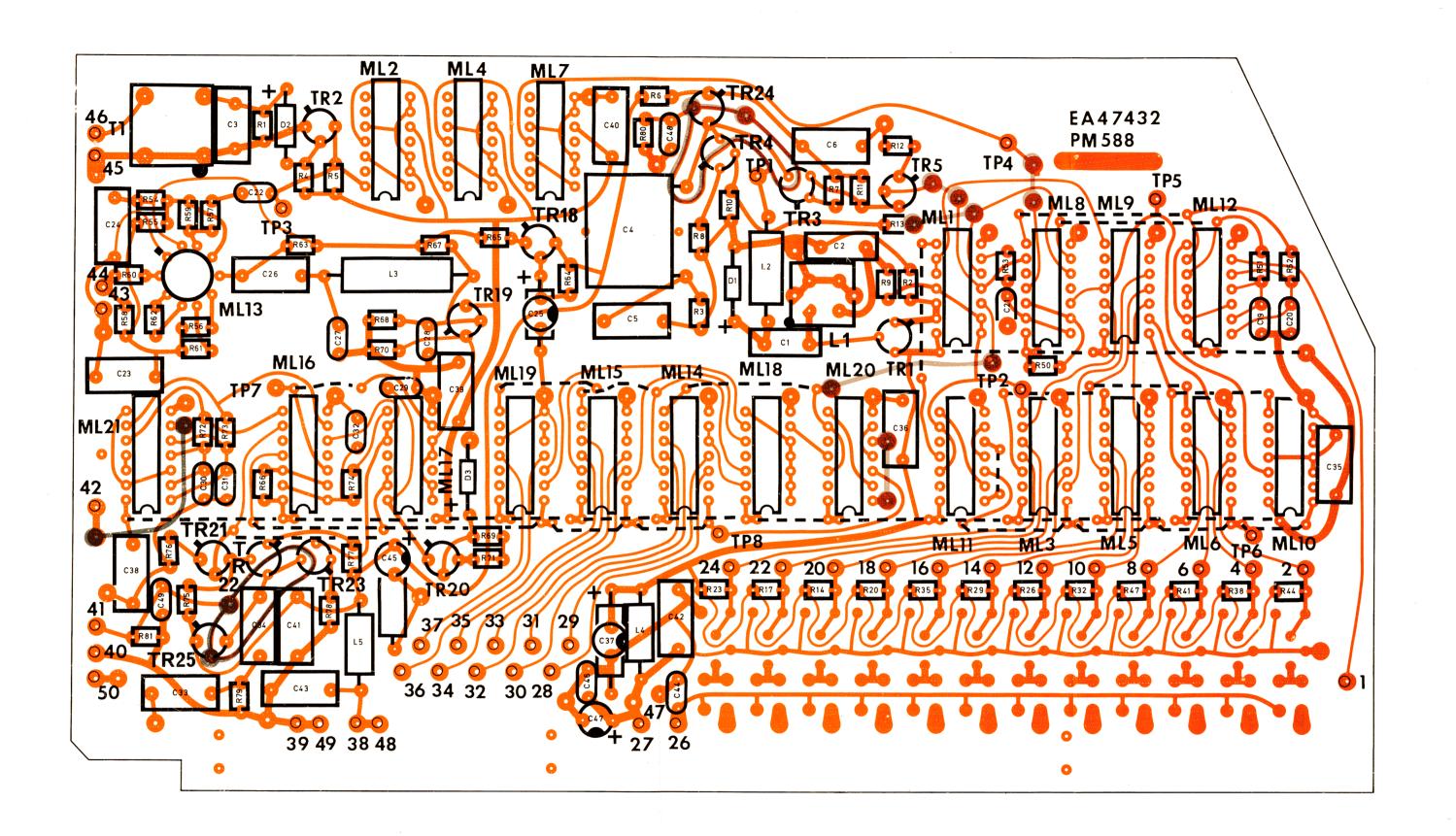

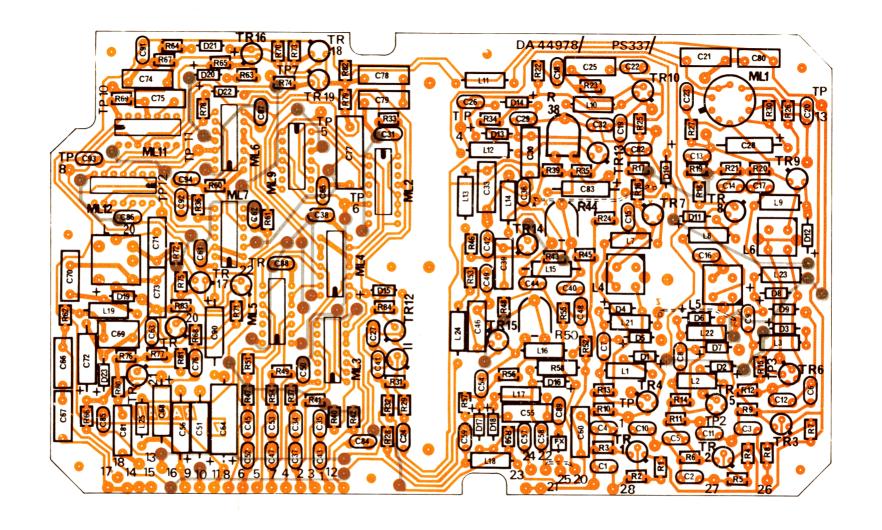

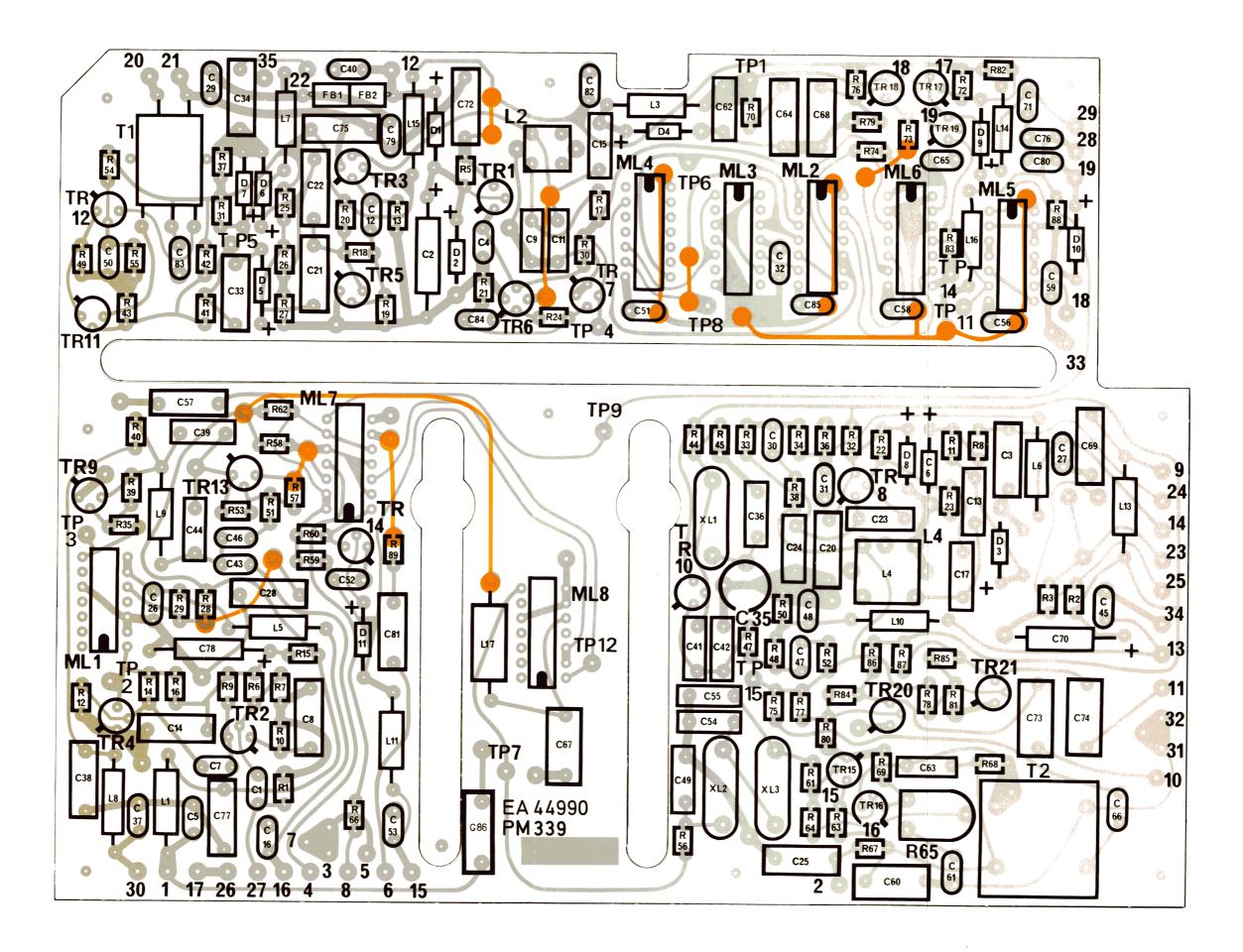

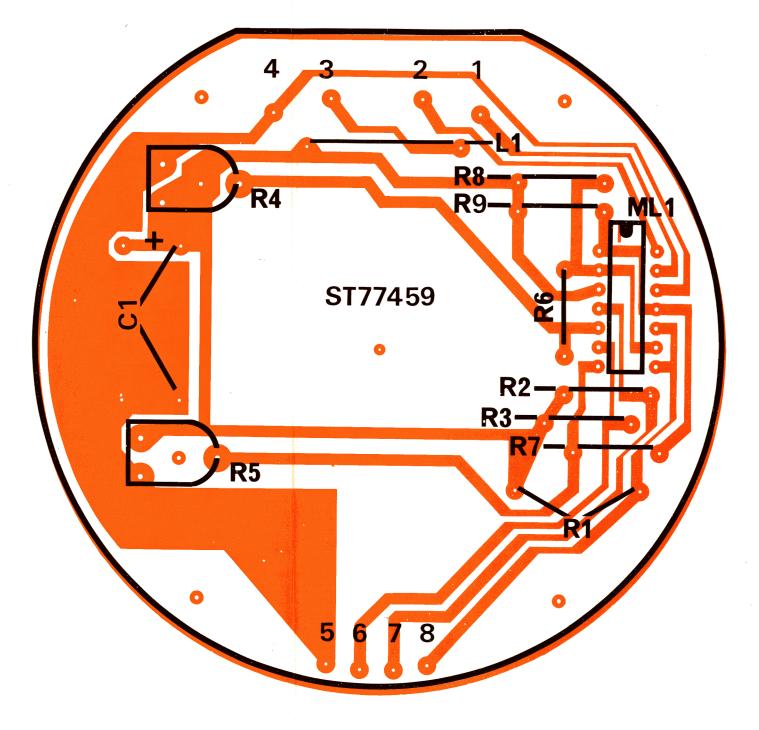

| Layout: Low Frequency Loop Board PM588  | 2.5     |

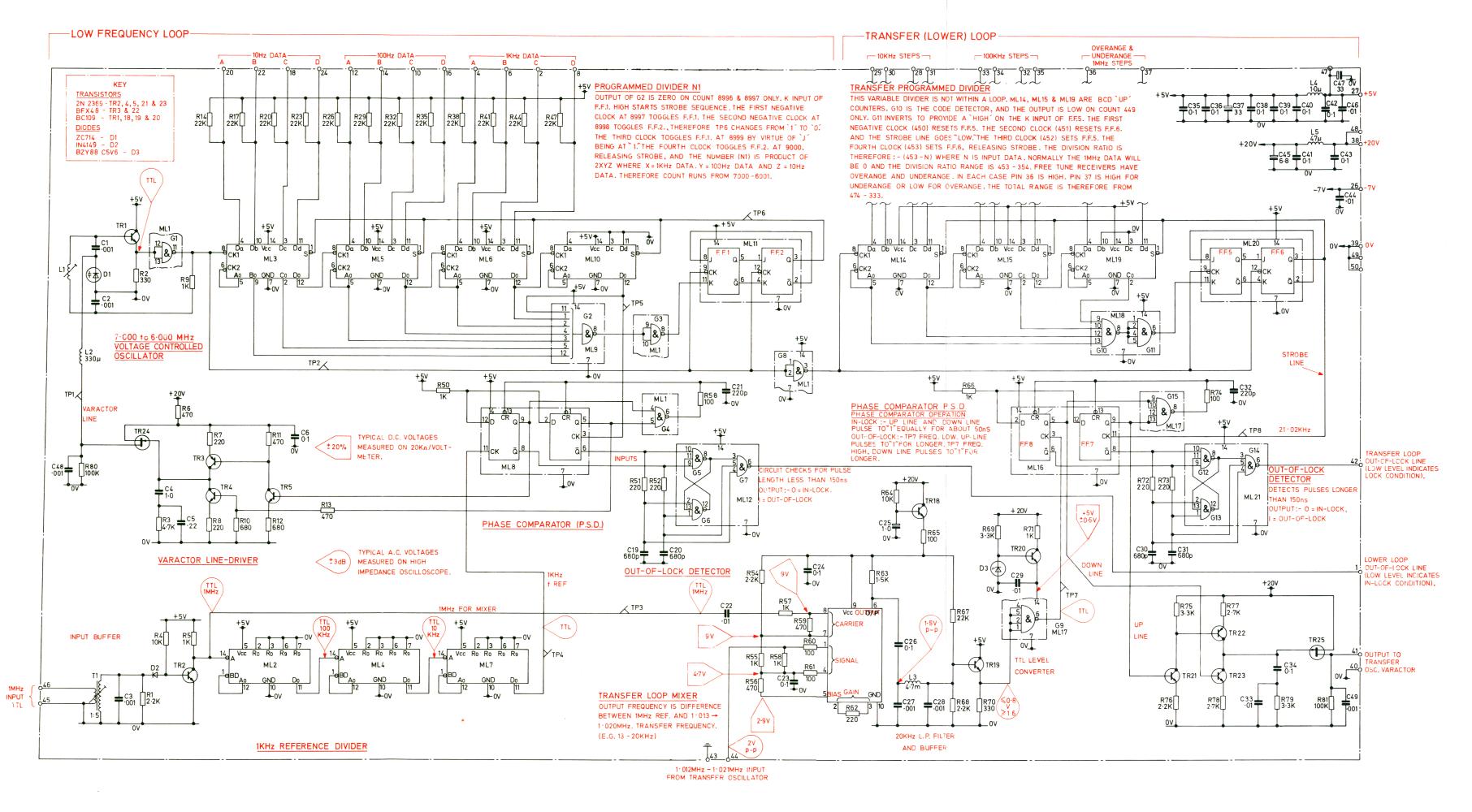

| Circuit: Low Frequency Loop Board PM588 | 2.6     |

#### CHAPTER 2

#### LOW FREQUENCY LOOP BOARD PM588

#### INTRODUCTION

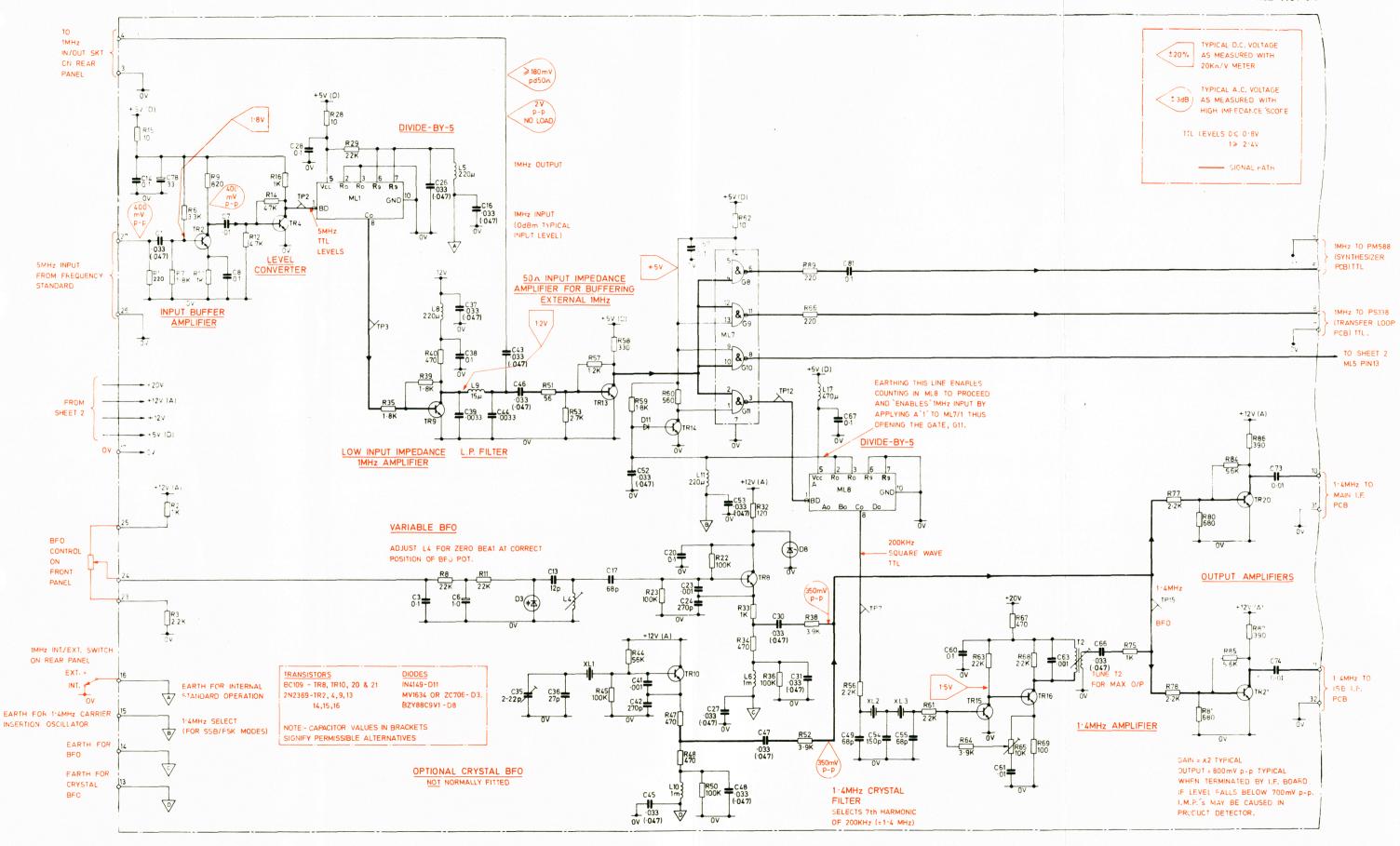

1. This board contains the low frequency loop and also the programmed divider, mixer phase comparator and out-of-lock detector circuits of the lower transfer loop; the lower transfer loop VCO is contained on the upper loop board (PM589). A circuit diagram of the board is given at the end of this chapter.

#### 6-7 MHz Voltage Controlled Oscillator (VCO)

2. The VCO is a Colpitts circuit consisting of L1, C2 and D1 (the varactor diode in series with C1.). The active component is ML1 buffered by transistor TR1. The square wave output signal is applied to the programmed divider, N1, and also to the programmed divider of the lower transfer loop, N2, via G8 (ML1).

#### Programmed Divider N1 (See Fig. 1.2)

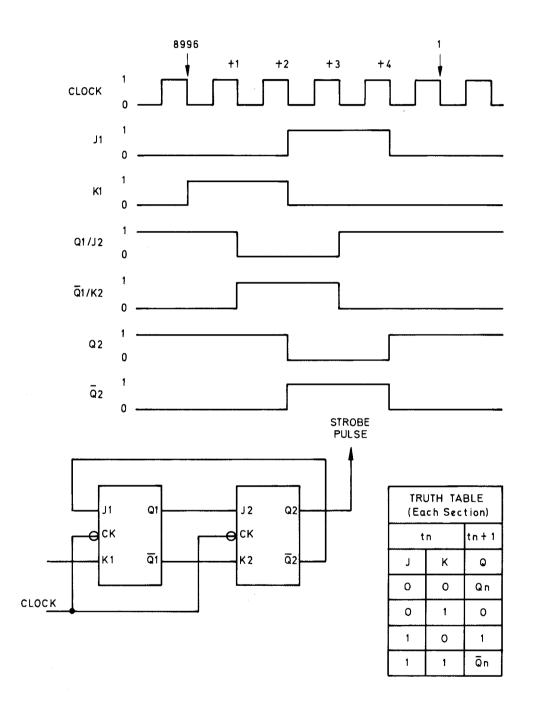

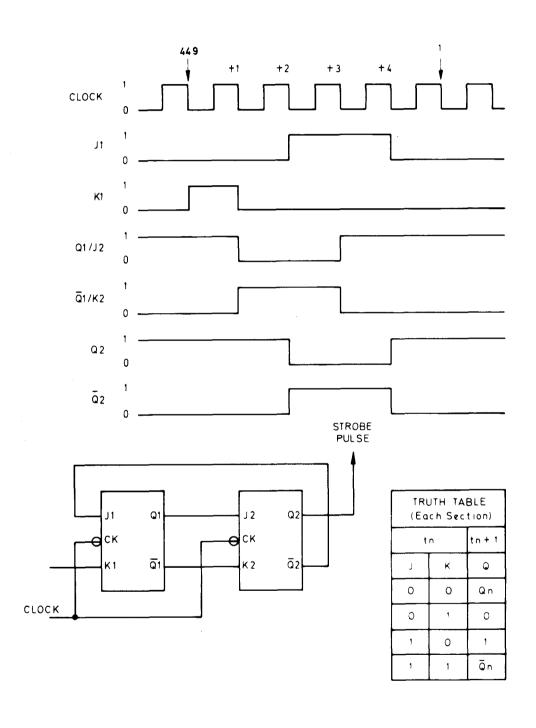

- 3. The programmed divider consists of four presettable decade counters, ML3, ML5, ML6, ML10, NAND gates G2, G3 and a dual J-K flip-flop, ML11.

- 4. The decade counters have strobed parallel-entry capability such that the starting point of a count sequence may be preset (see Technical Appendix A). A '1' or a '0' at a data input (Da, Db, Dc, Dd) is transferred to the associated output (Ao, Bo, Co, Do,) when the strobe (S) input is at '0'. The counting operation is performed on the negative-going edge of the input clock pulse.

- 5. The division ratio of the programmed divider, which is controlled by the 1kHz, 100Hz, 10Hz digits of the selected operating frequency, is given by the expression N1 = 7000 minus the selected digits, i.e. the division ratio is 7000 for a setting of 000 and is 6001 for a setting of 999. The operation of the divider is described below.

- 6. Binary coded decimal (BCD) frequency setting information is applied to the data inputs of ML3 (10Hz data), ML5 (100Hz data) and ML6 (1kHz data). The Da, Dc, and Dd data inputs of ML10 are connected to the OV line whilst the Db data input is floating and is equivalent to logic '1'. ML10, therefore, is set to start counting at binary 2.

- 7. To start a counting sequence, assume that a logic '0' strobe pulse is applied to the strobe (S) input of each decade counter. As described in paragraph 4, this causes the logic level applied to each input line (Da, Db, Dc, Dd) to be transferred to the corresponding output line (Ao, Bo, Co, Do). The negative-going edge of the clock pulse (from the VCO) is applied to the clock 1 input of ML3 and each pulse is now counted until an output from the counter of 8996 is reached, i.e. until the Do output from ML10 is at '1', the Ao and Do outputs from ML6 and ML5 are at '1', and the Bo and Co outputs

from ML3 are at '1'. Since ML10 is set to start counting at 2, and since the remaining counters may be set to start counting at any number from 0 to 9, the maximum number of clock pulses that may be counted is equal to 8996 minus 2000 which equals 6996.

8. Once a count of 8996 is reached, the input lines to the NAND gate, G2 are all at a logic '1' and the '0' output, inverted by G3, is applied to the K input of a dual negative edge triggered J-K flip-flop, ML11. The operation of this flip-flop, which generates the strobe pulse for the decade counters is given in the Timing Diagram, Fig. 2.1. From this diagram it can be seen that two clock pulses elapse before the start of the strobe pulse and a further two clock pulses elapse to coincide with the end of the strobe pulse. Thus four clock pulses are counted by ML11, making a total count of 7000, i.e. 6996 + 4.

## Reference Frequency Divider

9. The 1MHz input signal at board pins 45 and 46 is coupled by transformer T1 to a shaper stage, TR2. The output signal from the collector of TR2 is applied to a divider consisting of three cascaded decade dividers, ML2, ML4, ML7 and the output signal at 1000 pps, is applied to one of the clock inputs of the LF loop phase comparator, ML8.

## LF Loop Phase Comparator

- 10. The phase comparator consists of a dual D-type flip-flop, ML8, a two-input NAND gate, G4 and a voltage control circuit, TR3, TR4, TR5. It compares the output signal frequency from the programmed divider, N1, with the output signal frequency from the reference divider; any error between these two frequencies is used to develop a d.c. voltage which is applied to the 6 to 7 MHz VCO to eliminate the error. The action of the circuit is as follows:

- 11. The output signal from the programmed divider, N1, from ML10 pin 12, consists of positive-going pulses which are applied to the clock input of ML8b (Pin 3). The output signal from the reference divider also consists of positive-going pulses, and these are applied to the clock input of ML8a, (Pin 11). The D inputs of ML8, at pins 2 and 12, are both taken to the +5V rail (logic '1') via R50. Thus when the positive edge from ML10 pin 12 clocks ML8b, the Q output at pin 5 changes to '1' and the Q output changes to 'O'. Similarly, when the positive edge from the reference divider clocks ML8a, the Q output at pin 9 changes to '1' and the Q output changes to 'O'. When both Q outputs are at '1' the output from the NAND gate, G4 (ML1), changes to 'O' clearing both flip-flops at ML8 via R53 and thus resets the Q outputs to 'O' and the Q outputs to '1'.

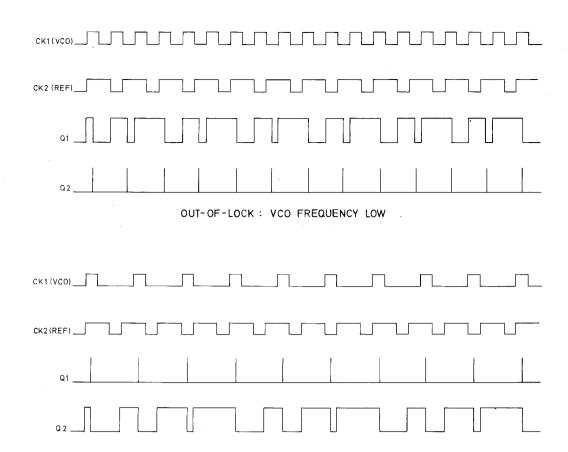

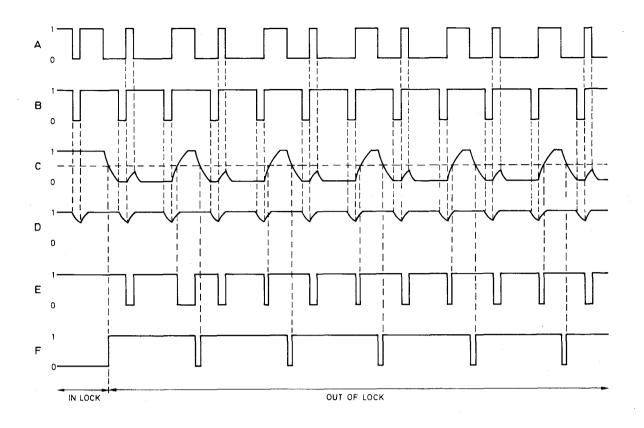

- 12. Consider the case where the 6 to 7 MHz VCO frequency is high. This will mean that the positive edge from the programmed divider will occur before the positive edge from the reference divider. The resulting setting and resetting of the flip-flops causes increased conduction of TR4, due to the Q output waveform from ML8b (see Timing Diagram Fig. 2.2) as compared with the conduction of TR5; this causes the voltage at the collector of TR4 to become less positive, thereby reducing the voltage applied to varactor diode, D1, and reducing the VCO frequency.

- 13. If the VCO frequency is low, the programmed divider output pulse will occur after the reference pulse, the Q output waveform from ML8a will cause increased conduction of TR5 and the voltage at the collector of TR4 will become more positive. The increased voltage applied to the varactor diode causes the VCO frequency to increase, thus correcting the error.

- 14. When the two signals are equal in frequency and phase the two flip-flops of ML8 are clocked at the same time, the two Q output waveforms are equal and varactor line voltage remains constant.

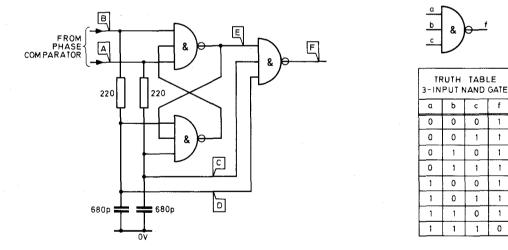

## LF Loop Out-of-Lock Detector

- 15. The LF loop out-of-lock detector consists of a bistable latch, G5, G6 and an output buffer, G7. The Q outputs from the phase comparator, ML8, are connected directly to G5, and also to G6 via integrating components, R50, C19 and R51, C20. Under phase-locked conditions the in-phase negative-going Q output pulses from ML8, pins 6 and 8 are prevented from reaching G6 due to the time constants presented by the integrating components. Pins 1 and 2 of G6 therefore float up to logic '1' and the resulting logic '0' output, at G6 pin 12, forces the output of G5 to logic '1'. The inputs to the output buffer, G7, are connected in parallel with those of G6 and the logic '0' in-lock indication output is taken to board pin 1.

- 16. When an out-of-lock condition exists, the clock input waveforms applied to ML8 are no longer in phase and the resultant longer-duration negative-going output pulses from ML8 pin 6 or ML8 pin 8 (dependant on whether a phase lead or a phase lag exists) are sufficient in width to overcome the time constant presented by the respective integrating components. The effect of this is to produce an alternating '0' '1' output signal from the buffer, G7, as shown in the timing diagram, Fig. 2.3.

## Programmed Divider N2 (See Fig. 1.2).

- 17. This programmed divider, which forms part of the lower transfer loop, consists of three presettable decade counters, ML14, ML15, ML19, NAND gates, G10, G11 and a dual J-K flip-flop, ML20.

- 18. The decade counters have strobed parallel entry capability such that the starting point of a count sequency may be preset. A '1' or a 'O' at a data input (Da, Db, Dc, Dd) is transferred to the associated output (Ao, Bo, Co, Do) when the strobe (S) input is at 'O'. The counting operation is performed on the negative-going edge of the input clock pulse.

- 19. The division ratio of the divider is controlled by the 10kHz and 100kHz digits of the selected operating frequency. The division ratio is given by the expression N2 = 453 minus selected digits; i.e. the division ratio is 453 for a setting of 00 and is 354 for a setting of 99.

- 20. BCD frequency setting information is applied to the data inputs of ML14 (10kHz data) and ML15 (100kHz data). The data inputs to ML19 are all at 0V (logic '0') and under this condition ML19 starts counting at zero.

- 21. To start a counting sequence, assume that a logic '0' strobe pulse is applied to the strobe (S) input of each decade counter. As described in paragraph 19, this causes the logic level applied to each data input line (Da, Db, Dc, Dd) to be transferred to the corresponding output line (Ao, Bo, Co, Do). The negative-going edge of the clock pulse (the output from the LF loop via G8) is applied to the clock 1 input of ML14 and each pulse is counted until a count of 449 is reached, i.e. until the Co output from ML19 is at '1'. Thus when a count of 449 is reached the four input lines to the NAND gates G10 are at logic '1' and the resulting '0' output, inverted by G11, is applied to the K input of a dual, negative-edge triggered, J-K flip-flop, ML20. The operation of this flip-flop, which generates the strobe pulse for the decade counters, is given in the timing diagram, Fig. 2.4. From this diagram it can be seen that two clock pulses elapse before the start of the strobe pulse and a further two clock pulses elapse to coincide with the end of the strobe pulse, thus four clock pulses are counted by ML20, making a total count of 453, i.e. 449 + 4, before the start of the next sequence.

## Mixer Stage.

22. ML13 is an integrated circuit mixer where the 1MHz square wave from TR2 is applied to the carrier input, pin 8, and the 1.013 - 1.020 MHz output from the lower transfer loop oscillator is applied to the signal input, pin 1. The output signal from the mixer, at pin 6, is applied to a low-pass filter, C27, C28, L3, which selects the difference frequency. The filter is followed by a buffer stage, TR19, and an output shaper, G9, which is fed from a voltage regulator consisting of TR20 and a 5.6V zener diode, D3; the square-wave output from G9 is applied to the lower transfer loop phase comparator.

# Lower Transfer Loop Phase Comparator

- 23. The phase comparator consists of a dual D-type flip-flop, ML16, NAND gates, G15, and a voltage contirol circuit, TR21, TR22, TR23. It compares the output signal frequency from the mixer with the output signal frequency from the programmed divider N2; any error between these two frequencies is used to develop a d.c. voltage which is applied to the lower transfer loop oscillator to eliminate the error. The action of the circuit is described below.

- 24. The output signal from the programmed divider, at ML20 pin 3, consists of negative going pulses which are applied to the clock input of ML16b (pin 11). The output signal from the mixer via ML17 pin 6 is applied to the clock input of ML16a (pin 3). The D inputs of ML16, at pins 2 and 12, are both taken to the +5V (logic '1') via R66. Thus when the positive edge from ML20 pin 3 clocks ML16b, the Q output at pin 9 changes to '1' and the Q output at pin 8 changes to '0'. Similarly, when the positive edge from ML17 pin 6 clocks ML16a, the Q output at pin 5 changes to '1' and the Q output at pin 6 changes to '0'. When both Q outputs are at '1' the output from the NAND gate, G15, changes to '0' clearing both flip-flops of ML16 via R74 and thus resets the Q outputs to '0' and the

and the  $\overline{Q}$  outputs to '1'.

- 25. Consider the case where the output frequency from the mixer is high (due to an increase in the frequency of the lower transfer loop oscillator). This will mean that the positive edge from the programmed divider will occur after the positive edge from the mixer. The resulting setting and resetting of the flip-flops causes increased conduction of TR23, due to the Q output waveform from ML16a (see timing diagram, Fig. 2.2) as compared with the conduction of TR21; this causes the voltage at the collector of TR23 to become less positive, thereby reducing the voltage applied to the varactor diode of the lower transfer loop oscillator. This causes a reduction in the oscillator frequency and a corresponding decrease in the output frequency from the mixer.

- 26. If the mixer output frequency is low (due to a decrease in the frequency of the lower transfer loop oscillator), the positive edge from the programmed divider will occur before the edge from the mixer, the Q output waveform from ML16b will cause increased conduction of TR21 and the voltage at the collector of TR23 will become more positive. The increased voltage applied to the varactor diode of the lower transfer loop oscillator causes an increase in the oscillator frequency and a corresponding increase in the output frequency from the mixer.

- 27. When the two signals are equal in frequency and phase the two flip-flops of ML16 are clocked at the same time, the two Q output waveforms are equal and the varactor line voltage remains constant.

# Lower Transfer Loop Out-of-Lock Detector

28. This consists of a bistable latch, G12, G13, and an output buffer, G14. It is fed from the Q outputs of the phase comparator flip-flop, ML16, and produces a steady logic '0' in-lock signal or an alternating '0' - '1' out-of-lock signal at board pin 42. The action of the circuit, which is identical to that of the LF loop lock detector (paragraph 13) is depicted in the timing diagram, Fig. 2.3.

### Adjustments

29. Refer to Chapter 23, paragraphs 16 to 18 for details of adjustments to the Low Frequency Loop Board PM588.

OUT-OF-LOCK: VCO FREQUENCY LOW

NOTE : ONLY RISING CLOCK EDGES ARE SIGNIFICANT.

ONE OUTPUT (Q1 OR Q2) PRODUCES SHORT (50-200nS) PULSES; THE OTHER PRODUCES

LONG PULSES, ACCORDING TO WHICH FREQUENCY IS THE HIGHER.

THE LONG PULSES CANNOT BE DISPLAYED ON AN OSCILLOSCOPE, AS THEY ARE OF VARYING LENTHS.

IN LOCK: VCO FREQUENCY AND REFERENCE EQUAL

NOTE : ONLY RISING CLOCK EDGES ARE SIGNIFICANT. Q1 AND Q2 OUTPUT PULSE LENGTHS ARE OF THE ORDER OF 50 -200 n S  $^{\circ}$

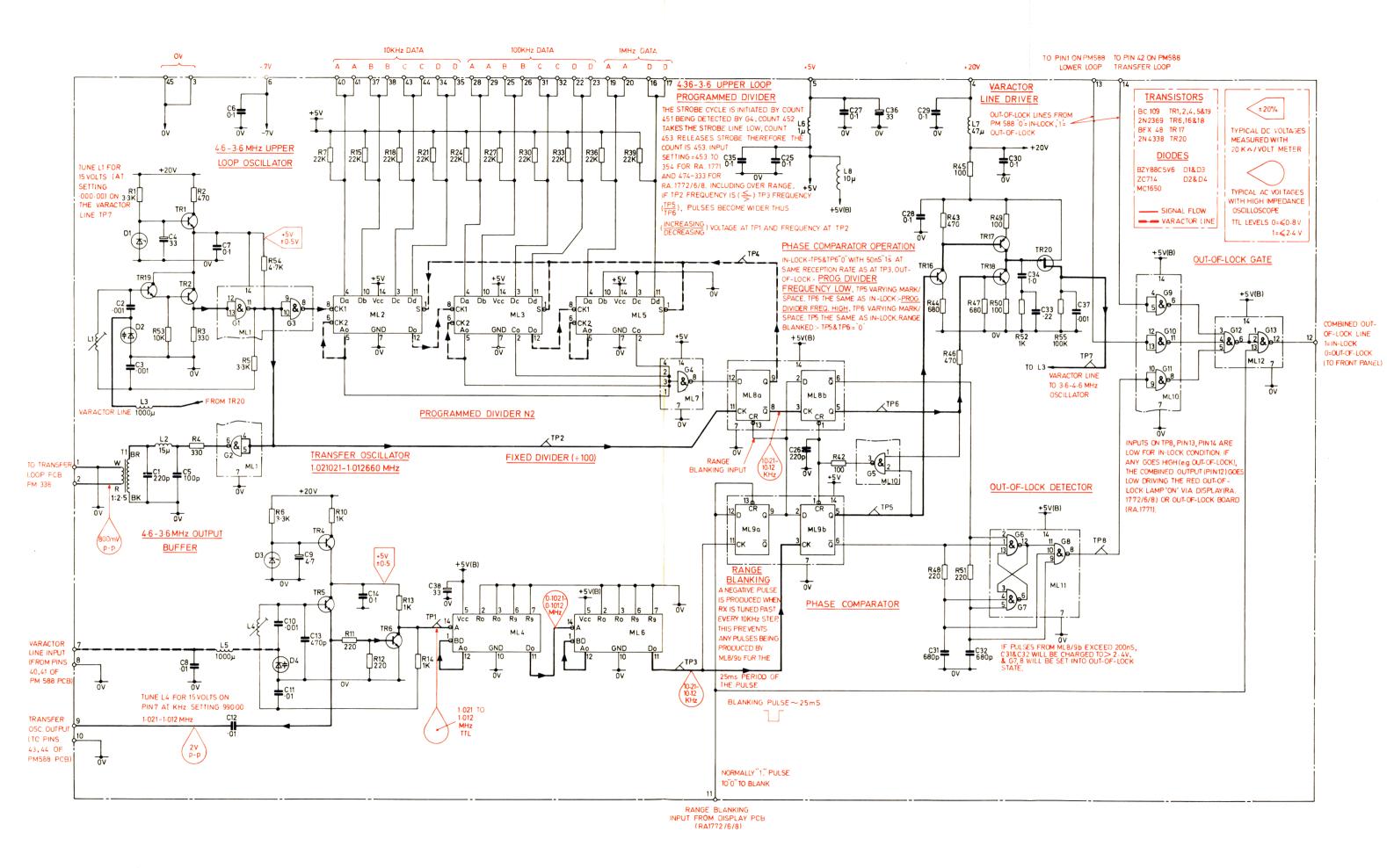

# UPPER LOOP BOARD PM589

# CONTENTS

|                         | Page |

|-------------------------|------|

| INTRODUCTION            | 3-1  |

| Lower Transfer Loop VCO | 3-1  |

| Upper Loop VCO/Shaper   | 3-1  |

| Programmed Divider N2   | 3-1  |

| Range Blanking          | 3-2  |

| Fixed Divider           | 3-3  |

| Phase Comparator        | 3-3  |

| Lock Detector           | 3-4  |

| Lock Indicator          | 3-4  |

| Adjustments             | 3-4  |

# ILLUSTRATIONS

|                                                                | <u>Fig.No.</u> |

|----------------------------------------------------------------|----------------|

| Timing Diagram: Strobe Pulse Generation: Upper Loop            | 3.1            |

| Layout: Upper Loop Board PM589 Circuit: Upper Loop Board PM589 | 3.2<br>3.3     |

# UPPER LOOP BOARD PM589

#### INTRODUCTION

This board contains the upper loop, the lower transfer loop VCO and a lock indicator circuit. A circuit diagram of the board is at the end of this chapter fig.3.3.

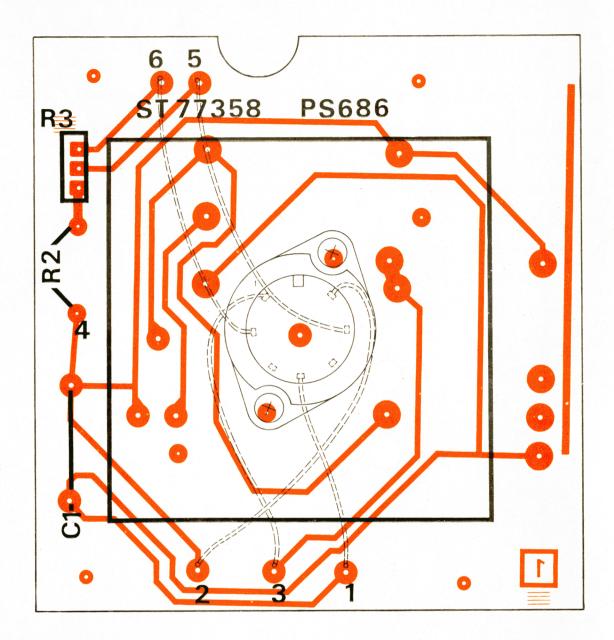

# Lower Transfer Loop VCO

- 2. This voltage controlled oscillator/shaper stage TR5, TR6, produces a squarewave output signal in the frequency range 1.013 to 1.020 MHz. The tuned circuit comprises L4, capacitor C10, C11, C13, and a varactor diode, D4; positive feedback is applied to the tuned circuit via R14. TR4 and 5.6V Zener diode D3 provide supply voltage stabilization.

- 3. The oscillator output signal to the mixer stage of the lower transfer loop (PM588) is taken from the emitter of TR5 and is fed to board pin 8 via C12; the varactor line input, from PM588, is applied to D4 via board pin 7 and inductor L5.

- 4. The lower transfer loop VCO output signal is taken from the collector of TR6 and may be monitored at TP1; it is applied to the lower loop phase comparator via a fixed divider stage ML4, ML6.

# Upper Loop VCO/Shaper

- 5. This VCO/Shaper stage comprises emitter followers, TR19, TR2, inverting NAND gate G1, and a tuned circuit, L1, C2, C3, and varactor diode, D2. Supply voltage stabilization is provided by TR1 and 5.6V Zener diode, D1. The oscillator output signal, in the frequency range 4.6 to 3.6MHz, is applied to the following:-

- (1) The upper transfer loop board (PS338) via a NAND gate, G2, a filter R4, L2, C5, a tuned circuit, T1, C1, and board pins 1 and 2.

- (2) The programmed divider, N2, of the upper loop via a NAND gate G3.

- (3) ML8a (Pin 11), which forms part of the strobe pulse generator for the programmed divider, N2.

# Programmed Divider N2. (See Fig. 1.2)

6. The upper loop programmed divider, which has the same division ratio, N2, as that of the lower transfer loop, consists of three presettable decade counters, ML2, ML3, ML5, NAND gate, G4, and a D-type flip-flop, ML8a.

- 7. The decade counters have strobed parallel entry capability such that the starting point of a count sequence may be preset. A 'l' or a 'O' at a data input (Da, Db, Dc, Dd) is transferred to the associated output (Ao, Bo, Co, Do) when the strobe (S) input is at 'O'. The counting operation is performed on the negative-going edge of the input clock pulse.

- 8. The division ratio of the divider is controlled by the 10kHz and 100kHz digits of the selected operating frequency. The division ratio is given by the expression N2 = 453 minus selected digits, i.e. the division ratio is 453 for a setting of 00 and is 354 from a setting of 99. The operation of the divider is described below.

- 9. BCD frequency setting information is applied to the data inputs of ML2 (10kHz) and ML3 (100kHz). The data inputs to ML5 are all at 0V (logic 'O') and under this condition ML5 starts counting at zero.

- 10. To start a counting sequence, assume that a logic 'O' strobe pulse is applied to the strobe (S) input of each decade counter. As described in paragraph 8 this causes the logic level applied to each data input line (Da, Db, Dc, Dd) to be transferred to the corresponding output line (Ao, Bo, Co, Do). The negative-going edge of the clock pulse (the 4.6 - 3.6MHz VCO output via G3) is applied to the clock 1 input of ML2 and each clock pulse is counted until a count of 451 is reached, i.e. until the Co output from ML5 is at '1', the Ao and Co outputs from ML3 are at '1', and the Ao output from ML2 is at '1'. Thus when a count of 451 is reached, the four input lines to NAND gate G4 are at logic 'l', and the output from G4, which is applied to the D input of flip-flop ML8a (pin 12), changes to 'O'. The next clock pulse to arrive at ML8 pin 11 transfers the logic 'O' at ML8 pin 12 to the Q output at pin 9, and this is applied as the strobe pulse to the three decade counters. The four input lines to the NAND gate, G4, are now no longer at logic '11' and the D input of ML8a, changes to '11'. The next clock pulse to arrive at ML8 pin 11 transfers the logic '1' at ML8 pin 12 to the Q output at pin 9, the 'O' strobe pulse is removed, and the counter is ready to start the next count sequence. Thus two clock pulses are used to generate the strobe pulse, making a total count of 453, i.e. 451 + 2.

### Range Blanking

- 11. The range blanking input, at board pin 11 is used to momentarily inhibit the two inputs to the upper loop phase comparator when, during receiver tuning, a 0-to-1 or a 1-to-0 transition of the 10kHz digit occurs. This allows the LF and lower transfer loop outputs to run up or down to the new frequency whilst the 3.6 to 4.6MHz VCO is prevented from changing frequency.

- 12. The range blanking input line, which is normally at approximately +5V (logic '1'), is connected to the D (pin 12) and clear (pin 13) inputs of a D-type flip-flop, ML9a. This provides the required logic '1' to the D inputs of the phase comparator, ML8b, ML9b. The logic 'O' 25 millisecond range blanking pulse, from the display board, clears ML9a and forces the Q output, at ML9 pin 9, to 'O'. This is applied to the D inputs of the phase comparator and also to the clear input of the strobe pulse generator flip-flop, ML8a. Thus a 25 millisecond strobe pulse, from ML8 pin 9, is applied to the programmed divider, N2, and the output is inhibited.

#### Fixed Divider

13. The fixed divider consists of two decade counters, ML4, ML6, connected in cascade. The lower transfer VCO output signal is applied to the A input of ML4 and the divide-by-100 output is taken from ML6 pin 11; this is applied as the clock input to the phase comparator (ML9b pin 3) and may be monitored at TP3.

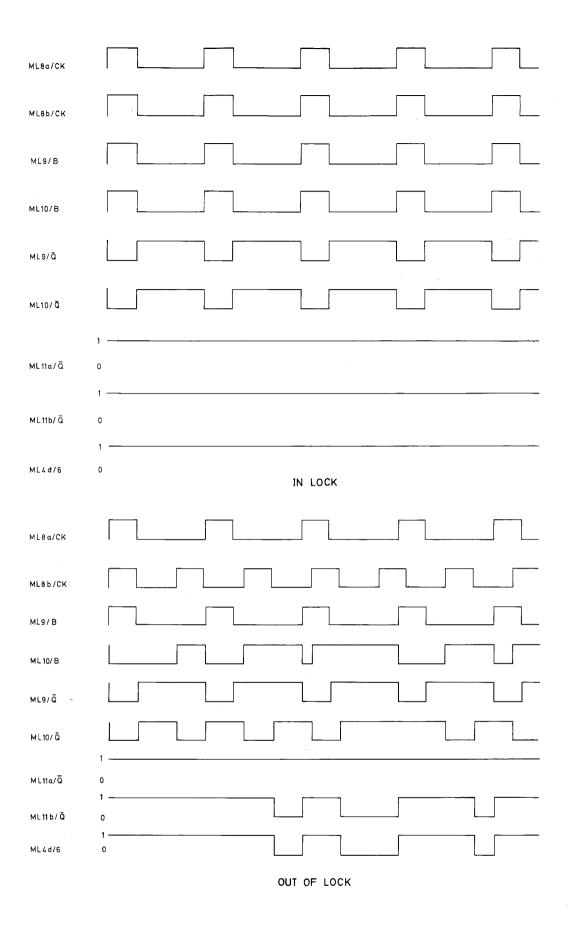

## Phase Comparator

- 14. The phase comparator consists of two D-type flip-flops, ML8b, ML9b, NAND gate, G5, and a voltage control circuit, TR16, TR17, TR18. It compares the output signal frequency from the programmed divider with the output signal frequency from the fixed divider; any error between these two frequencies is used to develop a d.c. voltage which is applied to the 3.6 to 4.6 MHz VCO to eliminate the error. The action of the circuit is as follows:-

- 15. The output from the programmed divider, at ML8 pin 8, consists of positive-going pulses which are applied to the clock input of ML8b (pin 3). The output from the fixed divider, at ML6 pin 11, also consists of positive going pulses and these are applied to the clock input of ML9b (pin 3). The D inputs of both ML8b and ML9b are at logic '1' (see paragraph 12). Thus when the positive edge from ML8a pin 8 clocks ML8b, the Q output at pin 5 changes to '1' and the Q at pin 6 changes to 'O'. Similarly, when the positive edge from ML6 pin 11 clocks ML9b, the Q output at pin 5 changes to '1' and the Q output at pin 5 changes to '1' and the Q output at pin 6 changes to 'O'. When both Q outputs are at '1', the output from the NAND gate, G5, changes to '0', clearing both ML8b and ML9b; thus the Q outputs are reset to '0' and the Q outputs are reset to '1'.

- 16. Consider the case where the frequency from the programmed divider is high. This will mean that the positive edge from ML8a pin 8 will occur before the positive edge from ML6 pin 11. The resultant setting and resetting of the flip-flop causes increased conduction of TR18, due to the Q output waveform from ML8b (see Q1 on Timing Diagram Fig. 2.2), as compared with the conduction of TR16; this causes the voltage at the collector of TR18 to become less positive, thereby causing a reduction in the voltage applied to the varactor diode, D2, of the 3.6 to 4.6MHz VCO, and a corresponding reduction in the VCO frequency.

- 17. If the output frequency from the programmed divider is low, the positive edge from ML8a pin 8 will occur after the positive edge from ML6 pin 11, the Q output waveform from ML9b pin 5 will cause increased conduction of TR16 and the voltage at the collector of TR18 will become more positive. The resultant increase in the voltage applied to the varactor diode, D2, causes a corresponding increase in the VCO frequency thus correcting the error.

- 18. When the two signals are equal in frequency and phase the two comparator flipflops are clocked at the same time, the two Q output waveforms are equal and the varactor line voltage remains constant.

Timing Diagram: Strobe Pulse Generation

Upper Loop PM 589

Fig. 3.1

### Lock Detector

19. This consists of a bistable latch, G6, G7 and an output buffer, G8. It is fed from the Q outputs of the phase comparator flip-flops, ML8b, ML9b, and produces a steady '0' in-lock signal, or an alternating '0' - '1' out-of-lock signal, at ML11 pin 8. The action of the circuit, which is identical to that of the LF Loop lock detector (Chapter 2, paragraph 15), is depicted in the Timing Diagram, Chapter 2, Fig. 2.3.

# Lock Indicator

20. The lock indicator consists of five NAND gates, G9 to G13 inclusive. The lock detector outputs from the LF and lower transfer loops are applied to G10 and G9 via board pins 13 and 14 respectively, whilst the upper loop lock detector output, at ML11 pin 8, is applied to G11. The output from G13 ('1' for in-lock, '0' for out-of-lock) is applied to a diode OR gate and the out-of-lock indicator lamp driver on the display board.

# Adjustments

21. Refer to Chapter 23, paragraphs 19 to 21, for details of adjustments to the Upper Loop Board PM589.

3-4

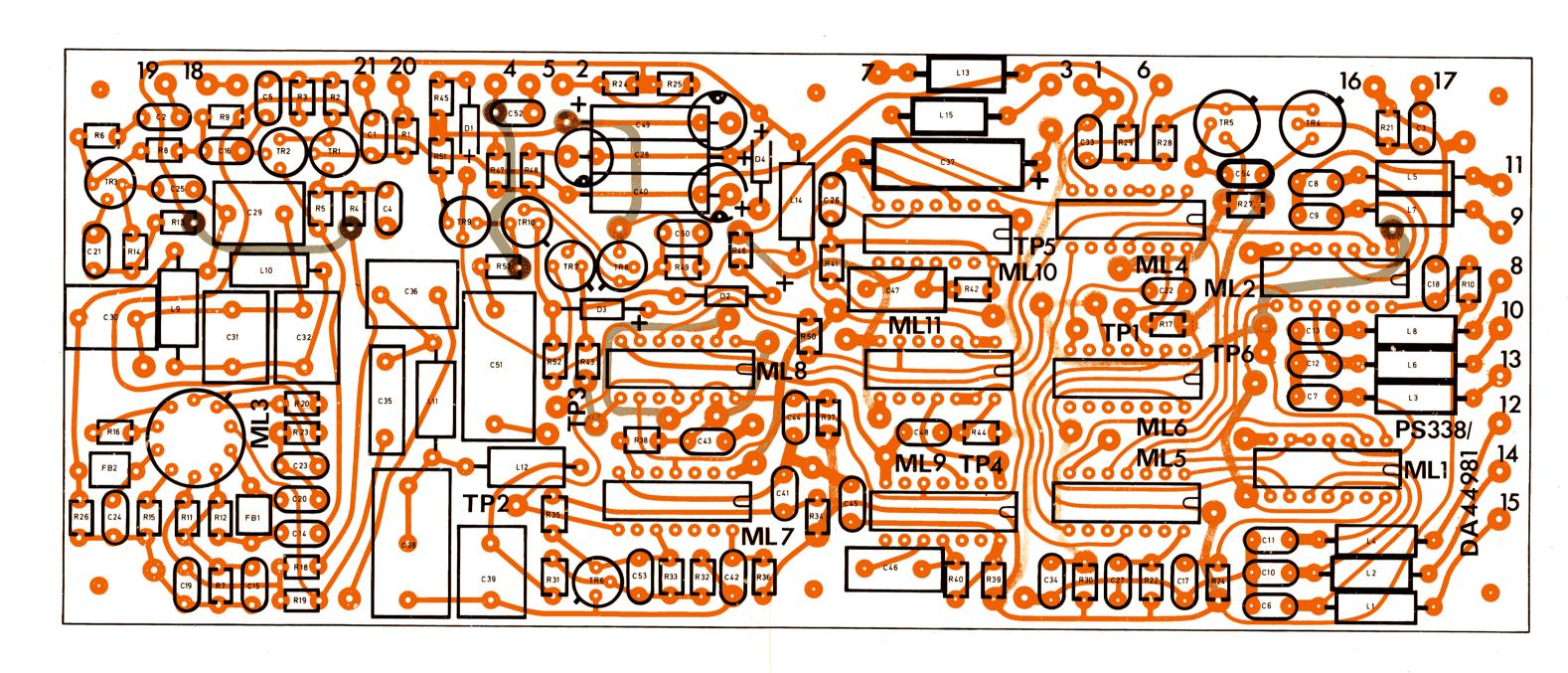

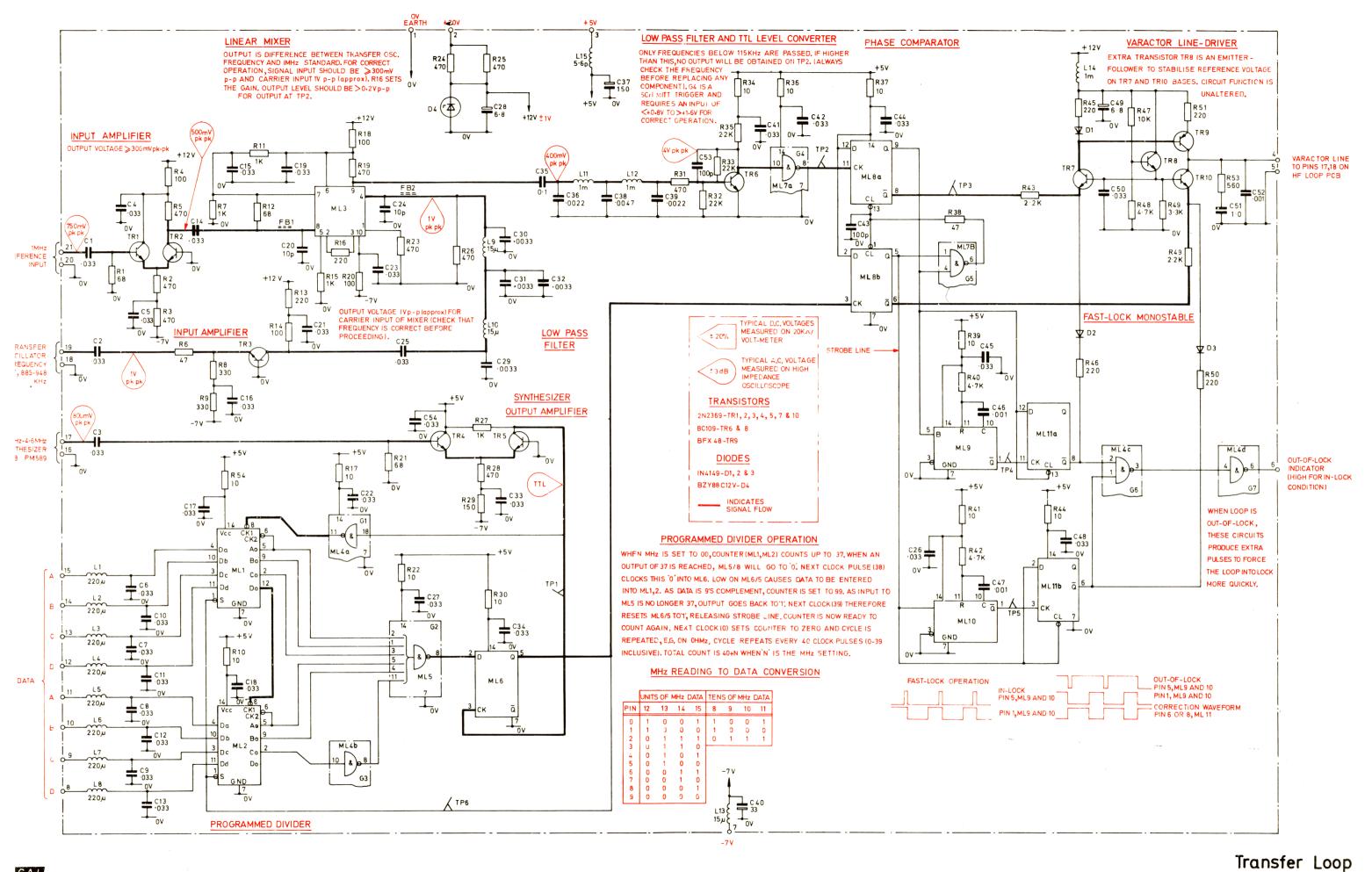

# TRANSFER LOOP BOARD PS338

# CONTENTS

| INTRODUCTION                                                                                                                                   | 4-1                      |

|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Programmed Divider N3<br>Mixer<br>Phase Comparator<br>Lock Indicator and Fast Lock Circuit                                                     | 4-1<br>4-2<br>4-2<br>4-4 |

| ILLUSTRATIONS                                                                                                                                  |                          |

|                                                                                                                                                | Fig.No                   |

| Timing Diagram: Fast Lock and Indicator: Upper Transfer Loop PS338<br>Layout: Transfer Loop Board PS338<br>Circuit: Transfer Loop Board PS 338 | 4.1<br>4.2<br>4.3        |

| TABLES                                                                                                                                         | Page                     |

|                                                                                                                                                | <u>i uge</u>             |

| Table 1: Code Conversion Table 2: Programmed Divider Operation (PS338)                                                                         | 4-4<br>4-4               |

Page

# TRANSFER LOOP BOARD PS338

#### INTRODUCTION

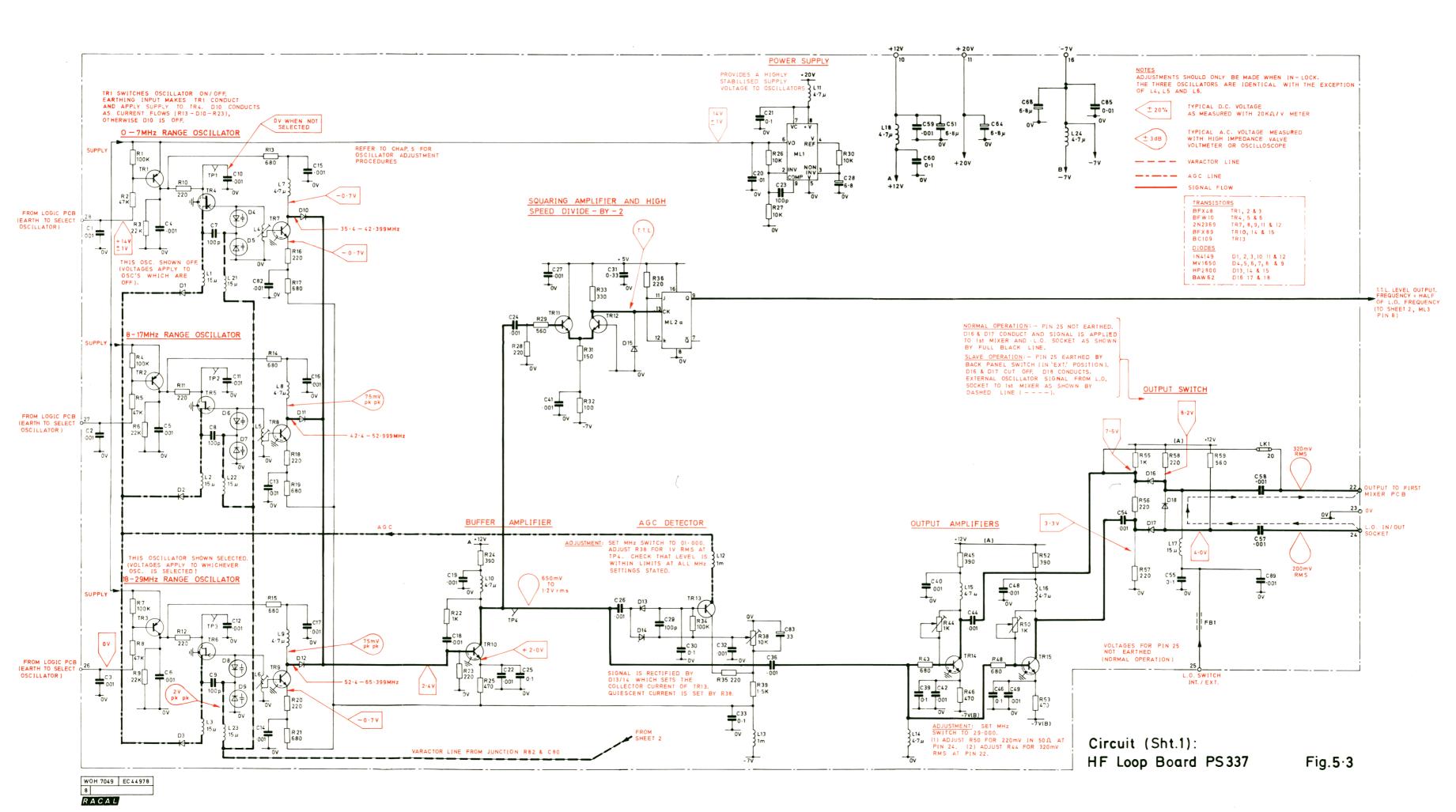

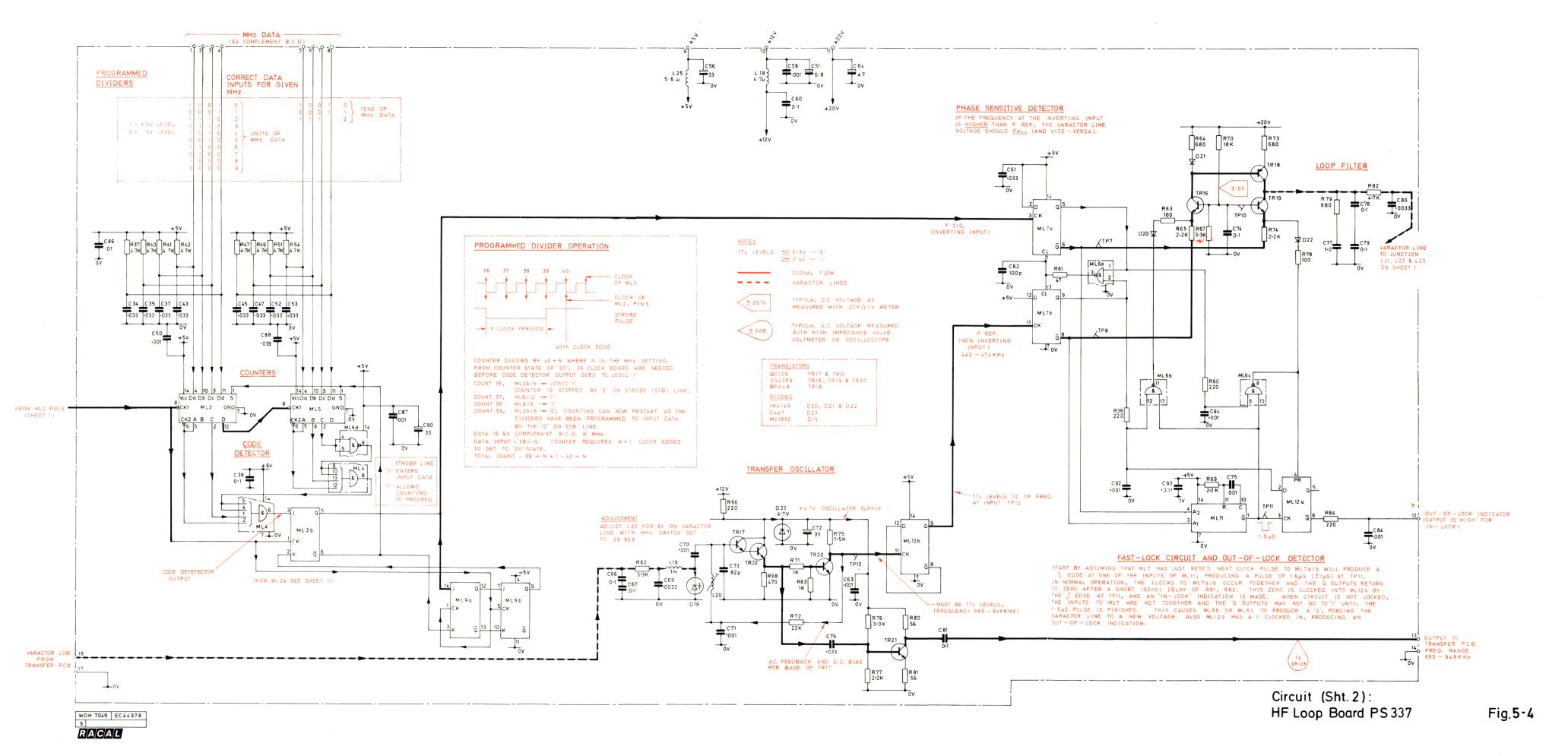

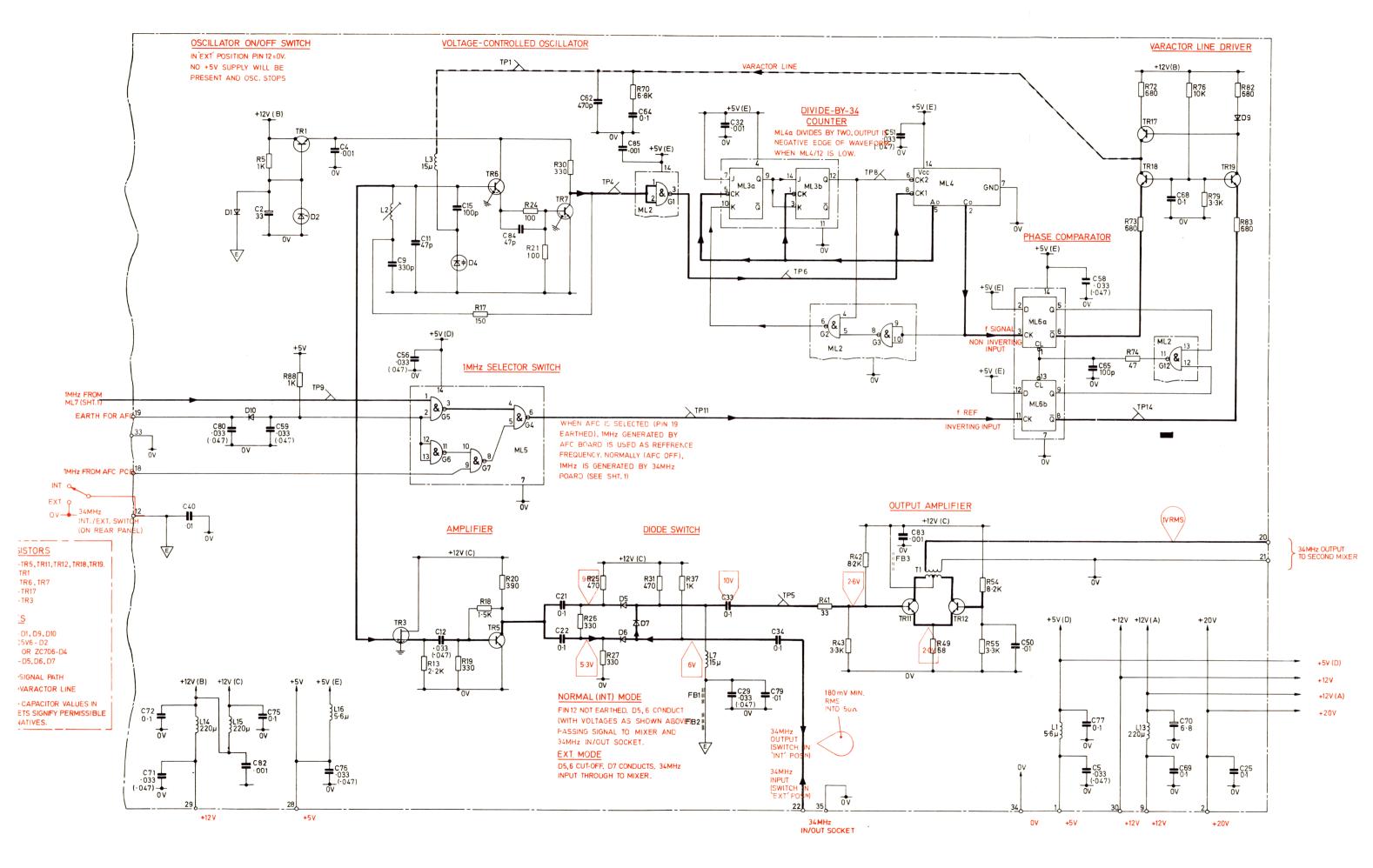

- 1. The transfer loop board contains the upper transfer loop (with the exception of the upper transfer loop oscillator which is located on the HF loop board PS337), programmed divider N3 and lock indicator circuits. This board, together with HF loop board, generates the 35.4 to 65.4 MHz local oscillator injection frequency for the first mixer. A circuit diagram of the board is given at the end of the chapter fig. 4.3.

- 2. The 4.6 to 3.6MHz output signal from upper loop, at board pin 17, is coupled by C3 to a shaper stage, TR4, TR5. The squarewave output is inverted by ML4a and is then applied to a programmed divider consisting of two presettable decade counters ML1, ML2, and inverter, ML4b, a six-input NAND gate, ML5 and a D-type flip-flop, ML6.

## Programmed Divider N3 (See Fig. 1.2)

- 3. The two decade counters, ML1, ML2, have strobed parallel-entry capability so that the starting point of a count sequence may be preset. A '1' or a '0' at a data input (Da, Db, Dc, Dd) is transferred to the associated output (Ao, Bo, Co, Do) when the strobe (S) input is at '0'. The counting operation is performed on the negative-going edge of the input clock pulse.

- 4. The division ratio of the programmed divider, which is controlled by the 10MHz and MHz lines, is given by the expression N3 = 40+ selected MHz digits, i.e. when 00MHz is selected, the division ratio is 40, and when 29 MHz is selected, the division ratio is 69. The operation of the divider is described below.

- 5. Information from the memory board is applied to the decoding board where it is converted into a BCD nines complement code (see Table 1). The nines complement coded outputs are applied to the data inputs of the two decade counters 'units' to ML1 and 'tens' to ML2, and control the starting point of a count sequence.

- 6. To start the counting sequence, assume that a logic '0' strobe pulse is applied to the strobe (S) inputs of both ML1 and ML2 (at pin 1). As described in paragraph 3 this causes the logic level applied to each input line (Da, Db, Dc, Dd) to be transferred to the corresponding output line (Ao, Bo, Co, Do). The negative going edge of the clock pulse (from the shaper stage, TR4, TR5 and the inverter ML4a) is now applied to the clock 1 input of ML1 at pin 8. Each clock pulse is now counted until a count of 37 is reached, i.e. until the Ao, Bo and Co outputs from ML1 and the Ao and Bo outputs from ML2 are all at logic '1'. (The C output from ML2 is applied to an inverter, ML4b, to inhibit binary 7).

- 7. When a count of 37 is reached, the input lines to the NAND gate, ML5, are all at logic '1' and the '0' output, at ML5 pin 8, is applied to the D input of flip-flop ML6. The next clock pulse, which is applied to pin 3 of ML6, transfers the '0' at ML6 pin 2 to the Q output, at ML6 pin 5, and this is applied as the next strobe pulse to the two decade counters, ML1 and ML2, ready for the next count. The output from ML5 changes to logic '1' and the next clock pulse applied to ML6 causes the Q output to change to logic '1'; this output is applied to the phase comparator, ML8.

- 8. Table 2 shows the operation of the divider for various settings of the MHz digits.

#### Mixer

9. ML3 is an integrated circuit mixer; the 1MHz reference frequency signal, shaped by TR1, TR2, is applied to pin 8 and the 885-948kHz transfer loop oscillator output signal, from the HF loop board, buffered by TR3, is applied to pin 4 via a low-pass filter, L9, L10, C29 to C32. The difference frequency output from the mixer, 115kHz to 52kHz, is coupled to a low-pass filter, L11, L12, C36, C38, C39, and is then applied to a shaper stage, TR6. The squarewave output from TR6 is applied to the phase comparator, ML8 via a buffer, ML7a.

### Phase Comparator

- 10. The phase comparator consists of a dual D-type flip-flop, ML8, a two-input NAND gate ML7b and a voltage control circuit, TR7, TR8, TR9, TR10. It compares the output signal frequency from the programmed divider with the output signal frequency from the mixer; any error between these two frequencies is used to develop a d.c. voltage, which is applied to the transfer loop oscillator (on the HF loop board) to eliminate the error. The action of the circuit is as follows.

- 11. The output from the programmed divider, at ML6 pin 5, consists of negative-going pulses; these are applied to the clock input of ML8b. The output from the mixer (via the low-pass filter, shaper and buffer), at ML7a pin 8, is applied to the clock input of ML8a. The D inputs to both ML8a and ML8b are taken to the +5V rail (logic '1'). Thus when the positive edge from ML6 pin 5 clocks ML8b, the Q2 output at pin 5 changes to '1' and the Q2 output changes to '0'. Similarly, when the positive edge from ML7a pin 8 clocks ML8a, the Q1 output changes to '1' and the Q1 output changes to '0'. When both Q outputs are at '1', the output from the NAND gate, ML7b, changes to '0' clearing both ML8 flip-flops via R38 and thus resetting the Q outputs to '0' and the Q outputs to '1'.